RXD-DV9

7

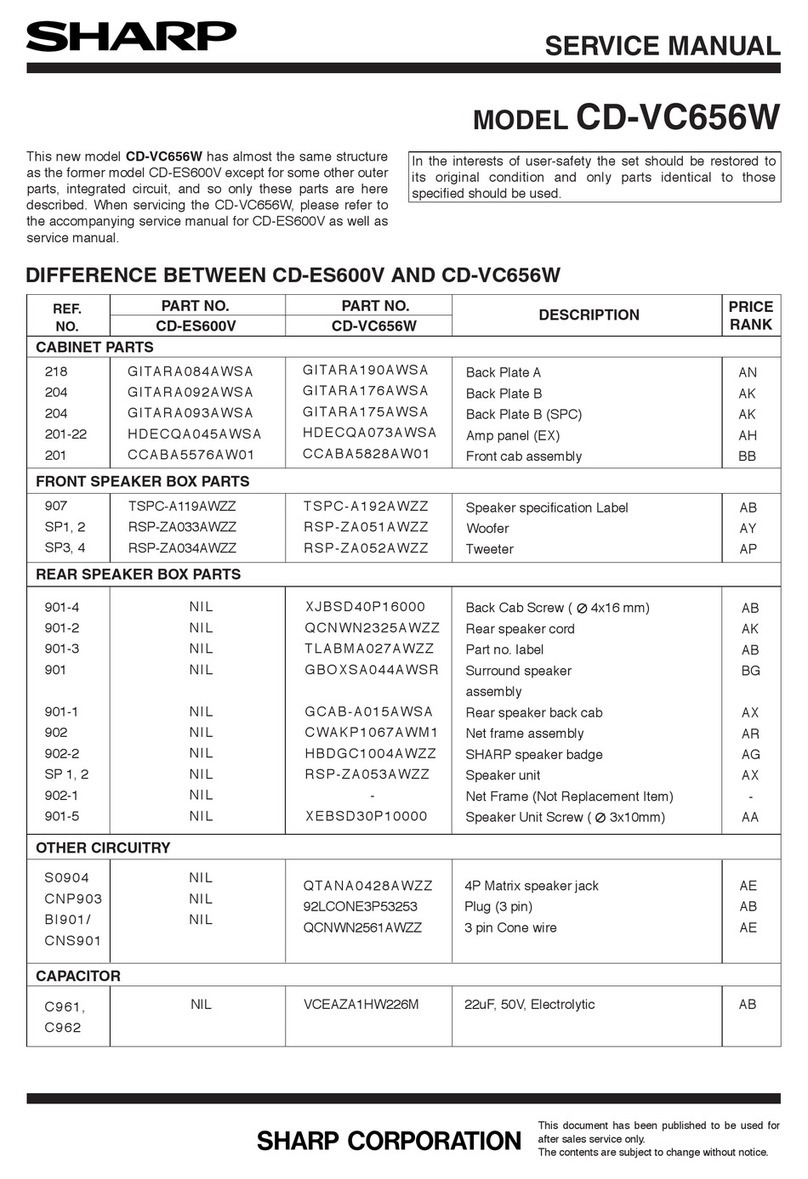

Pin No. Pin Name I/O Description

33 FE O FE AMP output terminal.

34 FEN I Input terminal for selecting FE AMP gain.

35 TEN I Input terminal for selecting TE AMP gain.

36 TE O TE AMP output terminal.

37 PDLIMTRES - Bias resistance terminal for PDLIMIT.

38 ABCDN I ABCD AMP for selecting gain (-) input terminal.

39 ABCD O ABCD AMP output terminal.

40 ABCDI I ABCD AC coupling input terminal for servo monitor.

41 ENVP - CAP connection terminal for selecting the RC value of peak hold

for detecting RF envelopes.

42 ENVB - CAP connection terminal for selecting the RC value of bottom

hold for detecting RF envelopes.

43 ENV O RF envelope detect output terminal.

44 DGND - Power ground input terminal for digital circuits.

45 FOKTH I Focus OK comparating level input terminal.

46 FOKB O Focus OK comparator output terminal( L: Focus OK).

47 DFCT CP1 - Connction terminal for RC value of peak hold, for selecting the

maximum time for servo signal.

48 DFCT CP2 - Connction terminal for RC value of peak hold, for selecting the

minimum defect time for PLL.

49 CC1 O Peak hold output terminal for selecting the minimum defect time for defect.

50 CC2 I Peak hold AC coupling input terminal for defect.

51 DVCC - Power voltage input terminal for digital circuit.

52 DFCTTH2 - Resistance connction terminal for selecting the defect

comparating level for PLL.

53 DFCTTH1 - Resistance connction terminal for selecting the defect

comparating level for servo.

54 DFCT1 O Defect output terminal for servo.

55 DFCT2 O Defect output terminal for PLL.

56 DPDVCC - Power voltage input terminal for DPD TE.

57 MIRR O Mirror output terminal.

58 BCA O BCA output terminal.

59 TE3OFST - CAP connection terminal(open) for 3B TE offset.

60 DPDEQ1 O DPD EQ(A+C) output terminal.

61 DPDEQ2 O DPD EQ(B+D) output terminal.

62 FAULTOUT O DPD abnormal wave from output terminal(monitor).

63 DPDMUTE I DPD TE mute control terminal(H: Mute).

64 PLLCTL I DPD TE PLL variable input terminal.

65 TE1RES I DPD TE PLL variable bias resistance.

66 DPDGND - Power ground input terminal for DPD TE.

67 VREFDPD O CAP connection terminal for DPD TE center voltage.

68 RREFDLY - Bias resistance connection terminal for delay block.

69 DATA I Data input terminal.

70 CLOCK I Clock input terminal.

71 STB I Data enable input terminal.

72 OSC - Input terminal for RC value of OSC,for auto offset block.

73 RESET I Reset input terminal (L: Reset)for auto offset block.

74 BCAI I BCA filter 1.

75 BCAO O BCA filter 2.

76 RFCT O RF ripple center voltage output terminal for mirror.

77 CB2 - CAP connection terminal of RC value of bottom hold, for RFCT generation.

78 CP2 - CAP connection terminal of RC value of peak hold, for RFCT generation.

79 RFRP O RF ripple AMP output terminal for mirror.

80 RFRPN I Input terminal for selecting RFRP APM gain.

81 MROOFST I RF ripple offset control terminal for mirror.

82 CB1 - RC connection terminal of RC value of bottom hold, for RFRP generation.

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299