10

J-Link / J-Trace (UM08001) © 2004-2009 SEGGER Microcontroller GmbH & Co. KG

EMBEDDED SOFTWARE

(Middleware)

emWin

Graphics software and GUI

emWin is designed to provide an effi-

cient, processor- and display control-

ler-independent graphical user

interface (GUI) for any application that

operates with a graphical display.

Starterkits, eval- and trial-versions are

available.

embOS

Real Time Operating System

embOS is an RTOS designed to offer

the benefits of a complete multitasking

system for hard real time applications

with minimal resources. The profiling

PC tool embOSView is included.

emFile

File system

emFile is an embedded file system with

FAT12, FAT16 and FAT32 support.

emFile has been optimized for mini-

mum memory consumption in RAM and

ROM while maintaining high speed.

Various Device drivers, e.g. for NAND

and NOR flashes, SD/MMC and Com-

pactFlash cards, are available.

emUSB

USB device stack

A USB stack designed to work on any

embedded system with a USB client

controller. Bulk communication and

most standard device classes are sup-

ported.

SEGGER TOOLS

Flasher

Flash programmer

Flash Programming tool primarily for microcon-

trollers.

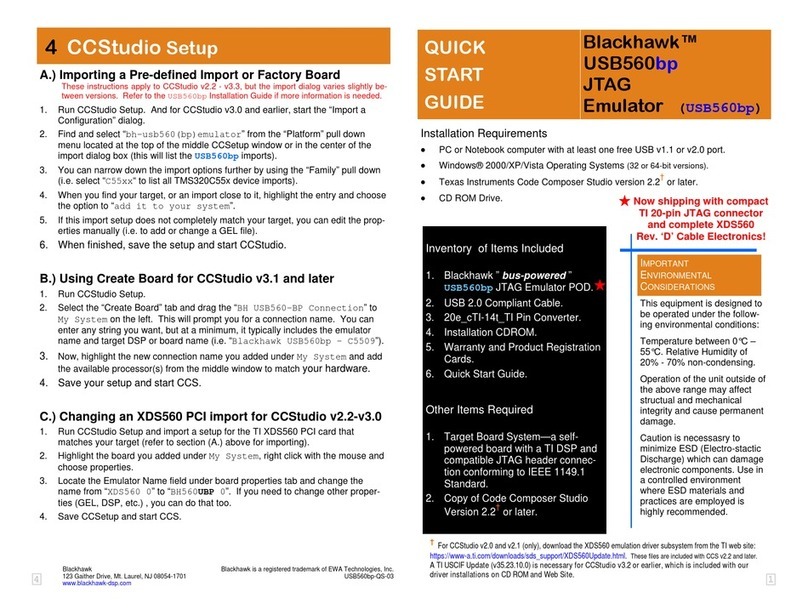

J-Link

JTAG emulator for ARM cores

USB driven JTAG interface for ARM cores.

J-Trace

JTAG emulator with trace

USB driven JTAG interface for ARM cores with

Trace memory. supporting the ARM ETM (Embed-

ded Trace Macrocell).

J-Link / J-Trace Related Software

Add-on software to be used with SEGGER’s indus-

try standard JTAG emulator, this includes flash

programming software and flash breakpoints.

SEGGER Microcontroller GmbH & Co. KG develops

and distributes software development tools and ANSI

C software components (middleware) for embedded

systems in several industries such as telecom, medi-

cal technology, consumer electronics, automotive

industry and industrial automation.

SEGGER’s intention is to cut software development-

time for embedded applications by offering compact flexible and easy to use middleware,

allowing developers to concentrate on their application.

Our most popular products are emWin, a universal graphic software package for embed-

ded applications, and embOS, a small yet efficient real-time kernel. emWin, written

entirely in ANSI C, can easily be used on any CPU and most any display. It is comple-

mented by the available PC tools: Bitmap Converter, Font Converter, Simulator and

Viewer. embOS supports most 8/16/32-bit CPUs. Its small memory footprint makes it

suitable for single-chip applications.

Apart from its main focus on software tools, SEGGER develops and produces programming

tools for flash microcontrollers, as well as J-Link, a JTAG emulator to assist in develop-

ment, debugging and production, which has rapidly become the industry standard for

debug access to ARM cores.

Corporate Office:

http://www.segger.com

United States Office:

http://www.segger-us.com