SEGA ENTERPRISES GENESIS 32X User manual

ll(liA\\"

SERVICE

MANUAL

GENESIS

32X(VAO,VA1)

I

MEGA

DRIVE

32X

NO. 012

ISSUED JUNE, 1995

CONTENTS

1.

SPECIFICATIONS · · · · · · · · · · :· · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · 2

2.

IDENTIFYING PARTS · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · 3

3.

ACCESSORIES· · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · 3

4.

DISASSEMBLY·· ·

·······································

· · 4

5. ADJUSTMENT · · ·

~

· · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · 5

6.

BLOCK DIAGRAM · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · 7

7.

SCHEMATIC & CIRCUIT BOARD DIAGRAMS · · · · · · · · · · · · · · · · 9

8.

PARTS

SPECIFICATIONS··································

19

9.

EXPLODED VIEW & PARTS

LIST··························

34

9-1. Exploded View · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · 34

9-2. Mechanical Parts List · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · ·

35

9-3. Electrical Parts List · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · ·

35

9-4. Accessories/Package List · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · ·

38

Sega Enterprises, Ltd.

BEFORE REFERRING TO THE SERVICE

MANUAL

Since

the

circuit of

the

Extension Unit

used

in

the

GENESIS

32X

has

been integrated

on

the

main

circuit board, an Extension

Unit

is

not

necessary for

the

GENESIS

32X(V

Al).

This circuit

is

built

into

the

MEGA

DRIVE

32X

from

the

first

unit.

1. SPECIFICATIONS

Ratings

MEGA DRIVE 32X

Model GENESIS32X PAL

PALG/I

Power input

Input:

AC120

V,

60

Hz

Input:

AC230

V,

50 Hz

Input:

AC240

V,

50

Hz

Output:

DCIO

V,

850

mA

Output:

DCIO

V,

850

mA

Output:

DC9

V,

850

mA

Power consumption

Approx.

4 W Approx. 4 W Approx. 4 W

Operating

environment Temperature: 5

"C

-35

"C

Humidity:

20%RH-80%RH (no condensation)

Dimensions l

15(W)

x 210(L) x

IOO(H)

mm

Specifications

Master 32bit

RISC

SH2

23

MHz

20MIPS

CPU

Srave 32bit

RISC

SH2 23

MHz

20MIPS

RAM

2Mbit

(SDRAM)

Memories

VRAM

2Mbit ..

·-

Sound

PWM

Sound Source (Stereo)

VDP

SEGA

custom

LSI

Display

TV

Display

capability Color 32,768 colors

VIDEO

Video

Output

RF

RGB

Slots Cartridge slots

-2-

2. IDENTIFYING PARTS

Front View

3. ACCESSORIES

Connector Cable

Spacer

for

GENESIS

II

/MEGA DRIVE

II

RF

Unit

Cartridge Slot

(PALversion except

for

France)

Rear View

Conversion Cable

AC Adaptor

Mono Cable Scart

(France only)

-3-

AN

IN Jack AC AdaptorJack

AudioNideo Cable (Mono)

Electromagnetic Shield Plates

Extension Unit

(Only

GENESIS 32X

VAO)

4. DISASSEMBLY

4-1. Top Case Removal (See Fig. 4-1)

I)

Remove

four screws®

and

the

top

case.

Flg.4-1

4-2. Sub Board Removal

(See Fig. 4-2)

/Top

case

I)

Remove

ten

screws @

attached

the

top

shield case.

2)

Remove

two

screws ©

attached

the

64-pin

connector.

3)

Remove

two

40-pin flat cables

on

the

sub

board

.

4)

Remove

the

sub

board

showned

as

arrow

.

Flg.4-2

4-3. Main Board Removal

(See Fig. 4-3, 4-4)

-4-

I)

Remove

four screws @ attached the front case

and

rear case

on

the

bottom

case

and

then

their

showned

as arrow.

2)

Remove

two

screws ®attached the

front

case

and

rear case

and

main

board

.

Rear Case

Flg.4-3

Flg.4-4

·.

5.

ADJUSTMENT

Video Frequency Matching Adjustment

Test equipment and

tools

for

adjustment

l.

Regulated power supply

(SV

DC)

2.

Frequency counter (capable of

displaying

7 digits or

more)

3.

10:

I oscilloscope

probe

4.

Philips screwdriver

5.

Non-metal

adjustment driver

6.

AC

adaptor excusively for super

32X

7.

One

lead

for

GND

and

two

leads

for

SV

Connections

of

test

equipment

Regulated power supply

1~10

1~1°

GND

V 0

AC adaptor excusively

for super 32X

To AC outlet

Frequency counter

13.5795456MHzl

To DC Jack Connectto

10:1

probe to IC12 pin 20

Connectto

GND Pattern

Adlustment procedure

l. Disconnect the super

32X

from

the

Mega

Drive.

Connect

to

IC12 pin

31

Sub Board

2.

Remove

the top case

and

top shield case

from

the

super

32X.

3.

Plug

the

AC

adaptor

into

an

AC

outlet

and

into

the

DC

jack.

4.

Set the regulated powersupply

to

5V

DC

and

connect

it

to

1Cl4

pin

l.

(The super

32X

turns on.)

5.

Connect

SY

DC

to

ICI2

pin

31.

(Set to the test

mode.)

32

31

20 17

~

1 16

6.

Connect

the

frequency counter

to

ICI2

pin

20

and

adjust

C72

so

the

frequency

is

3.579545

MHz±

lOHz.

-5-

MEMO

-

--

·

--

- -- - ·

··

- -·-- ·-

--·

- ·-

-·

·-

--

- -

----

-

--------

-

----

-- - --

--·

--

-··

-

-·-·

··-

-· -

-6-

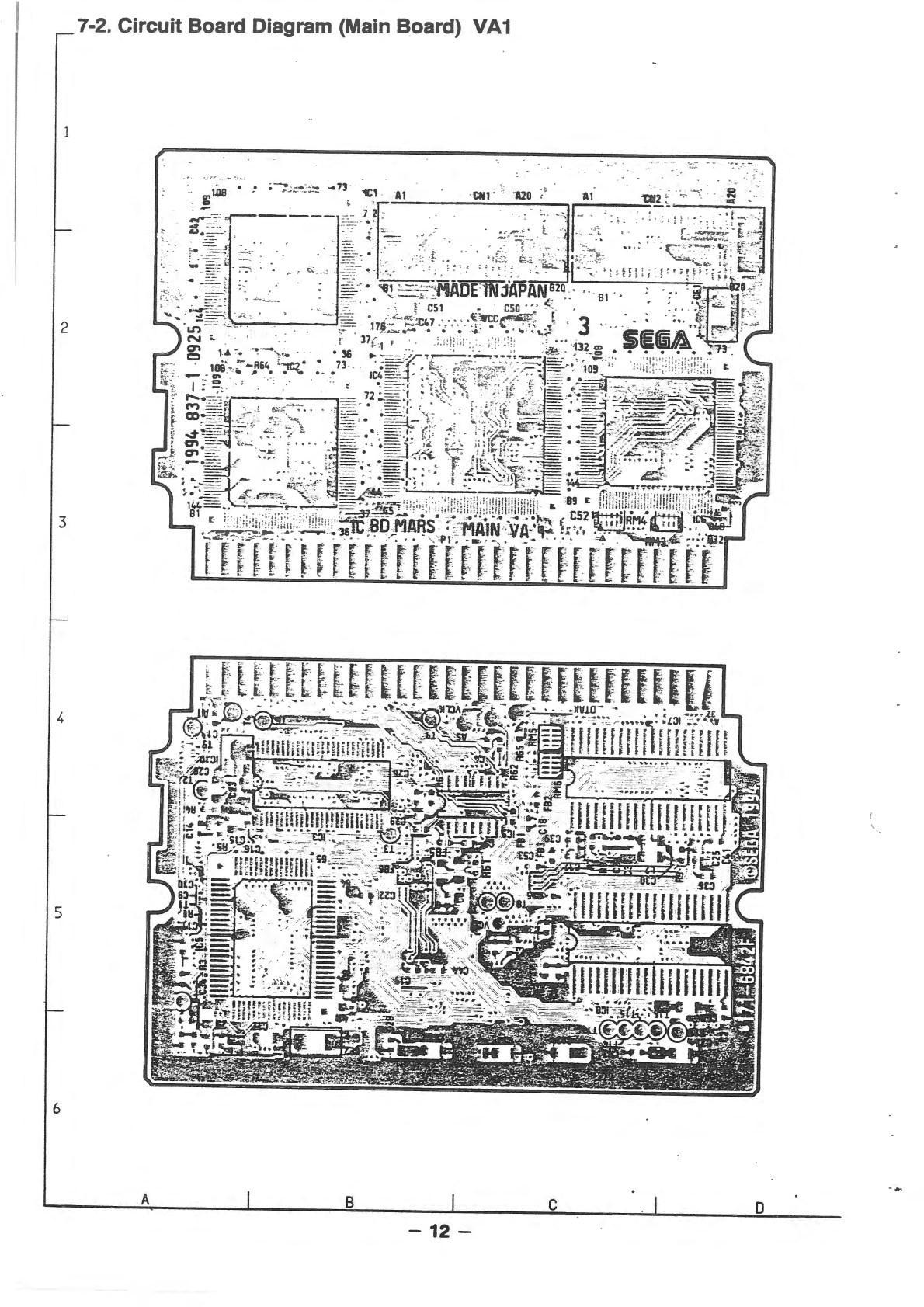

7-2.

Circuit

Board Diagram (Main Board)

VAO

..

2

3

4

5

6

A B c 0

-11 -

7-2.

Circuit

Board Diagram (Main Board) VA1

. ~ -·-

..

..

..

··-

...

..·.-..

2

3

4

5

6

A B c D

-

12

-

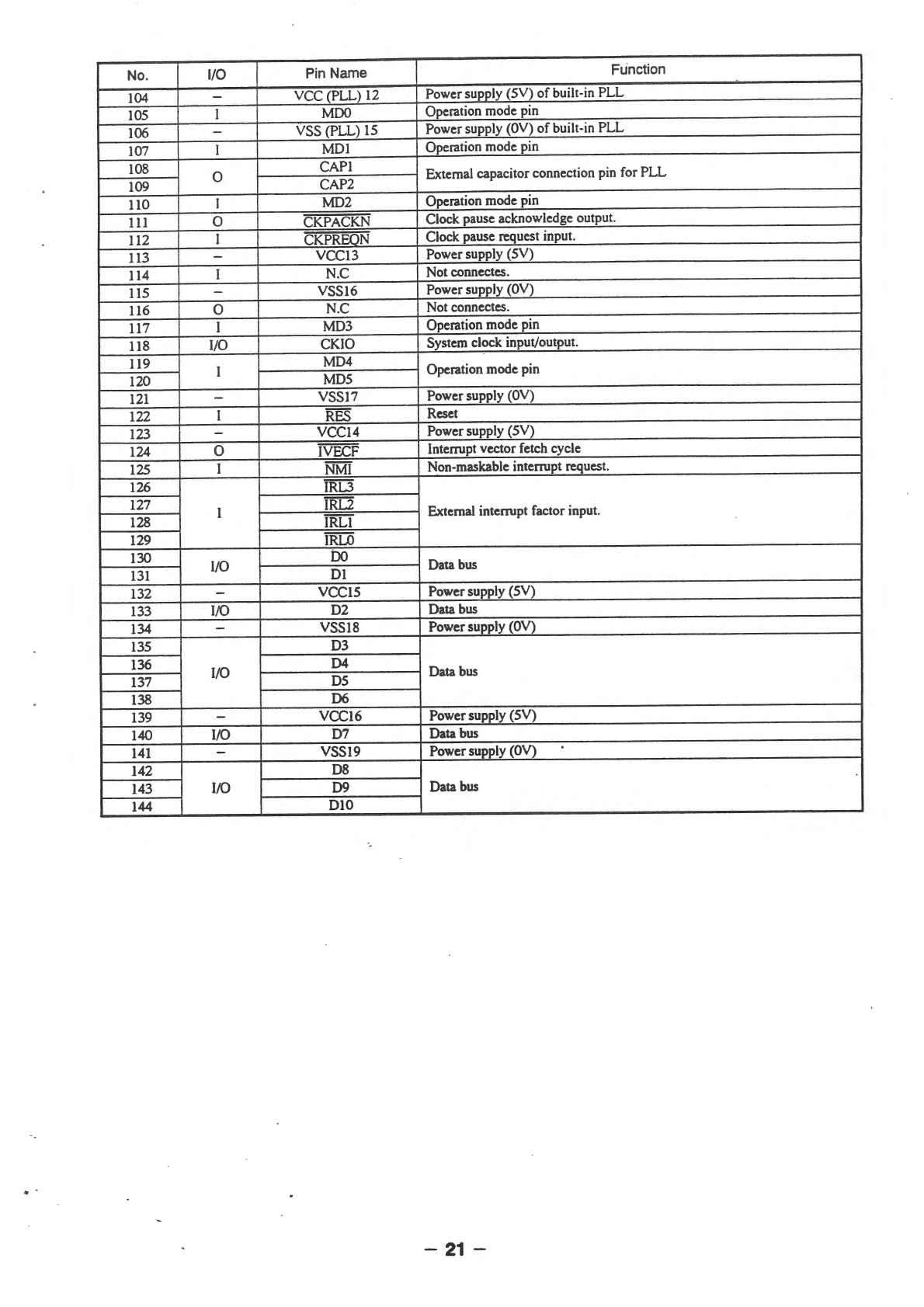

No. 1/0 Pin Name Function

104 -

VCC(PLL)

12 Powersuooly (SV)

of

built-in PLL

105 I

MDO

Operation mode pin

106 -

VSS(PLL)lS

Powersupply

(OV)

of

built-in

PLL

107 I MDI Operation mode pin

108 0 CAPI External capacitor connection pin for

PLL

109 CAP2

llO

I MD2 Operation mode pin

Ill

0 CKPACKN Clock pause acknowledge output.

112 I CKPRt-:!JN Clock pause request input.

ll3

-

VCCI3

Powersupply (SV)

ll4

I N.C Not connectes.

ll5

-VSS16 Powersupply

(OV)

ll6

0 N.C Not connectes.

ll7

I MD3 Operation mode pin

118 1/0 CKIO System clock input/output.

ll9

I MD4 Operation mode pin

120

MDS

121

-VSS17 Powersupply

(OV)

122 I RES Reset

123 -VCC14 Powersupply (SV)

124 0 JVECF Interrupt vector fetch cycle

125 I NM! Non-maskable interrupt request.

126 IRL3

127 I

IRL2

External interrupt factor input.

128 IRLI

129

IRLO

130 1/0 bo Data bus

131

Dl

132 -VCC15 Powersupply (5V)

133 1/0 D2 Data bus

134 -VSS18 Powersupply

(OV)

135 D3

136 1/0

04

Data bus

137 D5

138

06

139 -VCC16 Powersupply (SV)

140 1/0 D7 Data bus

141

-VSS19 Powersupply

(OV)

142 D8

143 1/0 D9 Data bus

144

010

..

-

21

-

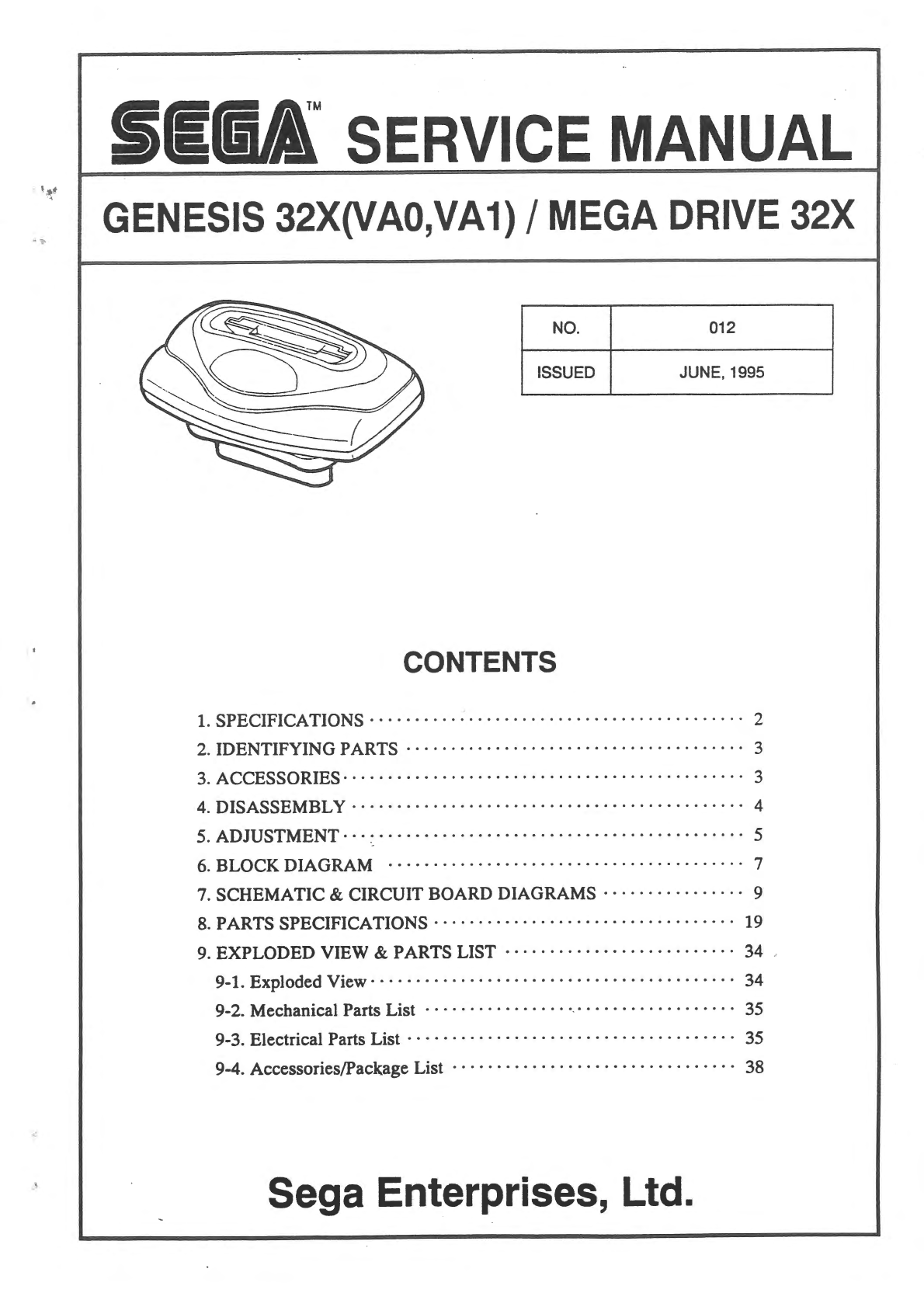

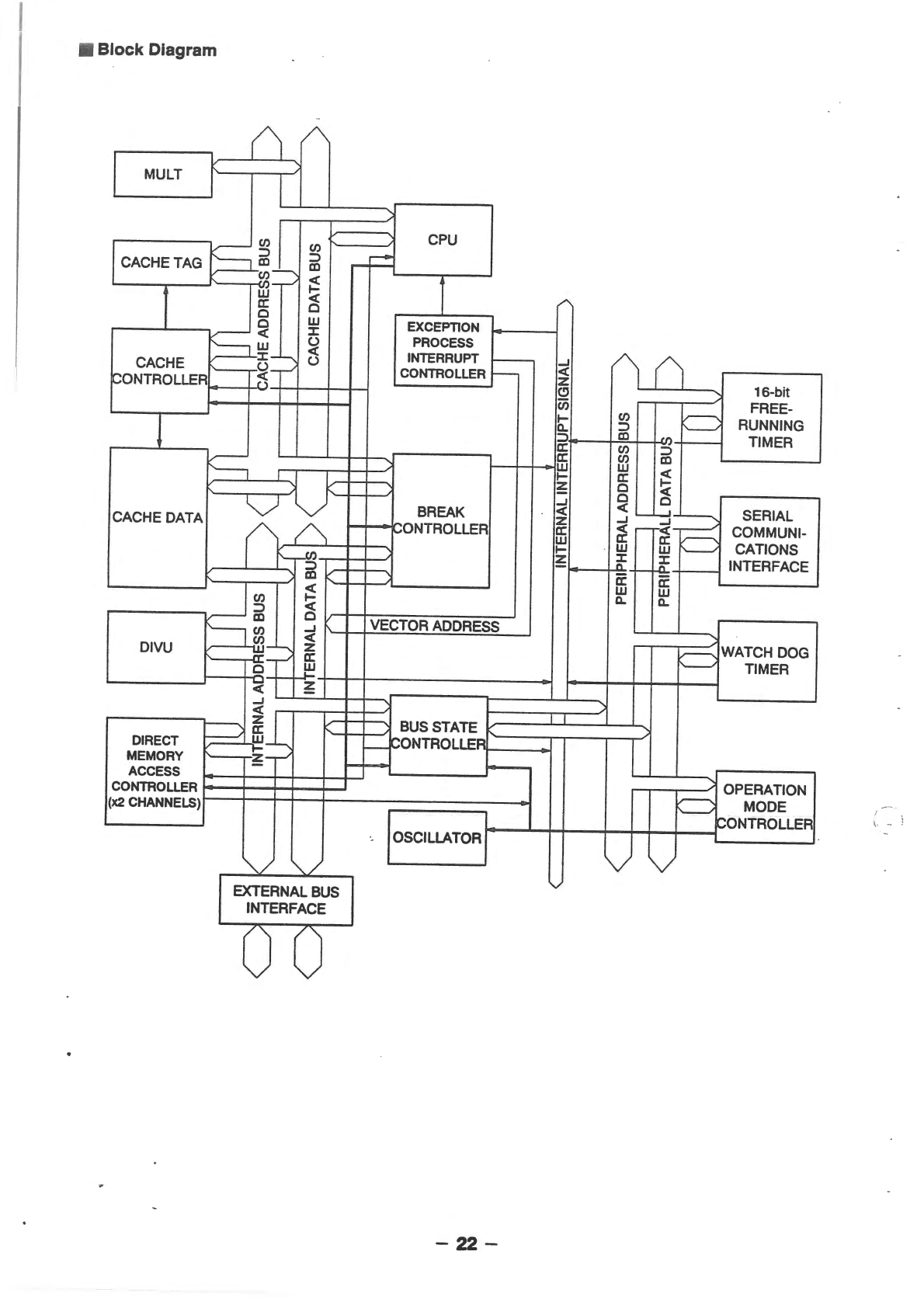

• Block Diagram

~

MULT

'.:

en

CPU

CACHETAG

~~-'--...

en

-

::>

CD

--

~-__/

~

l

/"

a:

0

0 w EXCEPTION

0

v--

<(

J:

-

~

PROCESS

[::::::L~---

INTERRUPT ..___

..J

r)

(I

CACHE

()

_

_,

()

CONTROLLER

,___

<(

~

z 16-bit

CONTROLLER (!)

~

c;;

FREE-

.....

en

r--..

RUNNING

a..

::>

'----'

~-

CD

-~

TIMER

en

:::>

a:

en

CD

v-

' w w

<(

['------,

.....

a:

.....

~

z 0

<(

..J

0 0

v BREAK

<( <(

...__l_..i

~.

SERIAL

z

..J

..J

' COMMUNI-

CACHE DATA

()_~

.:.ONTROLLER

a:

<(

~~<(--

w

a: a:

v--.._

CATIONS

.....

w

w~

z

~-

~

INTERFACE

~

-

CD

k'

a:

a:

<(

w w

~~

I-

a..

a..

<(

0 VECTOR ADDRESS

'~-~

..J

'

<(

v-------

WATCH DOG

DIVU z "----" TIMER

cil

a:

~

....

~

<(

..J

'

<(

~~1

I/

BUS STATE

DIRECT

~w

~ONTROLLES:

I-

,___

MEMORY -

~---

ACCESS , OPERATION

CONTROLLER

v-------

MODE

"----"

(x2 CHANNELS)

~ONTROLLER

OSCILLATOR

"/

"../

EXTERNAL BUS

INTERFACE

0

()

-22-

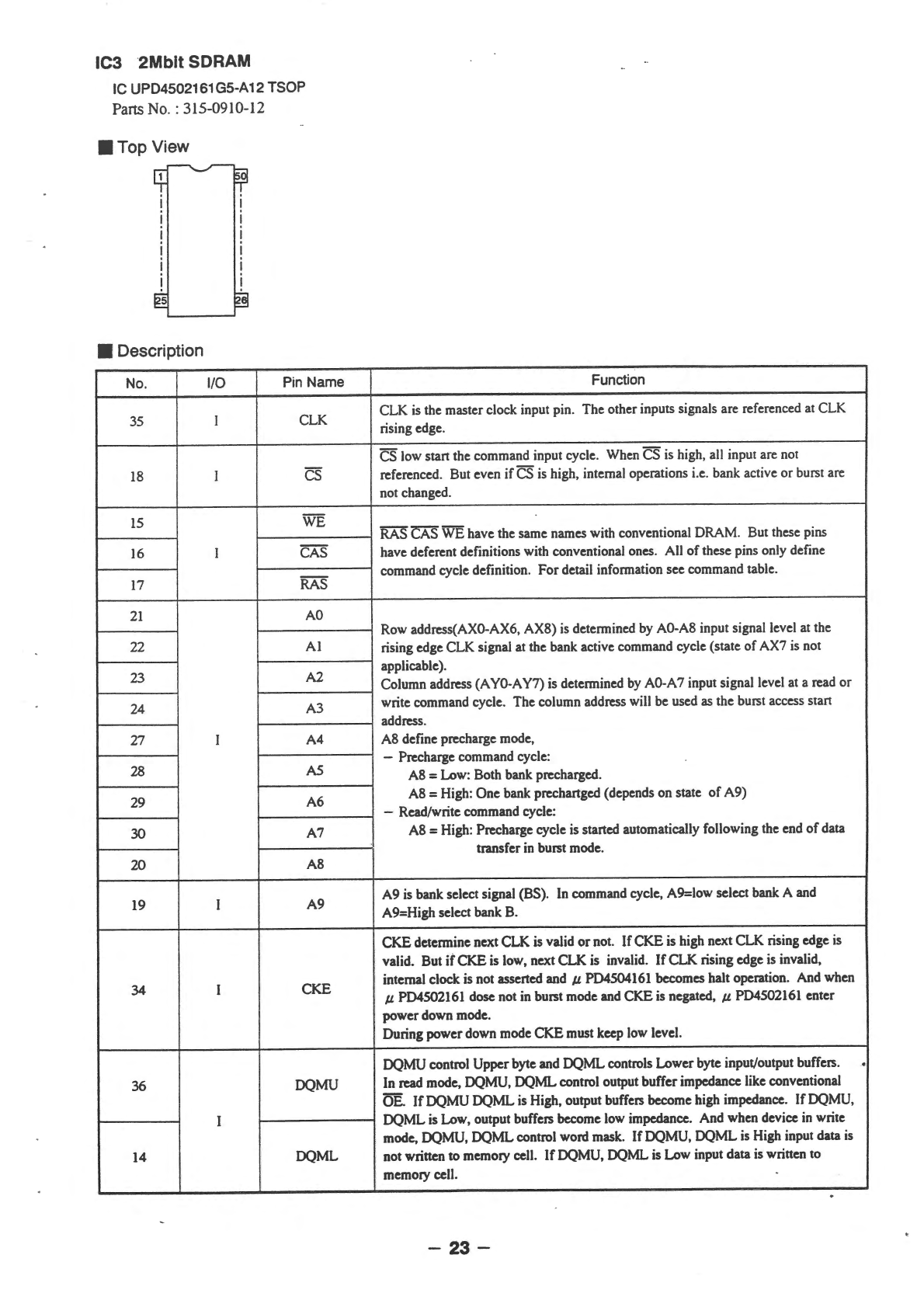

IC3 2Mblt SDRAM

IC

UPD4502161G5-A12

TSOP

Pans

No.

:

315-0910-12

•Top

View

• Description

No.

110

Pin Name

35 I CLK

18 I cs

15

WE

16 I CAS

17 RAS

21

AO

22

Al

23

A2

24 A3

27 I A4

28 AS

29

A6

30 A7

20

A8

19 I A9

34 I

CKE

36 DQMU

I

14 DQML

Function

CLK

is

the master clock input pin. The other inputs signals are referenced at CLK

rising edge.

CS low start the command input cycle. When CS

is

high, all input are not

referenced. But even

if

CS is high, internal operations i.e. bank active

or

burst are

not changed.

RAS CAS

WE

have the same names with conventional DRAM. But these pins

have deferent definitions with conventional ones. All

of

these pins only define

command cycle definition.

For

detail information see command table.

Row address(AXO-AX6, AXB) is determined by A0-A8 input signal level at the

rising edge CLK signal at the bank active command cycle (state

of

AX7 is not

applicable).

Column address (A

YO-A

Y7) is determined

by

AO-A

7 input signal level at a read

or

write command cycle. The column address will be used as the burst access start

address.

AB

define precharge mode,

-Precharge command cycle:

A8 = Low: Both bank prccharged.

AB= High: One bank prcchartged (depends on state

of

A9)

-Read/write command cycle:

AS

= High: Prccharge cycle

is

started automatically following the end

of

data

transfer

in

burst mode.

A9 is bank select signal (BS). In command cycle, A9=low select bank A and

A9=High select bank B.

CKE

determine next CLK is valid

or

not.

If

CKE is high next CLK rising edge is

valid. But

if

CKE

is low, next CLK is invalid.

IfCLK

rising edge is invalid,

internal clock is not asserted and

JI.

PD4504161 becomes halt operation. And when

JI.

PD4502161 dose not in burst mode and CKE

is

negated,

p.

PD4502161 enter

powerdown mode.

During powerdown mode CKE must keep low level.

DQMU control Upper byte and DQML controls Lower byte input/output buffers. .

In

read

mode, DQMU, DQML control output buffer impedance like conventional

OE.

IfDQMU

DQML is High, output buffers become high impedance. IfDQMU,

DQML is Low, output buffers become low impedance. And when device

in

write

mode, DQMU, DQML control word mask.

If

DQMU, DQML

is

High input data

is

not written to memory cell.

If

DQMU, DQML is Low input data is written to

memory cell.

-

23-

No.

1/0

Pin Name Function

2

DQO

3

DQI

..

5

DQ2

6

DQ3

8 DQ4

9

DQ5

11

DQ6

12

DQ7

1/0 1/0

pins

are

the

same

as

conventional

DRAM.

39

DQ8

40

DQ9

42

DQIO

43

DQll

45

DQ12

46

DQ13

48

DQI4

49

DQI5

I

7

13

-

Vee

Powersupply ofinternal circuits.

25

38

44

4

10

26

·-

-

Vss

Powersupply of

internal

circuits.

41

47

50

31,32 -

GND

Ground pins

-24-

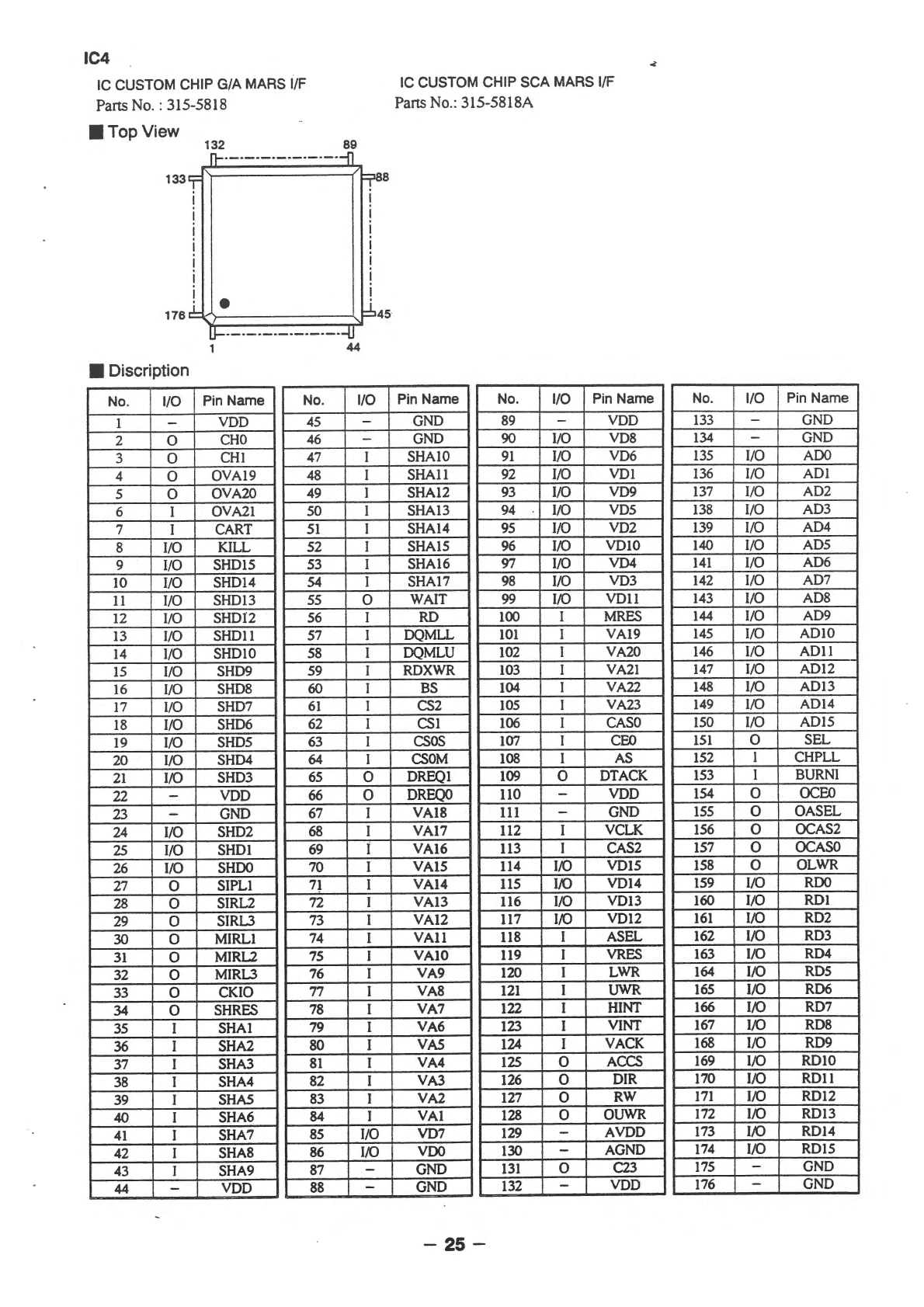

IC4

IC CUSTOM CHIP G/A MARS

llF

Parts No. : 315-5818

•TopView

132

133

• Discription

No.

1/0

Pin Name No.

1 -VDD 4S

2 0

CHO

46

3 0 CHI 47

4 0 OVA19 48

s 0 OVA20 49

6 I OVA21

so

7 I CART

SI

s I/O KILL S2

9

l!O

SHDlS

S3

10 l/O SHD14 54

11

1/0 SHD13

SS

12 l/O SHD12 56

13 1/0

SHDll

S7

14

l!O

SHD10 58

IS

110

SHD9

59

16 1/0 SHD8

60

17

110

SHD7

61

18 1/0 SHD6 62

19

l!O

SHDS 63

20

l!O

SHD4 64

21

1/0 SHD3 65

22

-VDD 66

23 -GND 67

24

1/0 SHD2 68

25 1/0

SHDl

69

26 l/O

SHOO

70

27 0 SIPLI

71

28 0 SIRL2 72

29 0 SIRL3 73

30

0 MIRLI 74

31

0 MIRL2 7S

32 0 MIRL3

76

33

0 CKIO 77

34 0 SHRES

7S

3S

I SHA!

79

36 I SHA2

80

37 I SHA3

81

3S

I SHA4 82

39 I SHAS 83

40

I SHA6 84

41

I SHA7

8S

42

I SHA8 86

43

I SHA9 87

44 -VDD 88

89

45

44

110

-

-I

I

I

I

I

I

I

I

0

I

I

I

I

I

I

I

I

I

0

0

I

I

1

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

l/O

1/0

-

-

IC CUSTOM CHIP SCA MARS

l/F

Parts No.: 315-5818A

Pin Name No.

110

Pin Name

GND 89 -VDD

GND 90

110

VDS

SHAlO

91

1/0 VD6

SHAil

92 l/O VDI

SHA12 93 1/0 VD9

SHA13 94 1/0 VDS

SHA14

9S

l/O VD2

SHAIS 96

1/0

VDlO

SHA16 97

l!O

VD4

SHA17 98 Ito VD3

WAIT 99

Ito

VDU

RD 100 I MRES

DQMLL

101

I VA19

DQMLU 102 I VA20

RDXWR 103 I

VA21

BS 104 I VA22

CS2

lOS

I VA23

CSI 106 I

CASO

csos

107 I

CEO

CSOM

108 I AS

DREQl 109 0 DTACK

DREQO

llO

-VDD

VAIS

lll

-GND

VA17 112 I VCLK

VA16 113 I CAS2

VAIS 114 1/0

VDlS

VA14

llS

1/0 VD14

VA13

ll6

Ito

VD13

VA12 117

1/0

VD12

VAil

llS

I ASEL

VAID 119 I VRES

VA9 120 I LWR

VAS

121

I

VWR

VA7 122 I HINT

VA6 123 I VINT

VAS 124 I VACK

VA4 125 0 ACCS

VA3 126 0 DIR

VA2 127 0 RW

VAi

128 0 OUWR

VD7 129 -AVDD

VDO

130 -AGND

GND

131

0 C23

GND 132 -VDD

-

25-

No.

1/0

Pin Name

133 -GND

134 -GND

13S

1/0

ADO

136 1/0

ADI

137

110

AD2

138 1/0 AD3

139 1/0 AD4

140

110

ADS

141

110

AD6

142

110

AD7

143

l!O

ADS

144 1/0 AD9

14S

1/0 ADIO

146 1/0

ADll

147

110

AD12

148

110

AD13

149 1/0

ADl4

ISO

110

ADIS

lSl

0

SEL

IS2 I CHPLL

1S3 I BURN!

154 0

OCEO

ISS 0 OASEL

1S6 0 OCAS2

1S7

0 OCASO

1S8

0 OLWR

1S9

110

RDO

160 1/0 RDI

161

1/0 RD2

162 1/0 RD3

163 1/0 RD4

164 1/0 RDS

16S

1/0 RD6

166 Ito RD7

167 1/0 RDS

168 1/0 RD9

169 I/O RD10

170 1/0

RDll

171

1/0 RD12

172 1/0 RD13

173 1/0 RD14

174 1/0 ROIS

17S

-GND

176 -GND

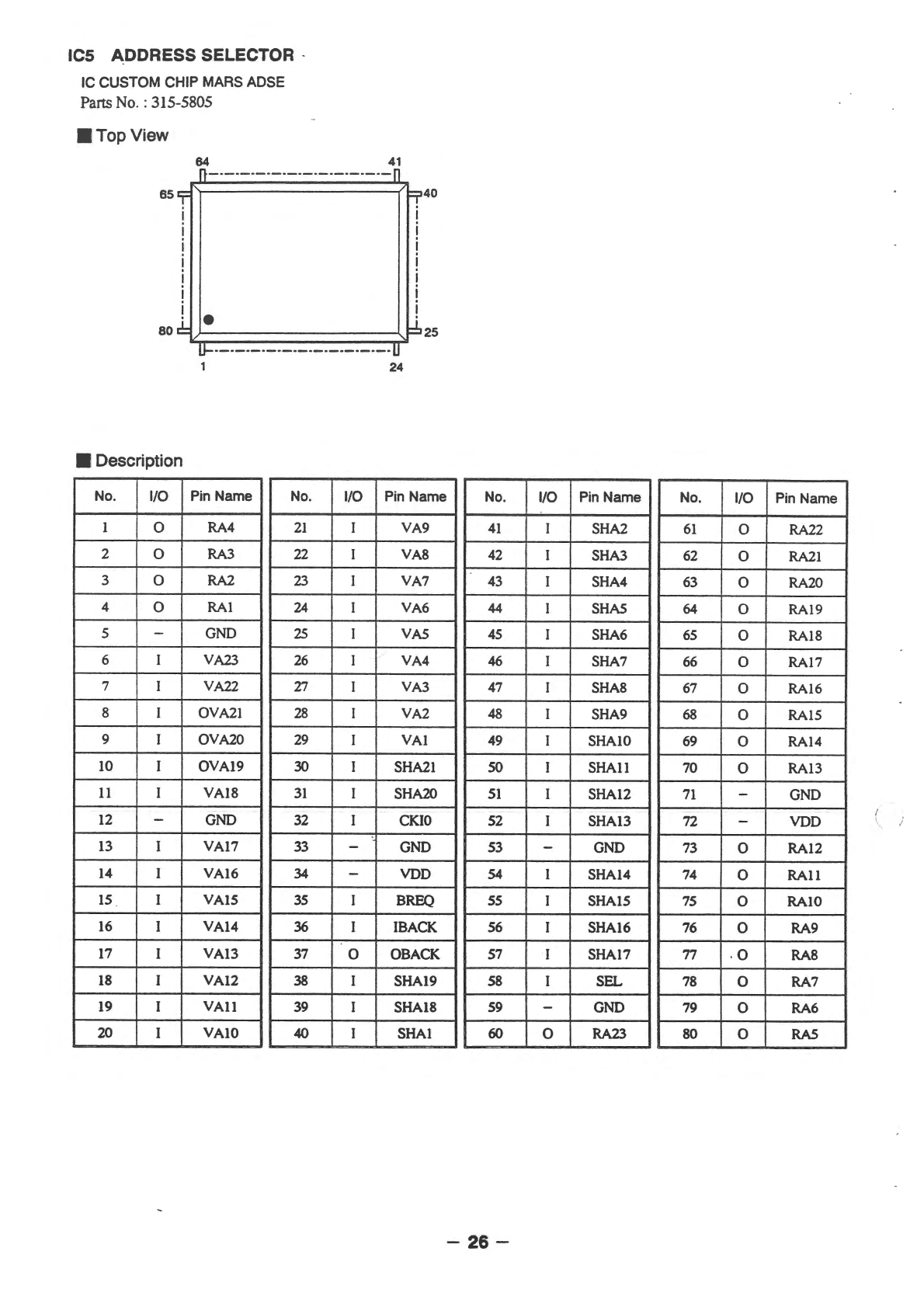

IC5 ADDRESS SELECTOR ·

IC

CUSTOM CHIP

MARS

ADSE

Parts No. : 315-5805

•TopView

65

80

I

I

I

I

• Description

No. 1/0

1 0

2 0

3 0

4 0

5 -

6 I

7 I

8 I

9 I

10

I

11

I

12

-

13

I

14

I

15

I

16

I

17

I

18

I

19

I

20

I

64

•

Pin Name No.

RA4

21

RA3

22

RA2

23

RAl

24

GND

25

VA23

26

VA22

27

OVA21

28

OVA20

29

OVA19

30

VA18

31

GND

32

VA17

33

VA16

34

VAIS

35

VA14

36

VA13

37

VA12

38

VAil

39

VAIO

40

1/0

I

I

I

I

I

I

I

I

I

I

I

I

-

-

I

I

0

I

I

I

41

40

25

24

Pin

Name

No. 1/0 Pin

Name

No. 1/0 Pin

Name

VA9

41

I

SHA2

61

0

RA22

VA8

42

I

SHA3

62

0

RA21

VA7

43

I

SHA4

63

0

RA20

VA6

44 I

SHAS

64 0

RA19

VAS

45

I

SHA6

65

0

RA18

VA4

46 I

SHA7

66

0

RA17

VA3

47

I

SHA8

67

0

RA16

VA2

48 I

SHA9

68

0

RAIS

VAl

49

I

SHA

IO

69

0

RA14

SHA21

50 I SHAll

70

0

RA13

SHA20

51

I

SHA12

71

-

GND

-

CKIO

52

I

SHA13

72 -

VDD

GND

53

-

GND

73

0

RA12

VDD

54 I

SHA14

74

0 RAll

BREQ

55 I

SHA15

75

0

RAIO

IBACK

56

I

SHA16

76

0

RA9

OBA

CK

57

I

SHA17

77

.Q

RAB

SHA19

58 I

SEL

78

0

RA7

SHA18

59 -

GND

79

0

RA6

SHAl

60 0 RA23

80

0 RAS

-

26-

IC6 8bit 20MHz D/A CONVERTER

IC

CUSTOM CHIP G/A MARS VDPNEC

Parts

No. :

315-5781

•TopView

108

73

109

72

144 37

36

• Description

No. 1/0 Pin Name No.

1/0

1 -

VDD

37

-

2 -

VDD

38

-

3 -

VDD

39

1/0

4

1/0

ODO

40

1/0

s

1/0

ODl

41

1/0

6

1/0

OD2

42

1/0

7

1/0

OD3

43

1/0

8

1/0

OD4

44

1/0

9

1/0

ODS

4S

1/0

10

1/0

OD6

46

1/0

11

1/0

OD7

47

1/0

12

1/0

OD8

48

1/0

13

1/0

OD9

49

1/0

14

1/0

ODlO

so

1/0

IS

1/0

ODll

51

1/0

16

1/0

OD12

S2

1/0

17

1/0

OD13

S3

1/0

18

1/0

OD14

S4

I

19

1/0

ODIS

SS

I

20

0

ORAS

56

I

21

0

OCAS

57

I

22

0

OOE

58

·1

23

0

OLWE

59

I

24

0

OUWE

60 0

25

0

OAO

61

I

26

0

OAl

62

0

27

0

OA2

63

0

28

0 0A3

64

I

29

0

OA4

65

I

30

0

OAS

66 I

31

0 0A6

67

I

32

0

OA7

68 I

33

I

MOD

El

69

I

34 -

VDD

70

-

3S

-

VDD

71

-

36

-

VDD

72 -

IC CUSTOM CHIP SCA MARS VDP

Parts

No. : 315-5781A

Pin Name No.

1/0

Pin Name

GND

73

-

VDD

GND

74

-

VDD

ADlS

75

-

VDD

AD14

76

-

N.C

AD13

77

0

EA7

AD12

78

0

EA6

ADU

79

0

EA5

ADlO

80

0

EA4

AD9

81

0

EA3

AD8

82

0

EA2

AD7

83

0

EAl

AD6

84

0

EAO

ADS

85

0

EUWE

AD4

86

0

ELWE

AD3

87

0

EOE

AD2

88

0

ECAS

ADI

89

0

ERAS

ADO

90

1/0

EDIS

TEST3

91

1/0

EDl4

C23

92

1/0

ED13

MODE2

93

1/0

ED12

RW

94

1/0

EDU

DIR

9S

1/0

EDlO

VACK

96

1/0

ED9

ACCS

97

1/0

EDS

HINT

98

1/0

ED7

VINT

99

1/0

ED6

MRES

100

1/0

EDS

HSY

NC

101

1/0

ED4

VSYNC

102

1/0

ED3

YS

103

1/0

ED2

NTSC

104

1/0

EDI

EDCLK

105

1/0

EDO

N.C

106

-

VDD

GND

107 -

VDD

GND

108

-

VDD

-

27-

No.

1/0

Pin Name

109

-

GND

110

-

GND

111

I

DGND

112

-

N.C

113

I

AGNDl

114

-

N.C

llS I

AVDDl

116

-

N.C

117

0

!OR

118

-

N.C

119

I

AVDD2

120

-

N.C

121

I

AGND2

122

-

N.C

123

0

JOG

124

-

N.C

125

I

!REF

126

-

N.C

127

I

VREF

128

-

N.C

129

I

COMP

130

-

N.C

131

0

IOB

132

-

N.C

133

I

AVDD3

134 -

N.C

135

I

AGND3

136

-

N.C

137

I

DVDD

138

-

N.C

139

I

TESTl

140

I

TEST2

141

0

BFP

142

0

OYS

143

-

GND

144

-

GND

IC7/8 1Mblt

CMOS

DRAM

IC

TC511664BJ-80 SOJ TOSHIBA

Parts No. : 315-0745-80

•TopView

• Description

GND

11016

11015

11014

11013

11012

11011

11010

1109

1 NC

GND

CA'S

C5E

NC

NC

NC

A1

As

As

1

GND

vcc

vss

~ ~

uwo---cr---..

IC LC321664AJ-80 SOJ SANYO

Parts

No.:

315-0961-80

AO-A7

: Address inputs

1/01

-

1/016:

Data input/outputs

RAS : Row address strobe

CAS : Column address strobe

UW : Upperbyte write enable

LW : Lower byte write enable

OE : Output enable

VCC : Powersupply

GND : Ground

NC : Notconnected

~

IC LC321664AM-80 SOP SANYO

Parts No. : 315-0962-80

l/02

1/04 1/06 l/08 l/010 l/012 1/014 1/016

1/01

1/03 l/05 l/07

l/09

1/011 1/013 1/015

0000000000000000

------~-+--It

LW

0-+--c:r---..

,__

_

___,

CAS CLOCK

GENERATOR

No.2

COLUMN COLUMN

8 ADRESS 8 DECODER

AO

BUFFER (8) SENSE AMP.

A1

REFRESH 1/0 GATE

A2

CONTROLLER

A3 --- 258 x 16---

A4 REFRESH

COUNTER (8)

A5

AB

ROW

: MEMORY ARRAY

A7 ADDRESS 8 258

BUFFER 258 x 256 x 18

CLOCK

RAS GENERATOR SUB STRAIGHTBIAS

No.1 GENERATOR

-

28-

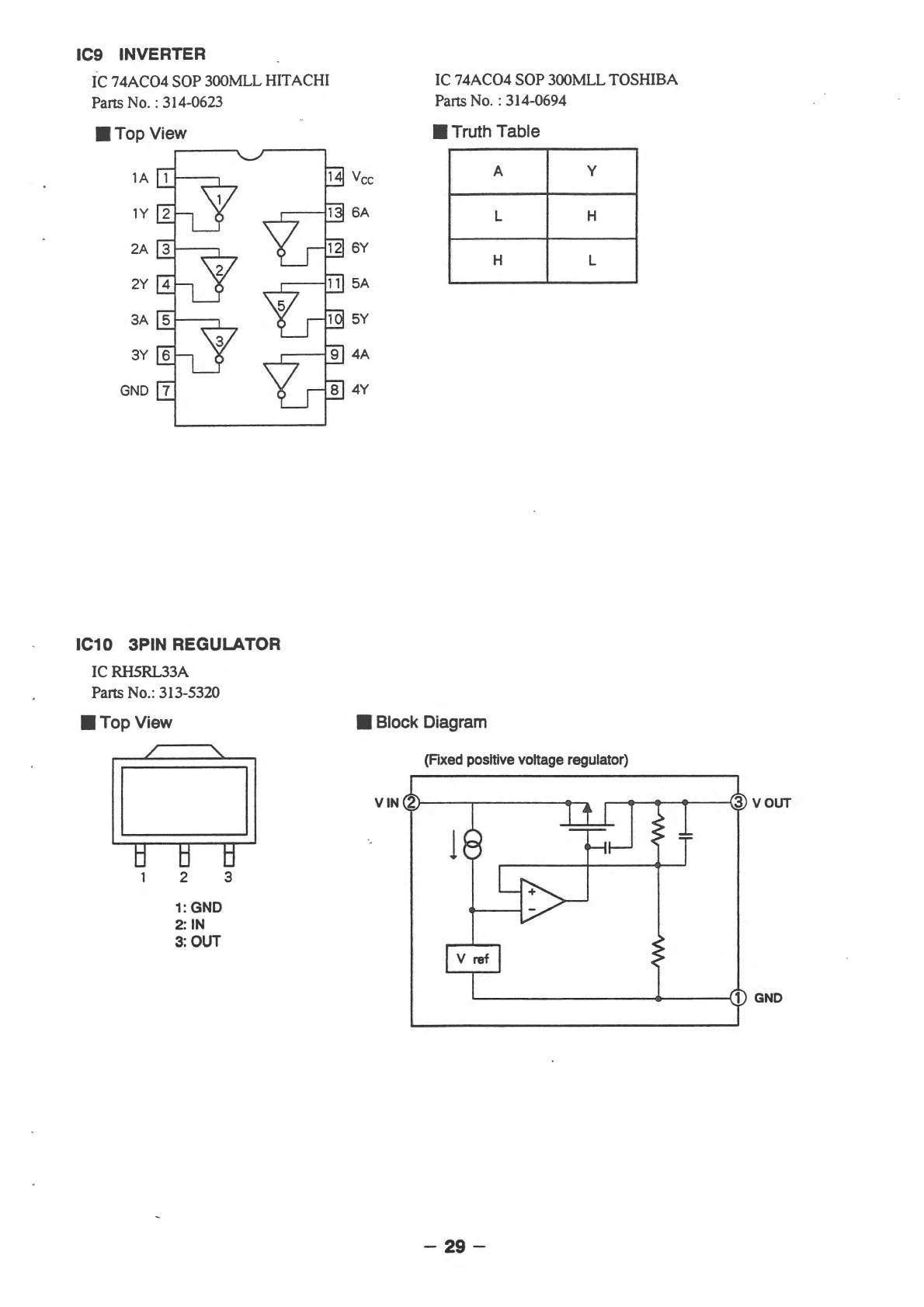

IC9 INVERTER

IC

74AC04

SOP 300MLL HITACHI

Parts No. : 314-0623

•TopView

GND

7

IC10 3PIN REGULATOR

ICRH5RL33A

Parts No.: 313-5320

•TopView

D

2 3

1:GND

2:

IN

3:0UT

IC

74AC04

SOP 300MLL TOSHIBA

Parts No. : 314-0694

•Truth

Table

A y

L H

H L

• Block Diagram

(Fixed positive voltage regulator)

~--------i3

V

OUT

1

V ref

'----------+----<1

GNO

-

29-

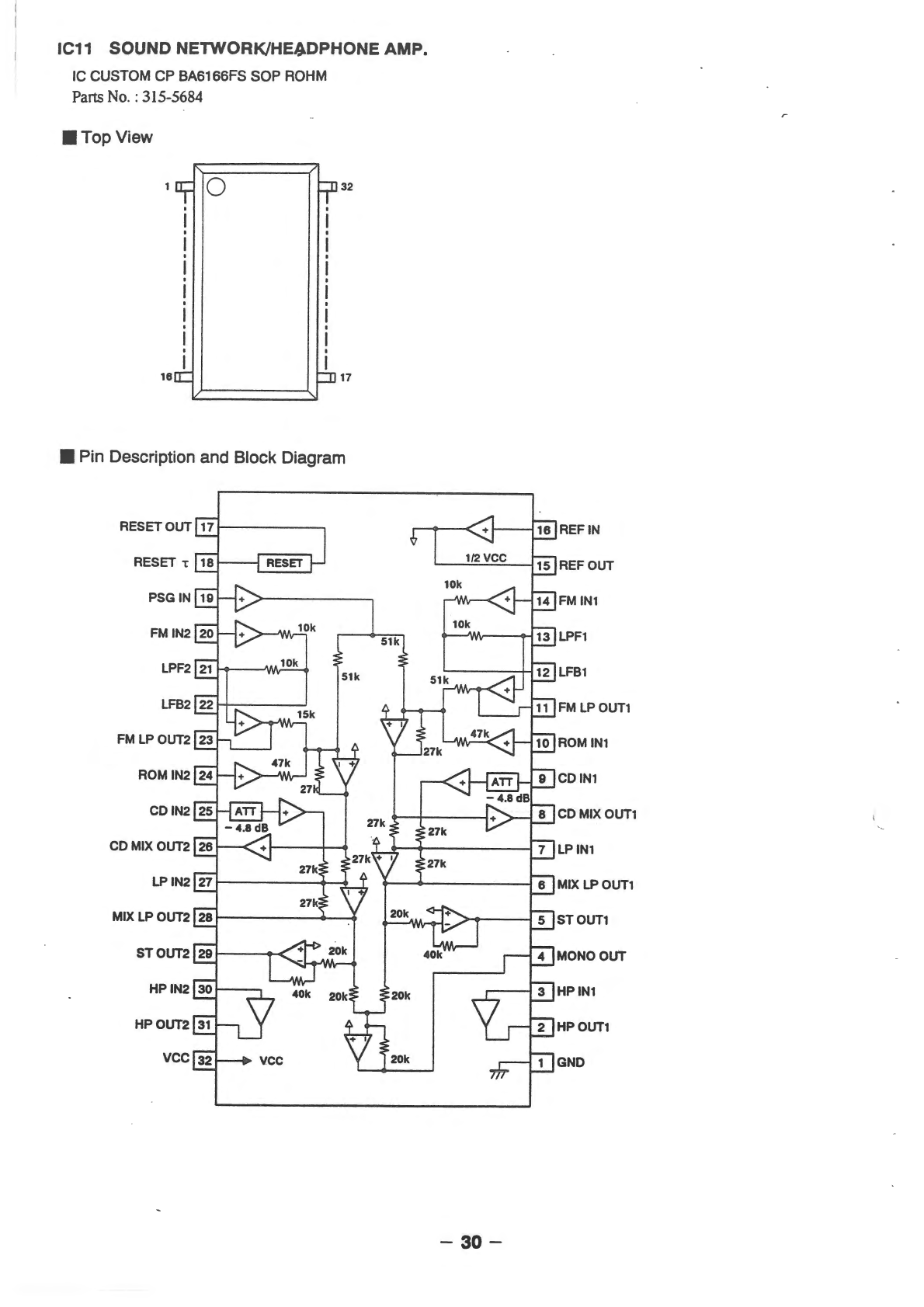

IC11 SOUND

NETWORK/HE~DPHONE

AMP.

IC CUSTOM CP BA6166FS SOP ROHM

Parts

No.

:

315-5684

•TopView

0

18

32

17

•Pin

Description and Block Diagram

RESET OUT

17

i---------,

RESET

-r

PSGIN

FMIN2

20k

REFIN

REF OUT

FM

IN1

LPF1

LFB1

FM

LPOUT1

ROM

IN1

CDIN1

CDMIXOUT1

7 LPIN1

6

MIX

LPOUT1

STOUT1

MONO

OUT

HPIN1

-

30-

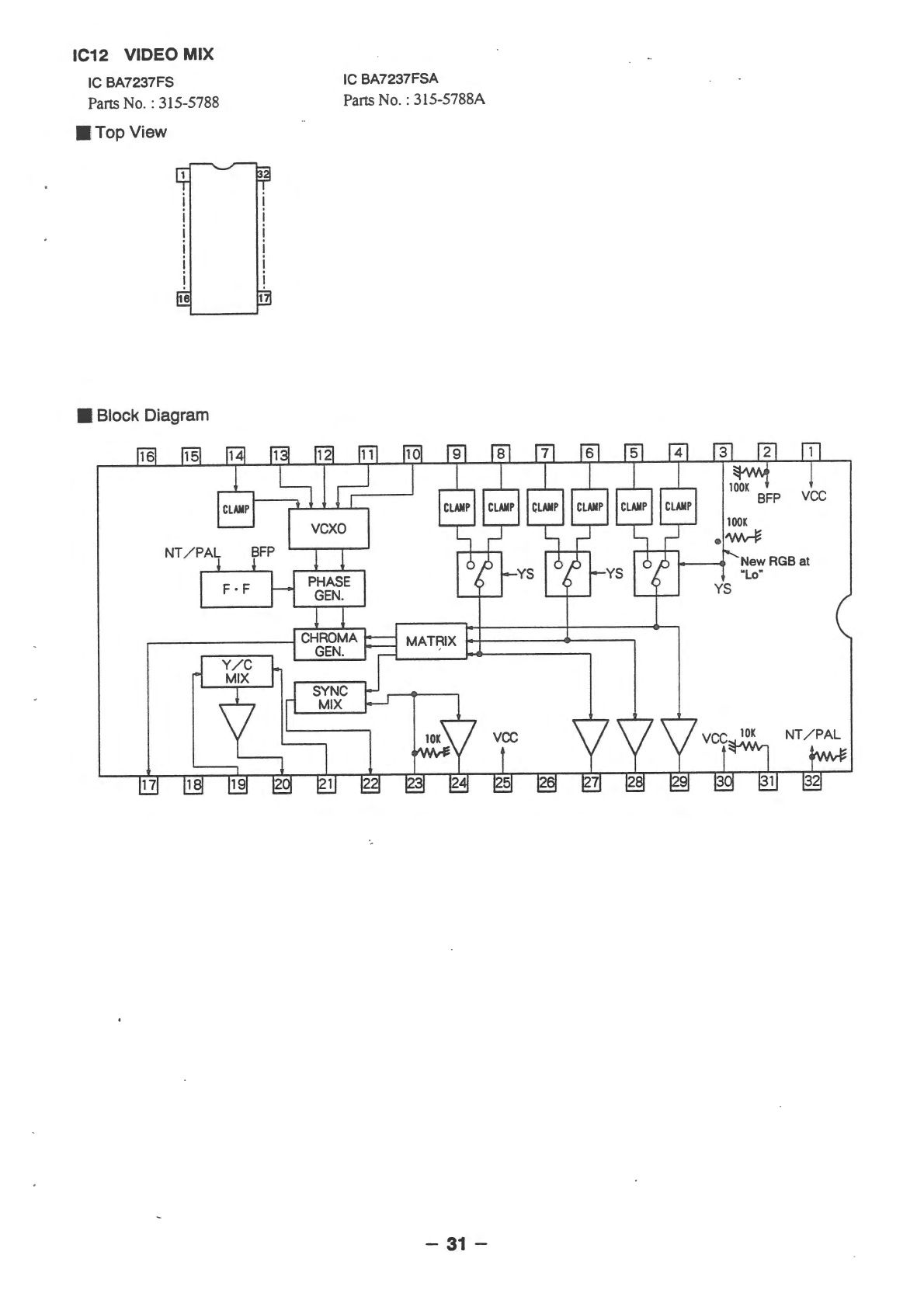

IC12 VIDEO MIX

IC BA7237FS

Parts No. : 315-5788

•TopView

• Block Diagram

16 15

NT/PAL

17

IC BA7237FSA

Parts No. : 315-5788A

F·F

YS

-

31

-

IC13 SWITCHING REGURATOR IC

IC MC34063A SOP

SP

Parts No. : 313-5244

•TopView

2

3

IC14 RESET IC

IC PST993E

Parts No. :313-5319

8

7

6

•TopView

•FrontView

0

IC IR3M03AN SOP

SP

Parts

No.

: 313-5335

• Block Diagram

Drive Collector 8

1---------~

lpk Sense 7

1--1-~

lpk

c

Oscillator T

Vee

6 Comparator

Comparator 5

1-------'

Inverting Input

• Block Diagram

-

32-

1.25V

reference

ulator

'----~

4 GND

--®OUT

This manual suits for next models

1

Table of contents

Other SEGA ENTERPRISES Game Console manuals