CRZ Technology DaisyPlus User manual

DaisyPlus Board User Guide

2 CRZ Technology

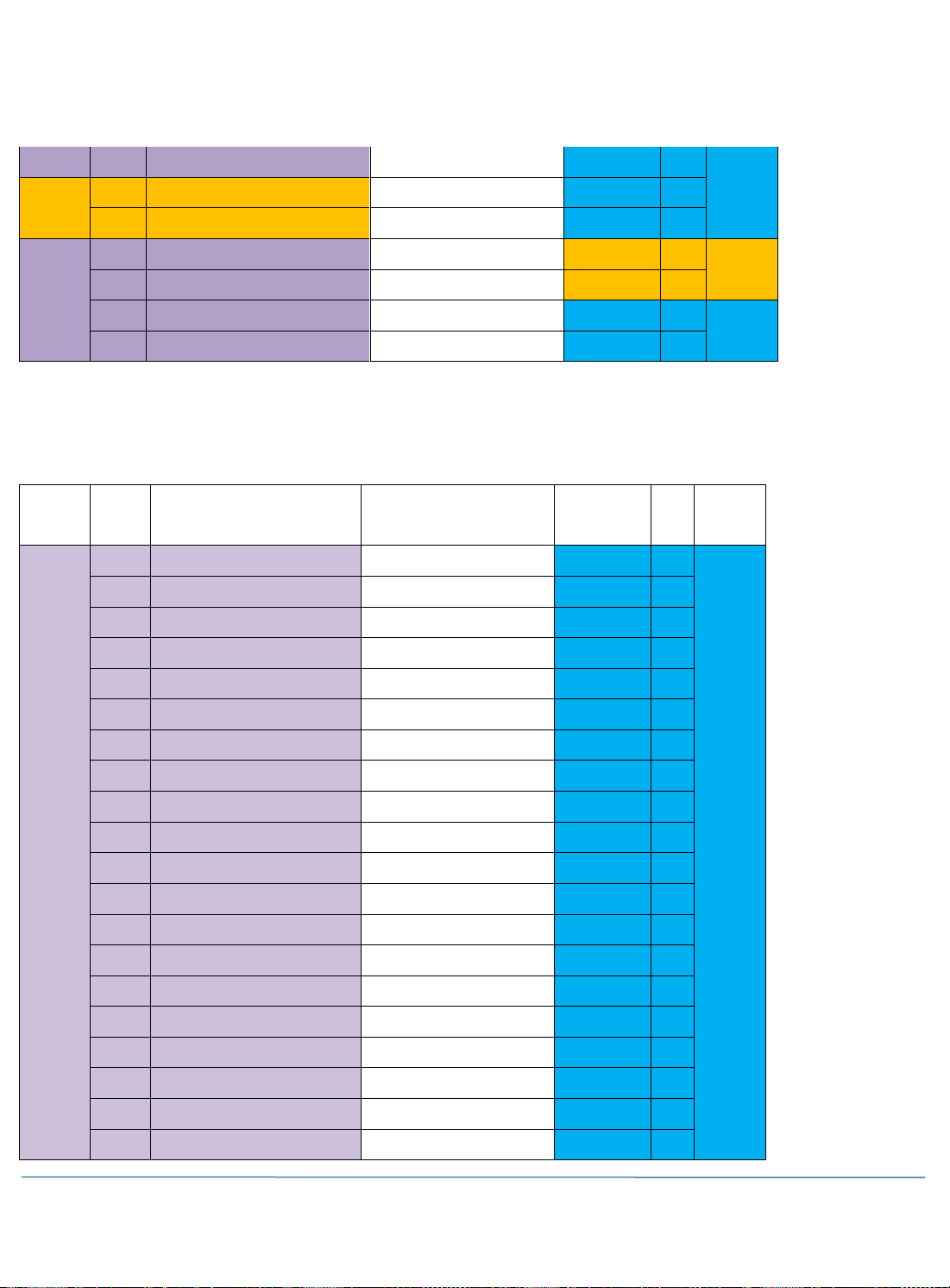

Document History

Revision

Date

Change note

1.0

2021.04.19

First draft

DaisyPlus Board User Guide

CRZ Technology 3

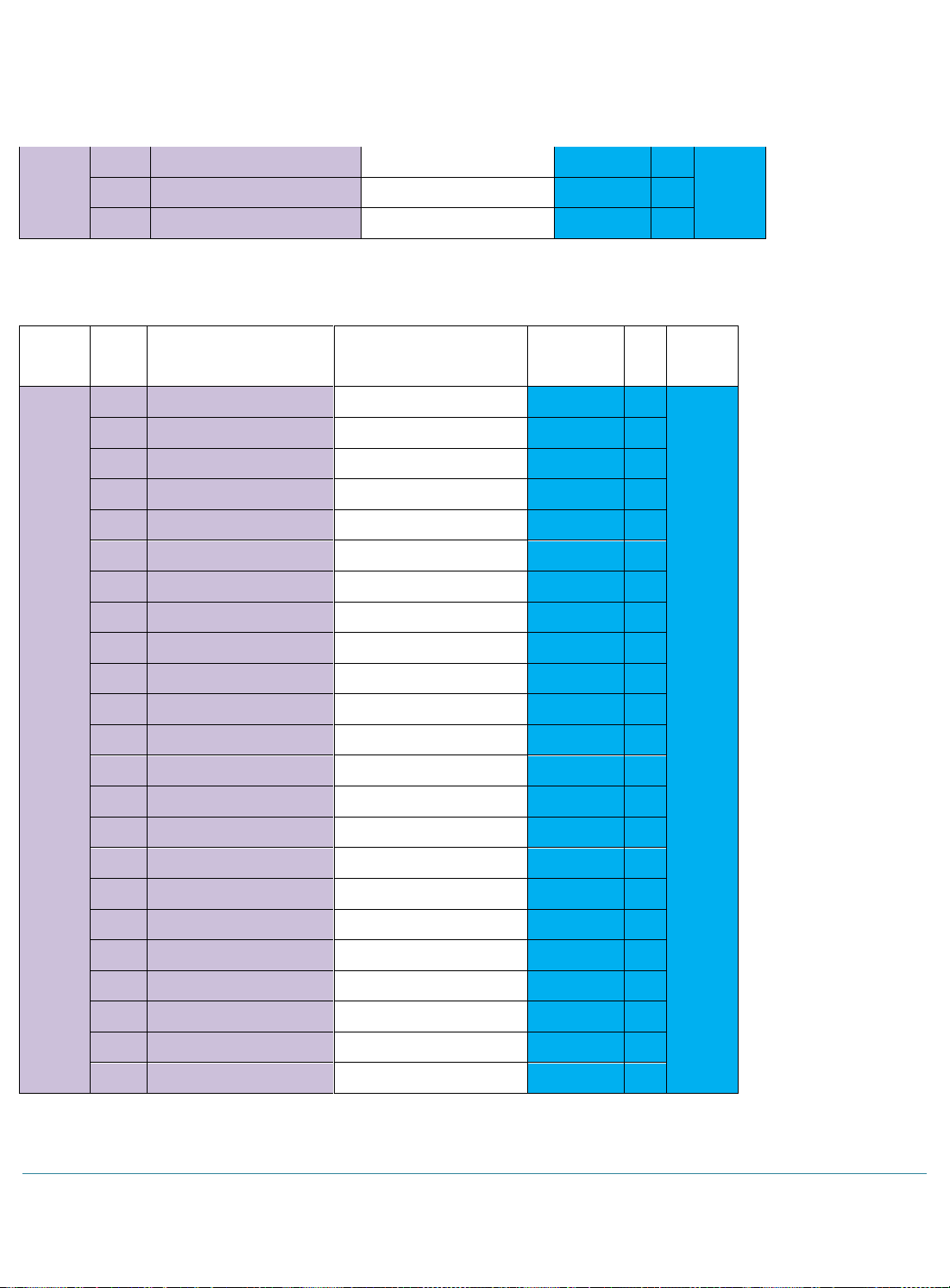

Table of Contents

1. Overview .............................................................................................................................................................................................. 4

1.1. Block Diagram ............................................................................................................................................................................................................4

1.2. Board Layout ...............................................................................................................................................................................................................5

2. LEDs and Connectors......................................................................................................................................................................... 6

2.1. Status LED .....................................................................................................................................................................................................................6

2.2. User LEDs.......................................................................................................................................................................................................................7

2.3. JTAG Connector Pinout[J7] .................................................................................................................................................................................8

2.4. uSD Card Reader[J2]...............................................................................................................................................................................................9

2.5. 2 Pin Fan connector[J1] ........................................................................................................................................................................................9

3. Operation Information .................................................................................................................................................................... 10

3.1. Mode Select DIP Switch [SW1]...................................................................................................................................................................... 10

3.2. PUSH buttons........................................................................................................................................................................................................... 11

3.3. I2C bus interfaces..................................................................................................................................................................................................12

4. Loopback board................................................................................................................................................................................ 14

4.1. NVME M.2 Loopback Card...............................................................................................................................................................................14

5. Clock system ..................................................................................................................................................................................... 15

5.1. 12-CH Clock Generator[U7].............................................................................................................................................................................15

5.2. 12-CH Clock Generator[U8].............................................................................................................................................................................16

6. MPSoC System Connections........................................................................................................................................................... 17

6.1. NOR Flash 1GBIT [U9, U10].............................................................................................................................................................................17

6.2. Dual NVME M.2 ......................................................................................................................................................................................................17

6.2.1. NVME0[J25]......................................................................................................................................................................................................17

6.2.2. NVME1[J25]......................................................................................................................................................................................................18

6.3. QSFP28 100G Ethernet ....................................................................................................................................................................................... 19

6.3.3. QSFP0 [J20]......................................................................................................................................................................................................19

6.3.4. QSFP1 [J23]......................................................................................................................................................................................................20

6.4. PS LPDDR4 [U12] ...................................................................................................................................................................................................21

6.5. PL DIMM Card Slots.............................................................................................................................................................................................26

6.5.1. DIMM0 [J8].......................................................................................................................................................................................................26

6.5.2. DIMM1 [J9].......................................................................................................................................................................................................34

6.6. PCIe x16 Endpoint [J11] .................................................................................................................................................................................... 42

6.7. 1G Ethernet PHY[U16]-Ethernet 1G[J10]................................................................................................................................................. 44

6.8. USB to Dual UART[U40] –USB Micro[J26]............................................................................................................................................. 45

6.9. NAND SO-DIMM[J28] .........................................................................................................................................................................................45

DaisyPlus Board User Guide

4 CRZ Technology

1. Overview

1.1. Block Diagram

Figure 1. High Level Block Diagram

DaisyPlus Board User Guide

CRZ Technology 5

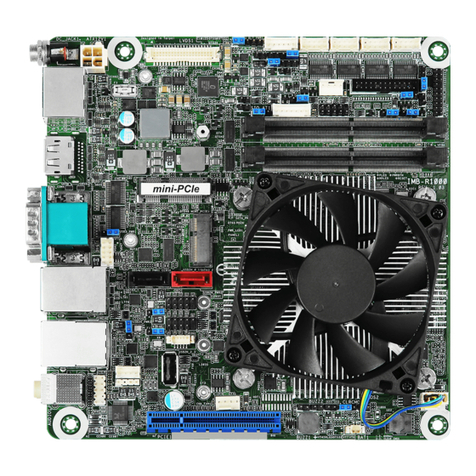

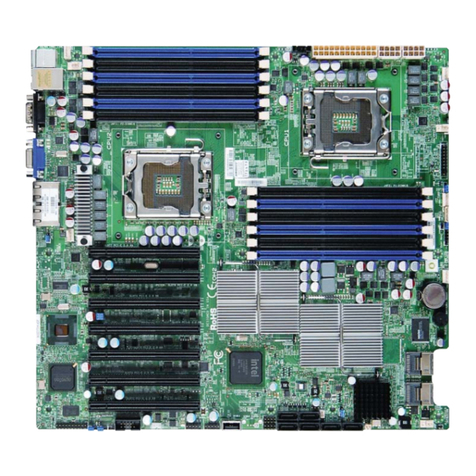

1.2. Board Layout

Front/Top(primary) side of Board

Figure 2. DaisyPlus Physical Layout: Front, Top

DaisyPlus Board User Guide

6 CRZ Technology

2. LEDs and Connectors

2.1. Status LED

Color

Board Label

Pin Name

Pin

Device

GREEN/RED

LD3

PS_INIT_B

V27

U1

GREEN

LD4

PS_DONE

Y28

RED

ErrOut(LD1)

PS_ERR_OUT

U27

RED

ErrStatus(LD2)

PS_ERR_STATUS

V28

Table 1. MPSOC Status LED

Color

Board Label

Description

GREEN

LD5

3V3 rail power good signal

GREEN

LD6

12V available from J27 ATX connector

or J11 PCIE Host

GREEN

LD16

DDR4_VDDQ power good signal

GREEN

LD18

VCC_NAND power good signal

GREEN

LD19

VCC_NAND_IO power good signal

Table 2. Power Status LED

DaisyPlus Board User Guide

CRZ Technology 7

2.2. User LEDs

There are 4 LEDs connected to PL part. All these LEDs are active High. Please refer to the following Figure and table.

-High on output = LED is ON

-Low or Tri-state = LED is OFF

Color

Board

Label

MPSOC

Description

Pin Name

Pin

RED

LED0(LD7)

B94_IO/L4_P/AD12_P

E1

User LED

RED

LED1(LD8)

B94_IO/L4_N/AD12_N

D1

User LED

RED

LED2(LD9)

B94_IO/L3_P/AD13_P

E3

User LED

RED

LED3(LD10)

B94_IO/L3_N/AD13_N

E2

User LED

Table 3. User LEDs

DaisyPlus Board User Guide

8 CRZ Technology

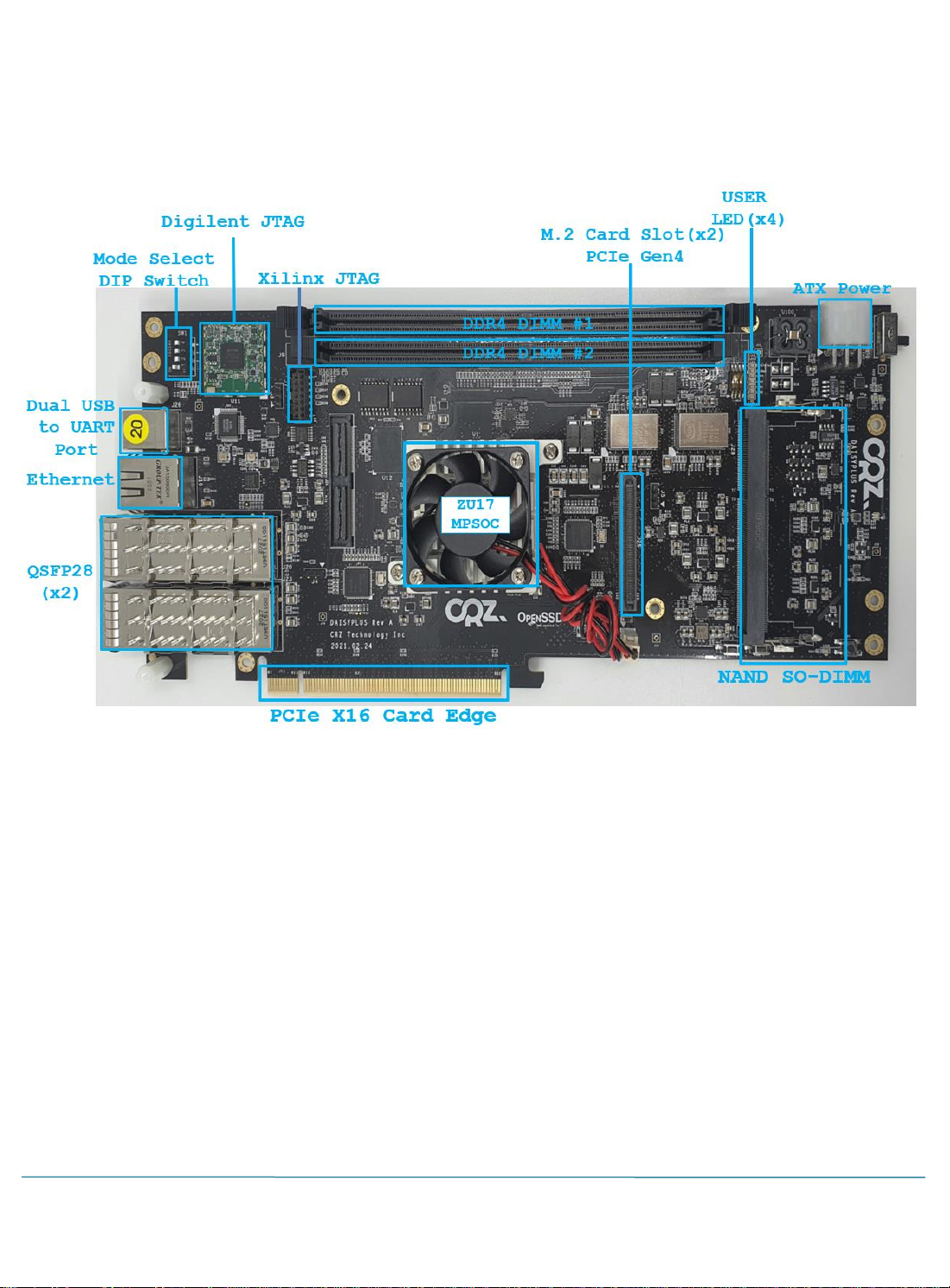

2.3. JTAG Connector Pinout[J7]

Figure 3. JTAG Connector[J7]

Device

Pin

Pin Name

Schematic Net Name

Pin

Device

VCC_3V3

2

J7

U1

AD26

B503_PS_JTAG_TMS

JTAG_TMS

4

AC26

B503_PS_JTAG_TCK

JTAG_TCK

6

AD27

B503_PS_JTAG_TDO

JTAG_TDO

8

AD25

B503_PS_JTAG_TDI

JTAG_TDI

10

NO CONNECT

12

U34

3

2A

PS_ARM_JTAG_SRST_B

14

GND

1

3

5

7

9

11

13

Table 4. Xilinx Config/Debug[J7] Signal Connections

DaisyPlus Board User Guide

CRZ Technology 9

2.4. uSD Card Reader[J2]

Schematic Net Name

MPSOC

Device

Pin Name

Pin

SDIO_DETECT

B501_PS_MIO45

T29

U1

SDIO_D0

B501_PS_MIO46

U28

SDIO_D1

B501_PS_MIO47

T28

SDIO_D2

B501_PS_MIO48

V30

SDIO_D3

B501_PS_MIO49

U29

SDIO_CMD

B501_PS_MIO50

V29

SDIO_CLK

B501_PS_MIO51

W30

Table 5. uSD Card Reader[J2] Signal Connections

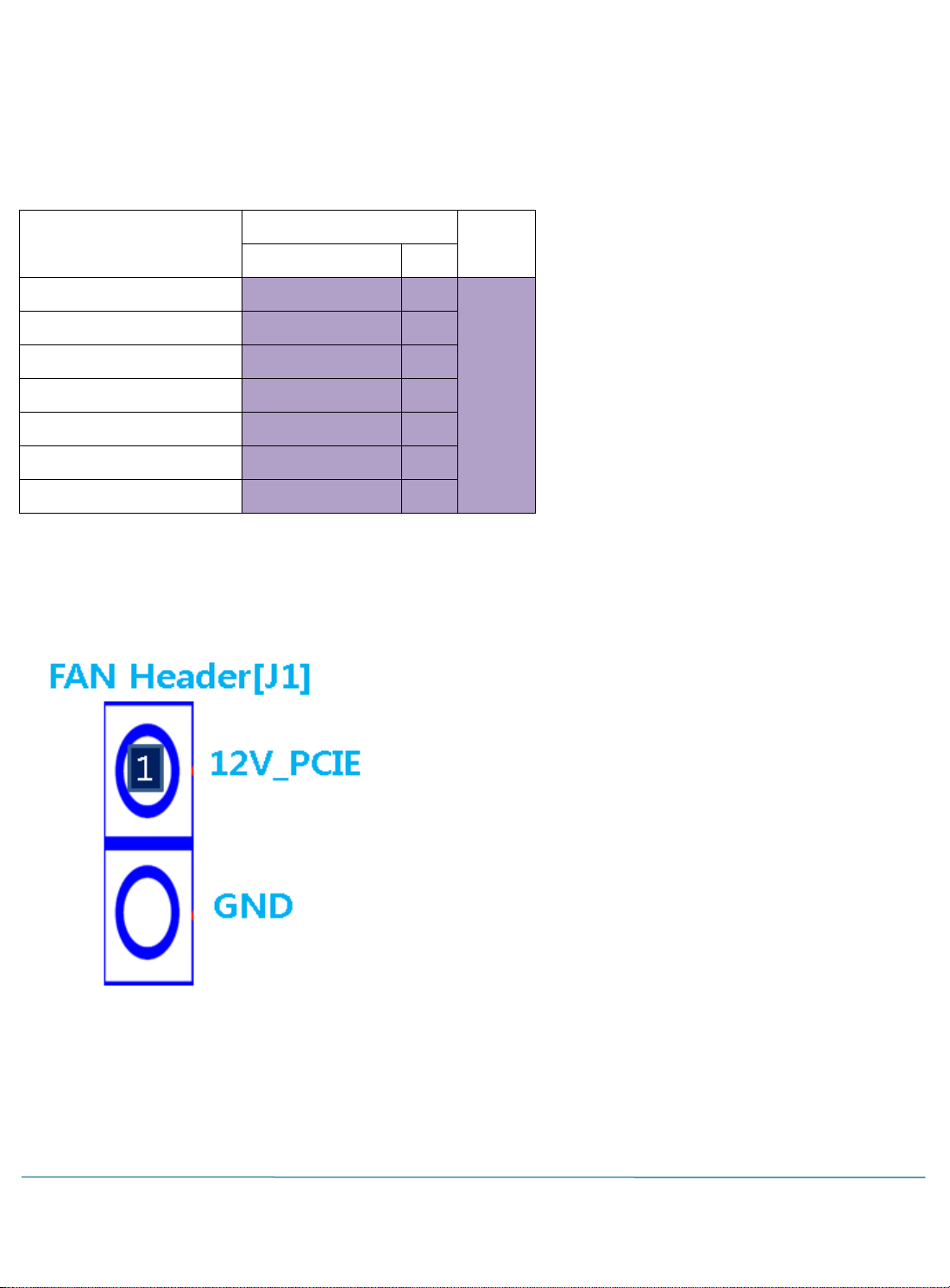

2.5. 2 Pin Fan connector[J1]

Figure 4. DC Fan Breakout Header

DaisyPlus Board User Guide

10 CRZ Technology

3. Operation Information

3.1. Mode Select DIP Switch [SW1]

There is DIP switch to select Boot mode.

Figure 5. Mode select DIP switch

MODE

Switch

[4]

[3]

[2]

[1]

JTAG

LOW(ON)

LOW(ON)

LOW(ON)

LOW(ON)

QSPI 32

LOW(ON)

LOW(ON)

HIGH(OFF)

LOW(ON)

SD1

HIGH(OFF)

HIGH(OFF)

HIGH(OFF)

LOW(ON)

Table 6. Mode select table

Switch

MPSOC

Pin Name

Pin

1

B503_PS_MODE0

AA27

2

B503_PS_MODE1

AC28

3

B503_PS_MODE2

AA28

4

B503_PS_MODE3

AB28

Table 7. Pin assignment for Mode select DIP switch

DaisyPlus Board User Guide

CRZ Technology 11

3.2. PUSH buttons

There are 3 push buttons and the default value is high.

-Button released = HIGH

-Button pressed = LOW

Device

Board Label

MPSOC

Pin Name

Pin

SW2

POR_B

B503_PS_POR_B

W27

SW3

SW3

B503_PS_PROG_B

Y27

SW4

SRST_B

B503_PS_SRST_B

AB27

Table 8. Signal assignment of push buttons

DaisyPlus Board User Guide

12 CRZ Technology

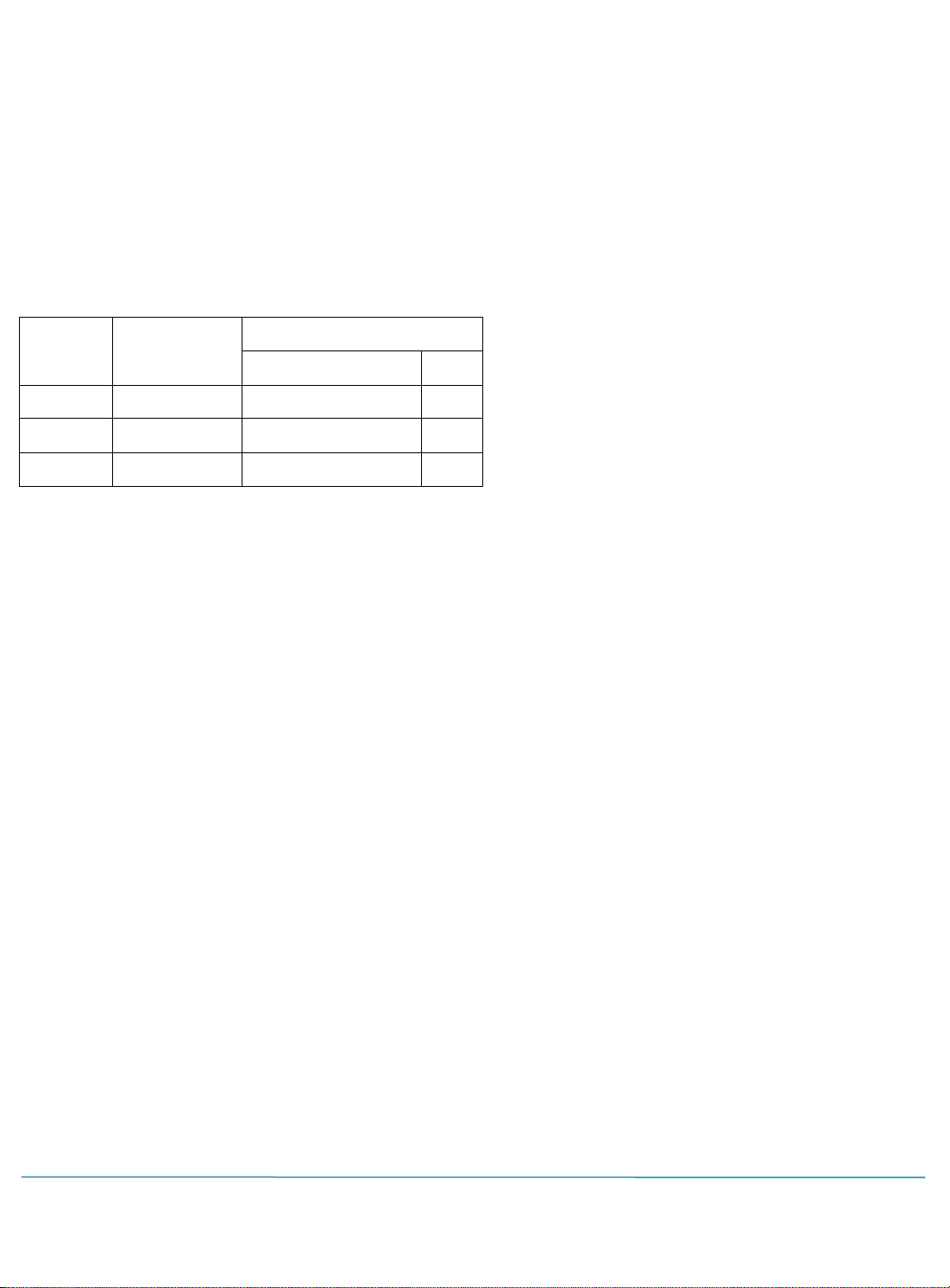

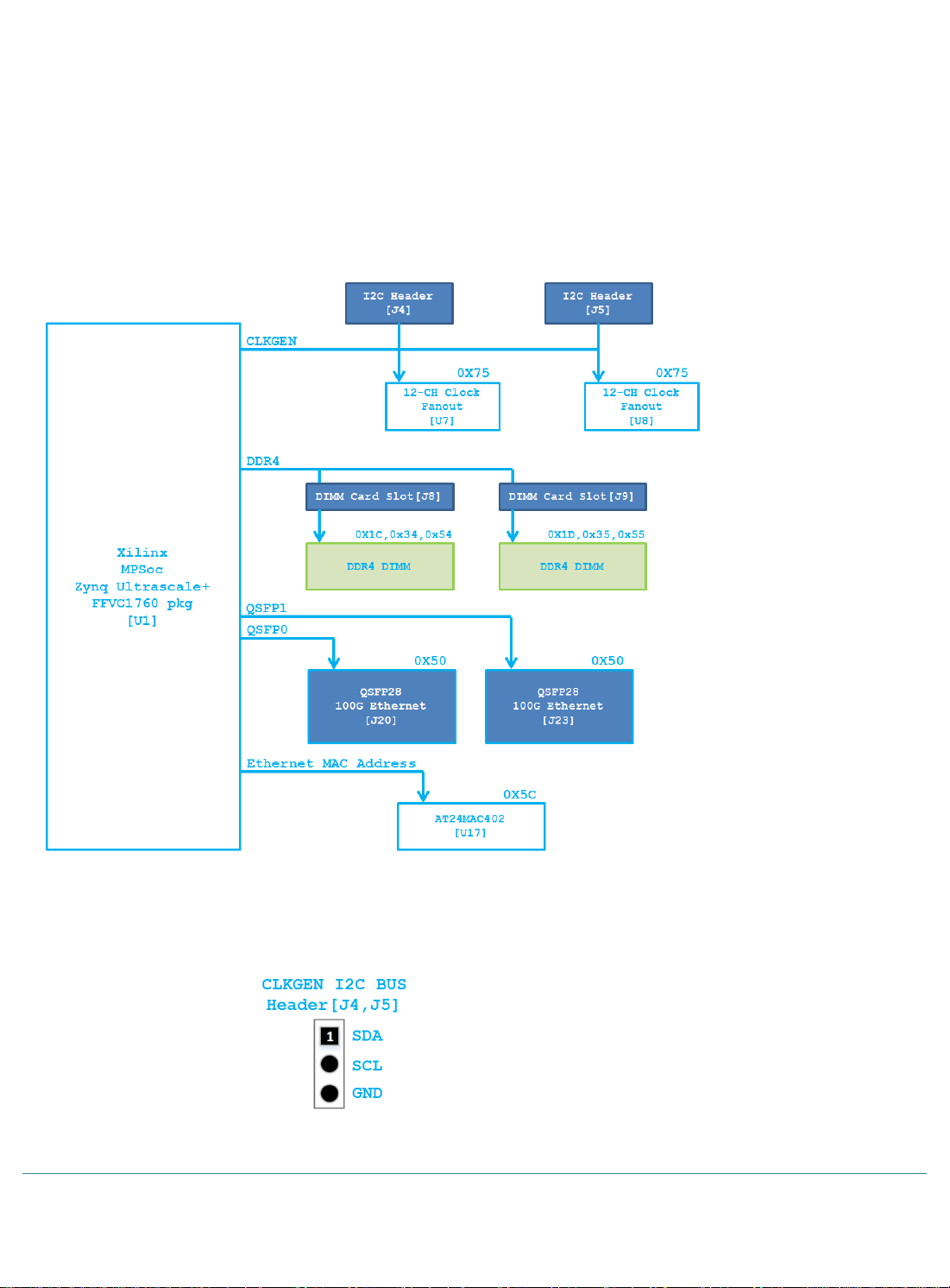

3.3. I2C bus interfaces

There are multiple I2C buses to communicate with several other devices. The block diagram below shows all I2C connections

on the board.

Figure 6. I2C Bus Block Diagram

The “CLKGEN” I2C bus is can be accessed via a 3-pin header(J4, J5)

Figure 7. CLKGEN I2C Bus Header

DaisyPlus Board User Guide

CRZ Technology 13

Device

Bus

Name

Pin

Pin Name

Schematic Net Name

Pin Name

Pin

Device

U1

CLKGEN

AJ32

B500_PS_MIO14

SI5391_0_SCL

SCLK

16

U7

AD35

B500_PS_MIO15

SI5391_0_SDA

SDA/SDIO

18

AJ31

B500_PS_MIO16

SI5391_1_SCL

SCLK

16

U8

AJ30

B500_PS_MIO17

SI5391_1_SDA

SDA/SDIO

18

Ethernet MAC

AJ31

B500_PS_MIO16

PS_I2C1_SCL

SCL

6

U17

AJ30

B500_PS_MIO17

PS_I2C1_SDA

SDA

5

DDR4

AJ32

B500_PS_MIO14

PS_I2C0_SCL

SCL

141

J8

SCL

141

J9

AD35

B500_PS_MIO15

PS_I2C0_SDA

SDA

285

J8

SDA

285

J9

QSFP0

AJ32

B500_PS_MIO14

PS_I2C0_SCL

SCL

11

J20

AD35

B500_PS_MIO15

PS_I2C0_SDA

SDA

12

QSFP1

AJ31

B500_PS_MIO16

PS_I2C1_SCL

SCL

11

J23

AJ30

B500_PS_MIO17

PS_I2C1_SDA

SDA

12

Table 9. Pin assignment of I2C Bus

DaisyPlus Board User Guide

14 CRZ Technology

4. Loopback board

There is loopback board helpful for development and testing

⚫NVME M.2 Loopback Card

4.1. NVME M.2 Loopback Card

Figure 8. NVME M.2 Loopback Card

REF DES

Connector

Description

Pin Name

Pin

TP53

P_12V

53

12V power rail

TP54

VCC3V3

54

3.3V power rail

Table 10. Test points of NVME M.2 Loopback card

DaisyPlus Board User Guide

CRZ Technology 15

5. Clock system

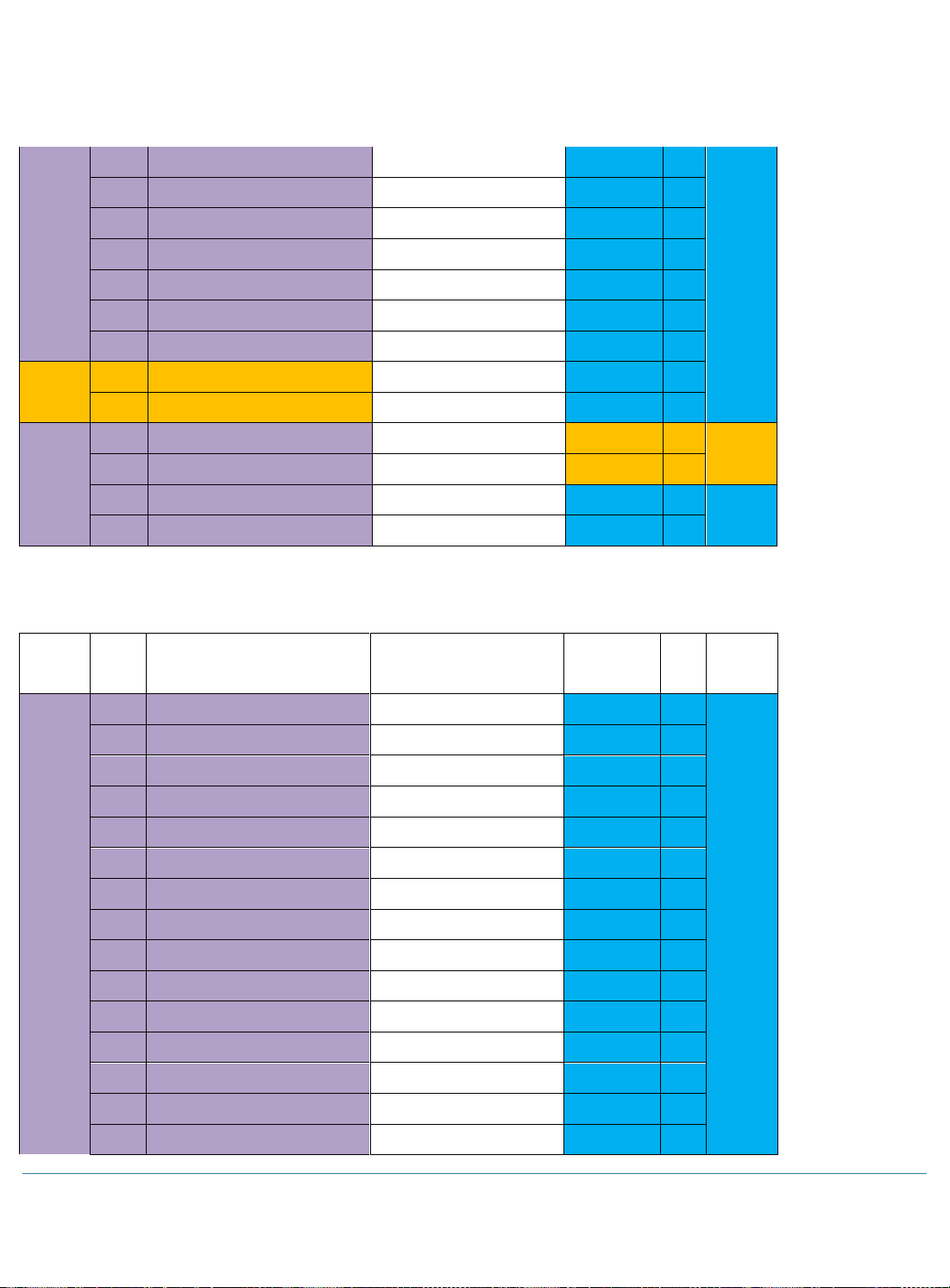

5.1. 12-CH Clock Generator[U7]

Part Manufacturer : Silicon Labs

Part Number : Sl5391

Device

Pin

Pin Name

Schematic Net Name

Pin Name

Pin

Device

U7

24

OUT0

GTR_REF_CLK0_100M_P

PS_MGTREFCLK0P_505_AG37

AG37

U1

23

OUT0b

GTR_REF_CLK0_100M_N

PS_MGTREFCLK0N_505_AG38

AG38

21

OUT0A

GTR_REF_CLK1_108M_P

PS_MGTREFCLK1P_505_AE37

AE37

20

OUT0Ab

GTR_REF_CLK1_108M_N

PS_MGTREFCLK1N_505_AE38

AE38

28

OUT1

GTR_REF_CLK2_125M_P

PS_MGTREFCLK2P_505_AC37

AC37

27

OUT1b

GTR_REF_CLK2_125M_N

PS_MGTREFCLK2N_505_AC38

AC38

31

OUT2

GTR_REF_CLK3_150M_P

PS_MGTREFCLK3P_505_AA37

AA37

30

OUT2b

GTR_REF_CLK3_150M_N

PS_MGTREFCLK3N_505_AA38

AA38

35

OUT3

PL_DDR4_0_CLK_300MHZ_P

IO_L11P_T1U_N8_GC_64_AU21

AU21

34

OUT3b

PL_DDR4_0_CLK_300MHZ_N

IO_L11N_T1U_N9_GC_64_AV21

AV21

38

OUT4

PL_HD_BANK_CLK_P

IO_L5N_HDGC_AD7N_93_G7

G7

37

OUT4b

PL_HD_BANK_CLK_N

IO_L5P_HDGC_AD7P_93_F7

F7

42

OUT5

B128_REFCLK1P

MGTREFCLK0P_128_AB34

AB34

41

OUT5b

B128_REFCLK1N

MGTREFCLK0N_128_AB35

AB35

45

OUT6

B129_REFCLK1P

MGTREFCLK0P_129_W32

W32

44

OUT6b

B129_REFCLK1N

MGTREFCLK0N_129_W33

W33

51

OUT7

B130_REFCLK1P

MGTREFCLK0P_130_R32

R32

50

OUT7b

B130_REFCLK1N

MGTREFCLK0N_130_R33

R33

54

OUT8

B131_REFCLK1P

MGTREFCLK0P_131_L32

L32

53

OUT8b

B131_REFCLK1N

MGTREFCLK0N_131_L33

L33

Table 11. Signal assignment of 12-CH CLK Generator [U7]

DaisyPlus Board User Guide

16 CRZ Technology

5.2. 12-CH Clock Generator[U8]

Part Manufacturer : Silicon Labs

Part Number : Sl5391

Device

Pin

Pin Name

Schematic Net Name

Pin Name

Pin

Device

U8

23

OUT0b

B224_REFCLK_N

MGTREFCLK0N_224_AK11

AK11

U1

24

OUT0

B224_REFCLK_p

MGTREFCLK0P_224_AK12

AK12

20

OUT0Ab

B225_REFCLK_N

MGTREFCLK0N_225_AH11

AH11

21

OUT0A

B225_REFCLK_P

MGTREFCLK0P_225_AH12

AH12

27

OUT1b

B226_REFCLK_N

MGTREFCLK0N_226_AF11

AF11

28

OUT1

B226_REFCLK_P

MGTREFCLK0P_226_AF12

AF12

30

OUT2b

B227_REFCLK_N

MGTREFCLK0N_227_AD11

AD11

31

OUT2

B227_REFCLK_P

MGTREFCLK0P_227_AD12

AD12

34

OUT3b

B228_REFCLK_N

MGTREFCLK0N_228_AB11

AB11

35

OUT3

B228_REFCLK_P

MGTREFCLK0P_228_AB12

AB12

41

OUT5b

B229_REFCLK_N

MGTREFCLK0N_229_Y11

Y11

42

OUT5

B229_REFCLK_P

MGTREFCLK0P_229_Y12

Y12

50

OUT7b

B230_REFCLK_N

MGTREFCLK0N_230_V11

V11

51

OUT7

B230_REFCLK_P

MGTREFCLK0P_230_V12

V12

55

OUT9b

B231_REFCLK_N

MGTREFCLK0N_231_T11

T11

56

OUT9

B231_REFCLK_P

MGTREFCLK0P_231_T12

T12

37

OUT4b

EXP_B228_REFCLK_N

B_B228_CLKN

35

J25

38

OUT4

EXP_B228_REFCLK_P

B_B228_CLKP

33

44

OUT6b

EXP_B229_REFCLK_N

36

36

45

OUT6

EXP_B229_REFCLK_P

34

34

53

OUT8b

EXP_B230_REFCLK_N

B_B230_CLKN

107

54

OUT8

EXP_B230_REFCLK_P

B_B230_CLKP

105

58

OUT9Ab

EXP_B231_REFCLK_N

108

108

59

OUT9A

EXP_B231_REFCLK_P

106

106

Table 12. Signal assignment of 12-CH CLK Generator[U8]

DaisyPlus Board User Guide

CRZ Technology 17

6. MPSoC System Connections

6.1. NOR Flash 1GBIT [U9, U10]

Device

Pin

Pin Name

Schematic Net

Name

Pin Name

Pin

Device

U1

AM33

PS_MIO0_AM33

QSPI_LWR_CS_B

S_N

7

U9

AM29

PS_MIO1_AM29

QSPI_LWR_CLK

C

16

AM31

PS_MIO2_AM31

QSPI_LWR_DQ1

DQ1

8

AM30

PS_MIO3_AM30

QSPI_LWR_DQ2

W_N/VPP/DQ2

9

AL33

PS_MIO4_AL33

QSPI_LWR_DQ3

HOLD_N/DQ3

1

AL32

PS_MIO5_AL32

QSPI_LWR_DQ0

DQ0

15

AL30

PS_MIO10_AK30

QSPI_UPR_CS_B

S_N

7

U10

AK33

PS_MIO11_AK32

QSPI_UPR_CLK

C

16

AK34

PS_MIO12_AJ34

QSPI_UPR_DQ0

DQ1

8

AK30

PS_MIO7_AL30

QSPI_UPR_DQ1

W_N/VPP/DQ2

9

AK32

PS_MIO8_AK33

QSPI_UPR_DQ2

HOLD_N/DQ3

1

AJ34

PS_MIO9_AK34

QSPI_UPR_DQ3

DQ0

15

Table 13. Signal assignment of NOR Flash 1GBIT [U9, U10]

6.2. Dual NVME M.2

6.2.1. NVME0[J25]

Device

Pin

Pin Name

Schematic Net Name

Pin

Name

Pin

Device

U1

AD4

MGTHRXP0_228_AD4

B228_RX0P

PERP0

9

J25

AD3

MGTHRXN0_228_AD3

B228_RX0N

PERN0

11

AC2

MGTHRXP1_228_AC2

B228_RX1P

PERP1

15

AC1

MGTHRXN1_228_AC1

B228_RX1N

PERN1

17

AB4

MGTHRXP2_228_AB4

B228_RX2P

PERP2

21

AB3

MGTHRXN2_228_AB3

B228_RX2N

PERN2

23

AA2

MGTHRXP3_228_AA2

B228_RX3P

PERP3

27

AA1

MGTHRXN3_228_AA1

B228_RX3N

PERN3

29

AC6

MGTHTXP0_228_AC6

B228_TX0P

PETP0

10

DaisyPlus Board User Guide

18 CRZ Technology

AC5

MGTHTXN0_228_AC5

B228_TX0N

PETN0

12

AB8

MGTHTXP1_228_AB8

B228_TX1P

PETP1

16

AB7

MGTHTXN1_228_AB7

B228_TX1N

PETN1

18

AA6

MGTHTXP2_228_AA6

B228_TX2P

PETP2

22

AA5

MGTHTXN2_228_AA5

B228_TX2N

PETN2

24

Y8

MGTHTXP3_228_Y8

B228_TX3P

PETP3

28

Y7

MGTHTXN3_228_Y7

B228_TX3N

PETN3

30

U8

38

OUT4

EXP_B228_REFCLK_P

REFCLKP

33

37

OUT4b

EXP_B228_REFCLK_N

REFCLKN

35

U1

AB12

MGTREFCLK0P_228_AB12

B228_REFCLK_P

OUT3

35

U8

AB11

MGTREFCLK0N_228_AB11

B228_REFCLK_N

OUT3b

34

B3

IO_L10P_AD10P_94_B3

GT_EXP_1_IO4

PERSTn

64

J25

D4

IO_L5P_HDGC_94_D4

GT_EXP_1_IO14

CONFIG_1

76

Table 14. Signal assignment of NVME0 M.2 [J25]

6.2.2. NVME1[J25]

Device

Pin

Pin Name

Schematic Net Name

Pin

Name

Pin

Device

U1

T4

MGTHRXP0_230_T4

B230_RX0P

PERP0

81

J25

T3

MGTHRXN0_230_T3

B230_RX1P

PERN0

83

R2

MGTHRXP1_230_R2

B230_RX0N

PERP1

87

R1

MGTHRXN1_230_R1

B230_RX2P

PERN1

89

P4

MGTHRXP2_230_P4

B230_RX1N

PERP2

93

P3

MGTHRXN2_230_P3

B230_RX2N

PERN2

95

N2

MGTHRXP3_230_N2

B230_RX3N

PERP3

99

N1

MGTHRXN3_230_N1

B230_RX3P

PERN3

101

R6

MGTHTXP0_230_R6

B230_TX0P

PETP0

82

R5

MGTHTXN0_230_R5

B230_TX0N

PETN0

84

P8

MGTHTXP1_230_P8

B230_TX1P

PETP1

88

P7

MGTHTXN1_230_P7

B230_TX1N

PETN1

90

N6

MGTHTXP2_230_N6

B230_TX2P

PETP2

94

N5

MGTHTXN2_230_N5

B230_TX2N

PETN2

96

M8

MGTHTXP3_230_M8

B230_TX3P

PETP3

100

DaisyPlus Board User Guide

CRZ Technology 19

M7

MGTHTXN3_230_M7

B230_TX3N

PETN3

102

U8

54

OUT8

EXP_B230_REFCLK_P

REFCLKP

105

53

OUT8b

EXP_B230_REFCLK_N

REFCLKN

107

U1

V12

MGTREFCLK0P_230_V12

B230_REFCLK_P

OUT7

5

U8

V11

MGTREFCLK0N_230_V11

B230_REFCLK_N

OUT7b

50

A3

IO_L10N_AD10N_94_A3

GT_EXP_1_IO5

PERSTn

66

J25

D3

IO_L5N_HDGC_94_D3

GT_EXP_1_IO15

CONFIG_1

78

Table 15. Signal assignment of NVME1 M.2 [J25]

6.3. QSFP28 100G Ethernet

6.3.3. QSFP0 [J20]

Device

Pin

Pin Name

Schematic Net Name

Pin

Name

Pin

Device

U1

N29

PS_MIO35_N29

QSFP1_MODSELL

MODSELL

8

J20

T27

PS_MIO36_T27

QSFP1_RESETL

RESETL

9

N30

PS_MIO37_N30

QSFP1_MODPRSL

MODPRSL

27

R27

PS_MIO38_R27

QSFP1_INTL

INTL

28

P29

PS_MIO39_P29

QSFP1_LPMODE

LPMODE

31

AJ32

PS_MIO14_AJ32

PS_I2C0_SCL

SCL

11

AD35

PS_MIO15_AD35

PS_I2C0_SDA

SDA

12

L41

MGTYRXP0_130_L41

QSFP1_RX1_P

RX1P

17

L42

MGTYRXN0_130_L42

QSFP1_RX1_N

RX1N

18

K39

MGTYRXP1_130_K39

QSFP1_RX2_P

RX2P

22

K40

MGTYRXN1_130_K40

QSFP1_RX2_N

RX2N

21

J41

MGTYRXP2_130_J41

QSFP1_RX3_P

RX3P

14

J42

MGTYRXN2_130_J42

QSFP1_RX3_N

RX3N

15

H39

MGTYRXP3_130_H39

QSFP1_RX4_P

RX4P

25

H40

MGTYRXN3_130_H40

QSFP1_RX4_N

RX4N

24

M34

MGTYTXP0_130_M34

QSFP1_TX1_P

TX1P

36

M35

MGTYTXN0_130_M35

QSFP1_TX1_N

TX1N

37

L36

MGTYTXP1_130_L36

QSFP1_TX2_P

TX2P

3

L37

MGTYTXN1_130_L37

QSFP1_TX2_N

TX2N

2

K34

MGTYTXP2_130_K34

QSFP1_TX3_P

TX3P

33

DaisyPlus Board User Guide

20 CRZ Technology

K35

MGTYTXN2_130_K35

QSFP1_TX3_N

TX3N

34

J36

MGTYTXP3_130_J36

QSFP1_TX4_P

TX4P

6

J37

MGTYTXN3_130_J37

QSFP1_TX4_N

TX4N

5

Table 16. Signal assignment of QSFP0 [J20]

6.3.4. QSFP1 [J23]

Device

Pin

Pin Name

Schematic Net Name

Pin

Name

Pin

Device

U1

P28

PS_MIO40_P28

QSFP2_LPMODE

MODSELL

8

J23

P30

PS_MIO41_P30

QSFP2_RESETL

RESETL

9

T30

PS_MIO42_T30

QSFP2_MODSELL

MODPRSL

27

R30

PS_MIO43_R30

QSFP2_INTL

INTL

28

R29

PS_MIO44_R29

QSFP2_MODPRSL

LPMODE

31

AJ31

PS_MIO16_AJ31

PS_I2C1_SCL

SCL

11

AJ30

PS_MIO17_AJ30

PS_I2C1_SDA

SDA

12

G41

MGTYRXP0_131_G41

QSFP2_RX1_P

RX1P

17

G42

MGTYRXN0_131_G42

QSFP2_RX1_N

RX1N

18

F39

MGTYRXP1_131_F39

QSFP2_RX2_P

RX2P

22

F40

MGTYRXN1_131_F40

QSFP2_RX2_N

RX2N

21

E41

MGTYRXP2_131_E41

QSFP2_RX3_P

RX3P

14

E42

MGTYRXN2_131_E42

QSFP2_RX3_N

RX3N

15

D39

MGTYRXP3_131_D39

QSFP2_RX4_P

RX4P

25

D40

MGTYRXN3_131_D40

QSFP2_RX4_N

RX4N

24

H34

MGTYTXP0_131_H34

QSFP2_TX1_P

TX1P

36

H35

MGTYTXN0_131_H35

QSFP2_TX1_N

TX1N

37

G36

MGTYTXP1_131_G36

QSFP2_TX2_P

TX2P

3

G37

MGTYTXN1_131_G37

QSFP2_TX2_N

TX2N

2

F34

MGTYTXP2_131_F34

QSFP2_TX3_P

TX3P

33

F35

MGTYTXN2_131_F35

QSFP2_TX3_N

TX3N

34

E36

MGTYTXP3_131_E36

QSFP2_TX4_P

TX4P

6

E37

MGTYTXN3_131_E37

QSFP2_TX4_N

TX4N

5

Table 17. Signal assignment of QSFP1 [J23]

Table of contents