DV-605/DVF-R5060-S

9

CIRCUIT DESCRIPTION

Pin No. Pin Name I/O Description

38 CLK I The system clock input. all other inputs are registered to the SDRAM on

the rising edge of CLK.

37 CKE - Controls internal clock signal and when deactivated, the SDRAM will be

one of the states among power down, suspend or self refresh.

19 CS - Enables or disables all inputs except CLK, CKE, and DQM.

20,21 BA0,BA1 - Selects bank to be activated during RAS activity.

Selects bank to be read/written during CAS activity.

22~26 Row address : RA0~RA11, Column address : CA0~CA7

29~35 A0~A11 - Auto-precharge flag : A10

16,17,18 WE,CAS,RAS - WE, CAS and RAS define the operation.

15,39 LDQM,UDQM I/O Controls output buffers in read mode and masks input data in write mode.

2,4,5,7,8,10,11,

13,42,44,45,47, DQ0~DQ15 I/O Multiplexed data input/output pin.

48,50,51,53

1,3,9,14,27,

43,49 VCC/VCC Q - Power supply for internal circuits and input buffers.

6,12,28,41,

46,52,54 VSS/VSS Q - Ground terminal.

36,40 NC - Unused.

2-3 64 Bit SDRAM : HY57V651620B (Main, IC31)

Pin No. Pin Name I/O Description

1~8, 16~25,48 A0~A18 I Address Inputs

29,31,33,35,

38,40,42,44 DQ0~DQ7 I/O Data Input/Outputs, Command Inputs

30,32,34,36,

39,41,43 DQ8~DQ14 I/O Data Input/Outputs

45 DQ15 I/O Data Input/Outputs or Address input

26 CE - Chip Enable

28 QE - Output Enable

11 WE - Write Enable

12 RP - Reset/Block Temporary Unprotect

15 RY/BY O Ready/Busy/Output

47 BYTE - Byte/Word Organization

37 VCC - Supply Voltage

27,46 VSS - Ground

2-4 Flash Memory : M29W800AT(Main, IC41)

Pin No. Pin Name I/O Pin Description

1,3,5,9,11,13 A0 to A5 I Data Inputs

2,4,6,8,10,12 Q0 to Q5 O Data Outputs

7 GND - Ground

14 VCC - Positive Supply Voltage

AQ

LH

HL

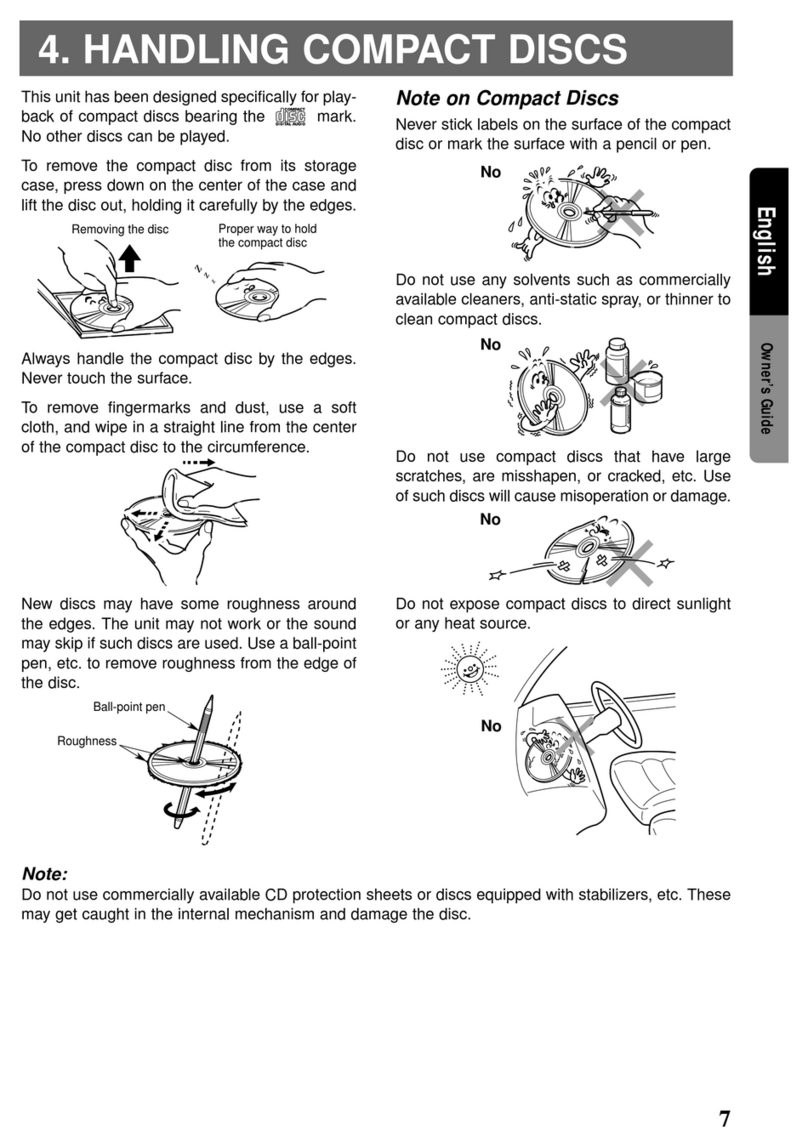

2-5 HEX Inverter (Single Stage) : M74HCU04(IC51) Truth Table