M68EM05P18UM/D

MOTOROLA Table of Contents 7

Table of Contents

General

Description Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

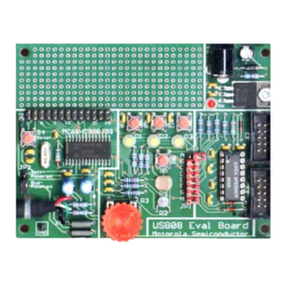

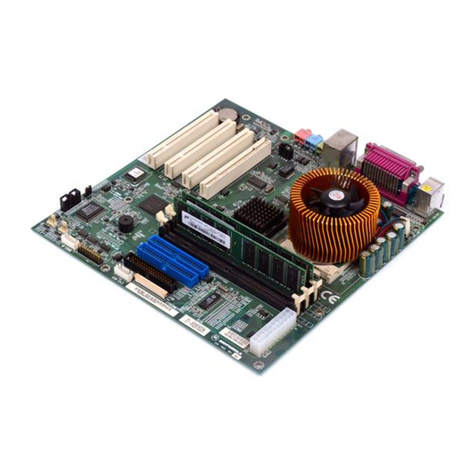

Emulation Components. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

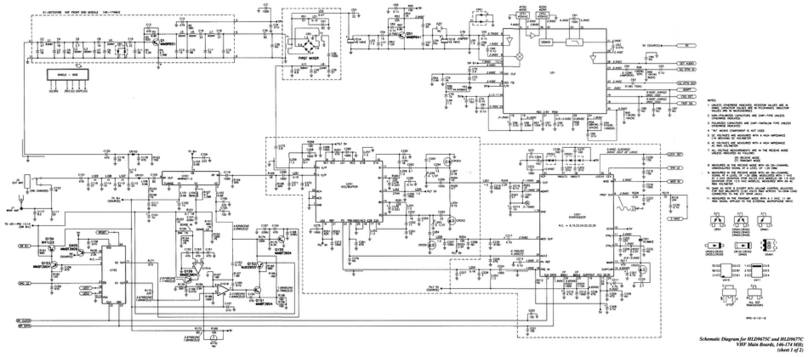

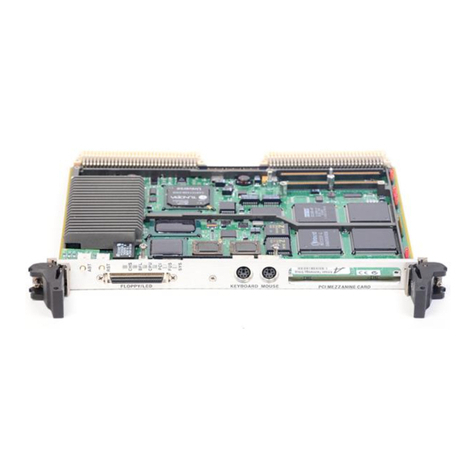

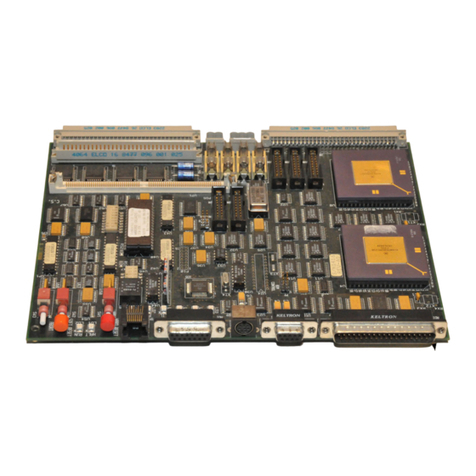

Emulation Module Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Target Cable Assemblies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Connector Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Target Cable Connector Pin Assignments . . . . . . . . . . . . . . . . . . .15

Logic Analyzer Connector Pin Assignments. . . . . . . . . . . . . . . . . .17

MMDS/MMEVS

Configuration

and Operation

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

Setting M68EM05P18 Jumper Headers and Switches . . . . . . . . . . . .21

Clock Source Select Header, W1 . . . . . . . . . . . . . . . . . . . . . . . . . .22

Reset Select Header, W2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

Port A Interrupt Mask Option Control Switch, SW1. . . . . . . . . . . . .24

Remaining System Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Personality File Usage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

MC68HC(8)05P18 Emulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Mask Option Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Port A Pullups/ Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Port C Bit 7 Sharing with the A/D Subsystem. . . . . . . . . . . . . . . . .29

Programming the 128-Byte EEPROM Array. . . . . . . . . . . . . . . . . .29

HC05EVS

Configuration

and Operation

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

Setting M68EM05P18 Jumper Headers and Switches . . . . . . . . . . . .33

Clock Source Select Header, W1 . . . . . . . . . . . . . . . . . . . . . . . . . .34

Reset Select Header, W2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

Interrupt Mask Control Switch, SW1. . . . . . . . . . . . . . . . . . . . . . . .36

Remaining System Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37