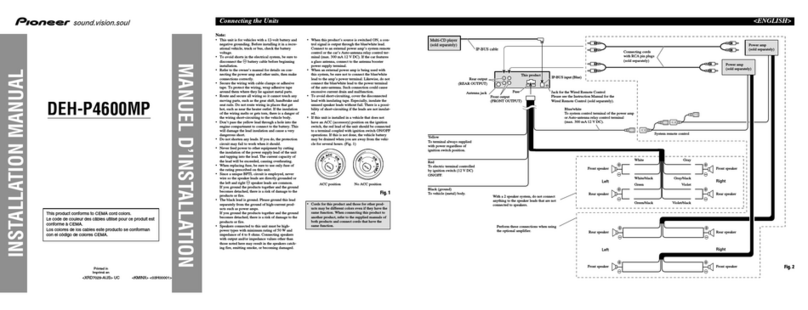

Primare CDI10 User manual

PRIMARE

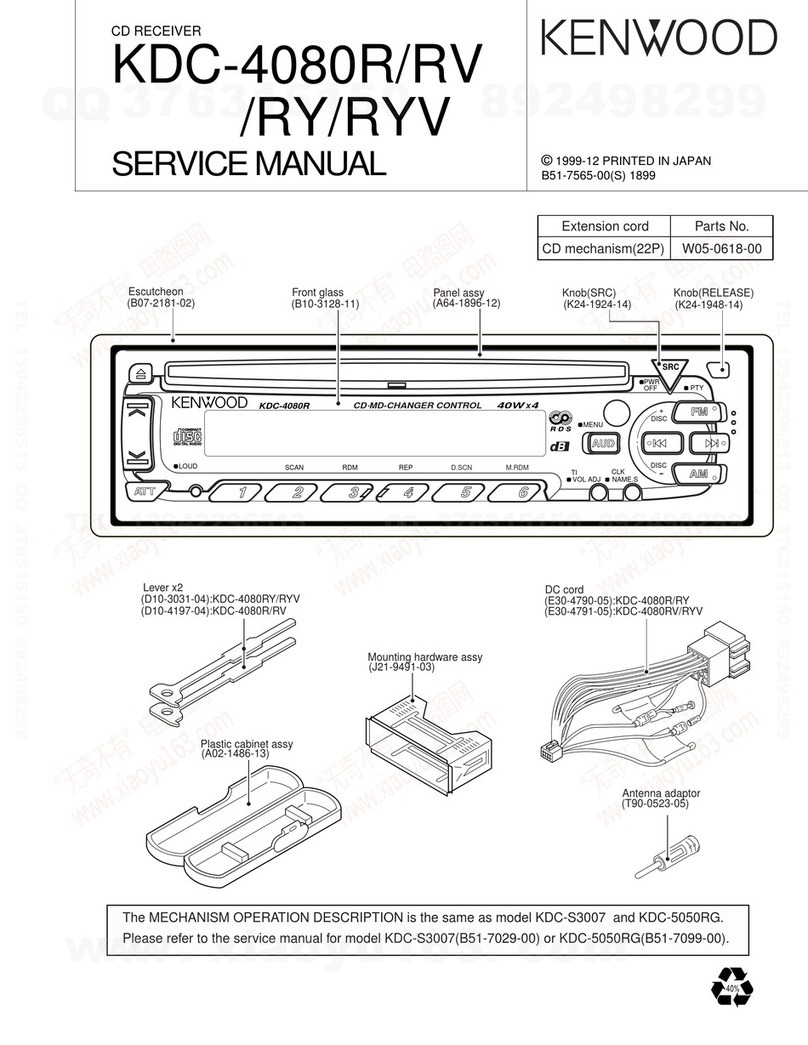

CDI 10 CD Receiver

Service Manual

1. Schematics and Pcb.

2. Technical Specifications.

Confidential !

This document is not allowed to show for third part without written permission

from Primare Systems AB.

This document is subject to change without notice.

Author:

Bjorn Holmqvist

Primare AB

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

审核:

文件编号:

硬件版本:

CDI10

1/1

页次:

文件名称:

拟制:

2005-08

DAB板原理图

日期:

主机型号:

DAB_POWER

DAB_SPDIF

DAB_RXD

DAB_TXD DAB_RXD

DAB_TXD

DAB_POWER

DAB_SPDIF

DAB_POWER

DAB_SPDIF

DAB_TXDDAB_TXD

DAB_VCC DAB_V5 DAB_V33

DAB_VCC DAB_VCC

DAB_V5 DAB_V5DAB_V33 DAB_V33

2R4 4K7

2U1 APL1117

3 2

1

IN OUT

GND

2C6 103

2R7 OPEN

2R1 33

2Q1

2N3904

+

2C4

100uF

2L2 FBSMT

2C3

104

2L1 FBSMT

DAB

HEADER 22X2

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

41 42

43 44

2R6 OPEN

2R3 33

2U1 IRF7304

1

3

2

4 5

6

7

8

2JP1

HEADER 7X2

12 34 56 78 910 1112 1314

2C5 103

+

2C3

100uF

2C7 103

2R5

4K7

2R3 33

2C9 OPEN

2C1

104

2C8 103

2R8 10

A

A

B

B

C

C

D

D

E

E

4 4

3 3

2 2

1 1

拟制:

1/1

页次:

主机型号:

2005-08

前控板原理图

日期:

CDI10

审核:

文件名称:

文件编号:

硬件版本:

IR-IN

VFD_RST

VFD_TXD

165_DATA

165_CS

MAIN_SCL

165_CLK

MAIN_SDA

VFD_V33

D5V

VFD_V33

VFD_V33

VFD_V33

P5V

VFD_V33

VFD_V33

P5V D5V

P5V

VFD_V33

+33V

VFD_V33

D5V

D5V +33V

P5V

3R21

24K9

VFD

MN14016B

1

2

3

7

8

9

10

11

12

13

14

40

41

42

6

15

16

17

F-

F-

F-

VSS

VSS

VDD1

BK

LAT

GCP

SO2

SO1

F+

F+

F+

VDD2

CLK

SI1

SI2

3R22

1K

3U3 APL1117

3 2

1

IN OUT

GND

3C13

104

3R26

180

3C10

104

3R19 1R

3R13 33

3R20 1R

+

3C1

10uF

3R11 33

3C8

104

3R15 4K7

3R16 4K7

3R5

4K7

3R17 4K7

+

3C9

10uF

3R6

4K7

3C4

104

3L1 FBSMT

3JP1

HEADER 7X2

1 2

3 4

5 6

7 8

9 10

11 12

13 14

3R18 4K7

3C18 104

3C16 104

3R25 OPEN

3L4 NI6A151

3L3

FBSMT

3R14

FBSMT

3R1 33

3L2 FBSMT

3U2

P89LPC932A1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

P2.0

P2.1

P0.0

P1.7

P1.6

RST

VSS

XT1

XT2

INT1

SDA

SCL

MOSI

MISO

SS

SPICLK

RXD

TXD

P0.7

P0.6

VDD

P0.5

P0.4

P0.3

P0.2

P0.1

P2.6

P2.7

+

3C3

10uF

3R24 10

3R2

47K

3R4

4K7

3C17 104

+

3C11

47uF 3C12

221

4R11 4K7

3C2

104

Q1

2N3904

HT82-60

3U1

1

2

3

+

3C6

47uF

3U4

MC34063

1

3

2

45

6

8

7SWC

CT

SWE

GNDOP

VCC

DCO

LPI

3C15

104

3R3 4K7

3JP2

PH-7A

1

2

3

4

5

6

7

3D1 EP05Q04

+

4C3

47uF

+

3C5

47uF

+

3C7

10uF

Q2

2N3906

3R23 OPEN

3C14

104

4R11

4K7

A

A

B

B

C

C

D

D

E

E

4 4

3 3

2 2

1 1

审核:

2/7

日期:

文件名称:

主机型号:

页次:

硬件版本:

拟制:

CDI10

主板原理图

文件编号:

2005-08

HD[0..15]

DA0

DRST#

DD3

DD5

DACS3#

DRD#

DD10

DD0

DD7

DA1

DD15

DACS1#

DIRQ

DD4

DD6

DD13

DWR#

DA2

DIOCS16#

DD1

DD2

DIORDY

DD11

HIORDY

DD14

DD9

DD8

LA10

LA8

LA13

LA14

LA12

LA18

LA16

LA11

LA19

LA15

LA9

LA4

LA2

LA9

LA5

LA16

LA17

LA11

LA10

LA13

LA15

LA3

LA8

LA0

LA6

LA12

LA7

LA1

LA14

DD0

DD1

DD2

DD3

DD4

DD5

DD6

DD7

DD8

DD9

DD10

DD11

DD12

DD13

DD14

DD15

DD12

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

DIRQ

DRST#

DWR#

DRD#

DIOCS16#

DACS1#

DACS3#

DA0

HIRQ

HRST#

HWR#

HRD#

HIOCS16#

HCS3#

HCS1#

HA0

DIORDY

DA2

DA1

HA2

HA1

LD1

LD2

LD6

LD4

LD5

LD0

LD3

LD7

LD[0..12]

LD0

LD1

LD2

LD3

LD4

LD5

LD6

LD7

LA19

LA7

LA18

LA2

LA3

LA0

LA6

LA1

LA4

LA5

LA[0..19]

LA17

HD[0..15]

HRST#

HWR#

HRD#

HCS1#

HIORDY

HCS3#

LA[0..19]

LD[0..12]

LCS3#

LOE#

ESS_RST#

WRLL#

LCS3#

HIRQ

HIOCS16#

HA0

HA2

HA1

LOE#

CD_POWER_ON

EVCCEVCC

VCC

EVCC

EVCC

VCC33

VCC33

EVCC EVCC

D+5V ESS_VCC

ESS_12VD+12V

ESS_VCC

ESS_12VESS_VCC

VCC33

VCC33

+

C1

470uF

R36 4K7

U6 APL1117

3 2

1

IN OUT

GND

C63 103C62 103

U11 IRF7304

1

3

2

4 5

6

7

8

R59 OPEN

+

C6

100uF

+

C8

10uF

Q6

2N3904

+

C66

1000uF

RB5 33X4 18 27 36 45

R103

4K7

JP2

HEADER 4

1

2

3

4

+

C41

470uF

JP2

HEADER-2X20

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

RESET GND

D7 D8

D6 D9

D5 D10

D4 D11

D3 D12

D2 D13

D1 D14

D0 D15

GND KEY

DRQ GND

IOW GND

IOR GND

IOCHRDY BALE

DACK GND

IRQ14 IOCS16

A1 RESERVED

A0 A2

CS0 CS1

ACTIVITY GND

+

C9

OPEN

FB1 B060

RB1 33X4 18 27 36 45

Q7

2N3904

RB6 33X4 18 27 36 45

R102

4K7

R58 10

R38 4K7

U3

27C080/OPE N

12

11

10

9

8

7

6

5

27

26

23

25

4

28

29

3

13

14

15

17

18

19

20

21

2

22

24

31

30

1

32

16

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

D0

D1

D2

D3

D4

D5

D6

D7

A16

CE

OE

A18

A17

A19

VCC

GND

U17 IRF7304

1

3

2

4 5

6

7

8

R1 33

C61 103

C128

104

+

C2

470uF

R2 33

C129

104

+

C40

1000uF

RB2 33X4 18 27 36 45

U4 MX29LV400CTTC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24 25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

A15

A14

A13

A12

A11

A10

A9

A8

NC

NC

WR

RST

NC

NC

NC

A18

A17

A7

A6

A5

A4

A3

A2

A1 A0

E

GND

G

DQ0

DQ8

DQ1

DQ9

DQ2

DQ10

DQ3

DQ11

VCC

DQ4

DQ12

DQ5

DQ13

DQ6

DQ14

DQ7

DQ15/A_1

GND

BYTE

A16

R39

10K

+

C42

470uF

R62 OPEN

R37

10K

RB3 33X4 18 27 36 45

R101 33

+

C39

1000uF

RB4 33X4 18 27 36 45

C7

104

C32 103

R60 OPEN

A

A

B

B

C

C

D

D

E

E

4 4

3 3

2 2

1 1

ES60x8

硬件版本:

拟制 : 审核 :

文件名称:

主机型号 :

文件编号 :

日期: 页次:

2005-08

1/7

CDI10

主板原理图

MA[0..11]

DB[0..15]

HD[0..15]

LD[0..12]

VD[0..7]

MA9

DMA3

LA18

MA4

LD7

DMA6

MA4

DB9

LD5

LA8

DB8

LA6

BANK0

MA8

DB12

MA7

MA3

DB2

DMA10 MA7

DMA0

DB1

DB14

MA2

MA5

DQMX

DB4

MA1

LA10

LD6

LA1

DB0

DB7

DB5

MA9

DB14

DB6

LA11

MA10

DMA8

DMA11

LD3

LD1

LA9

DB15

DMA4

DMA2

DMA9

DB7

MA11

DB3

LA12

MA5

MA6

DMA7

LA3

MA10

LA17

DB11

DB10

MA6

DB10

DB15

DB5

DB8

MA11

WE#

DMA1

LA15

BANK1

LA7

LD4

LA0

CKE

DB2

DB3

LA4

CS0#

MA0

MA8

DB13

CAS#

DB11

WRLL#

LCS3#

DB13

LA19

DB12

LA13

MA3

DB1

DB6

DB4

DB9

RAS0#

LA5

LA2

MA2

MA1

LA16

LD0

DB0

DMA5

LD2

LA14

MA0

HRD#

HD3

HWR#

HD0

HA1

HD2

HD7

HD6

HD1

HD4

HD5

HA2

HIRQ

HA0

HD9

HD10

HD11

HD13

HD14

HD15

HIORDY

HIOCS16#

HRST#

HCS3#

HCS1#

HD12

HD8

SDA#

DCLK

SCL#

/H_SYNC

/V_SYNC

27MHzXIN

DCAS#

DCKE

DWE#

DRAS0#

DQM

DMCK

DCS0#

TSD3#

TBCK#

SPDIF#

MCLK#

AUX7

AUX5

CLK_IN

CLK-IN

ESS_RST

LD8

LD9

LD10

LD11

TSD2#

TWS#

TSD1#

TSD0#

LD12

AUX4

AUX6

LA[0..19]

LOE#

HIRQ

HWR#

HRD#

HD[0..15]

HA[0..2]

HRST#

HCS1#

HIORDY

HIOCS16#

HCS3#

LA[0..19]

LCS3#

WRLL#

LOE#

LD[0..12]

VD[0..7]

27MHz

/H_SYNC

/V_SYNC

CLK-IN

27MHz

ESS_SPDIF

IR-IN

CLK-IN

AUX5

AUX6

AUX7

ESS_RST

VCC33

VCC33

VCC25

VCC33

VCC33

VCC33

VCC

VCC33 VCC33

VCC33

VCC VCC

AVCC

EVCC

VCC33

VCC25

AVCC AVCC

RB11 33X4

1 8

2 7

3 6

4 5

U1 ES6028

122

100

123

106

124

9

125

107

126

35

127

108

128

1

131

109

132

111

133

110

134

83

135

113

136

18

137

114

140

121

141

115

139

27

172

44

59

68

75

92

99

51

104

130

148

157

159

164

183

193

201

129

53

2

54

55

3

56

4

57

5

58

6

7

8

10

11

12

13

14

15

16

17

19

20

21

22

23

24

25

26

28

29

30

31

32

33

34

36

37

38

39

40

41

42

43

45

46

47

48

49

50

52

60

61

62

63

64

65

66

67

69

70

71

72

73

74

76

77

78

79

80

81

82

84

85

86

87

88

89

90

91

93

94

95

96

97

98

101

102

103

105

112

116

117

118

119

120

138

142

143

144

145

146

147

149

150

151

152

153

154

155

156

158

160

161

162

163

165

166

167

168

169

170

171

173

174

175

176

177

178

179

180

181

182

184

185

186

187

188

189

190

191

192

194

195

196

197

198

199

200

202

203

204

205

206

207

208

HD0/DCI[0]/EAUX1[0]

DCS0

HD1/DCI[1]/EAUX1[1]

YUV0/CAMYUV2

HD2/DCI[2]/EAUX1[2]

VC25

HD3/DCI[3]/EAUX1[3]

YUV1/VREF

HD4/DCI[4]/EAUX1[4]

VC25

HD5/DCI[5]/EAUX1[5]

YUV2/CDAC

HD6/DCI[6]/EAUX1[6]

VC33

HD7/DCI[7]/EAUX1[7]

YUV3/COMP

HD8/DCI_FDS/EAUX2[0]

AVCC(VDAC)

HD9/EAUX2[1]

YUV4/RSET

HD10/EAUX2[2]

VC25

HD11/EAUX2[3]

YUV5/YDAC

HD12/EAUX2[4]

VC33

HD13/EAUX2[5]

YUV6/VDAC

HD14/EAUX2[6]

VC25

HD15/EAUX2[7]

YUV7CAMYUV3

VC25

VC33

VC25

VC25

VC33

VC33

VC33

VC33

VC33

AVCC(PLL)

VC33

VC33

VC33

VC33

VC33

VC33

VC33

VC33

VC33

VSS

DMA0

LA4

DMA1

DMA2

LA5

DMA3

LA6

DMA4

LA7

DMA5

LA8

LA9

VSS

LA10

LA11

LA12

LA13

LA14

LA15

LA16

VSS

LA17

LA18

LA19

LA20

LA21

RESET

TDMDX/RSEL

VSS

TDMDR

T DMCLK

TDMFS

TDMTSC

TWS/SEL_PLL2

TSD0/SEL_PLL0

VSS

TSD1/SEL_PLL1

TSD2

TSD3

MCLK

TBCK

SPDIF/SEL_PLL3

NC/CAMVS

VSS

RSD

RWS

RBCK

NC/APLL

XIN

XOUT

AVSS( PLL)

VSS

DMA6

DMA7

DMA8

DMA9

DMA10

DMA11

VSS

DCAS

DSCK/DOE

DWE

DRAS0

DBANK0/DRAS1

DBANK1/DRAS2

VSS

DB0

DB1

DB2

DB3

DB4

DB5

VSS

DB6

DB7

DB8

DB9

DB10

DB11

VSS

DB12

DB13

DB14

DB15

DCS1

VSS

DQM

DSCK

VSS

CLK

AVSS( VDAC)

PCLK2XSCN/CAMYUV4

PCLKQSCN/CAMYUV5/AUX3[2]

VSSCN/CAMYUV6/EAUX3[1]

HSSCN/CAMYUV7/EAUX3[0]

VSS

VSS

HWRQ/DCI_REQ/EAUX4[1]

HRDQ/EAUX4[0]

HIRQ/DCI_ERR/EAUX4[7]

HRST/EAUX3[5]

HIORDY/EAUX3[3]

VSS

HWR/DCI_CLK/EAUX4[5]

HRD/DCI_ACK/EAUX4[6]

HIOCS16/CAMPCLK/EAUX3[4]

HCS1FX/EAUX3[7]

HCS3FX/EAUX3[6]

HA0/EAUX4[2]

HA1/EAUX4[3]

VSS

HA2/EAUX4[4]

AUX0

AUX1

AUX2

VSS

AUX3

AUX4

AUX5

AUX6

AUX7

LOE

VSS

LCS0

LCS1

LCS2

LCS3

VSS

LD0

LD1

LD2

LD3

LD4

VSS

LD5

LD6

LD7

LD8

LD9

LD10

LD11

VSS

LD12

LD13

LD14

LD15

LWRLL

LWRHL

VSS

CAMYUV0

CAMYUV1

LA0

LA1

LA2

LA3

VSS

R104 OPEN

C112

104

C120

104

RB8 33x4

1 8

2 7

3 6

4 5

R113

4K7 R107

4K7

C132

OPEN

RB13 33x4

1 8

2 7

3 6

4 5

+

C5

100uF

12

C122

104

R109

4K7

U5

24C01A

1

2

3

45

6

7

8S0

S1

S2

GNDSDA

SCL

WC

VCC

C102

104

R4

1K

C125

104

C124

104

C101

104

R8

FBSMT

R112

OPEN

C103

104

C131

OPEN

R3

1K

C115

104

C127

104

C126

104

Y1 OPEN

R7 33

C109

104

C104

104

RB10 33X4

1 8

2 7

3 6

4 5

C105

104

R108

OPEN

C118

104

C106

104

C12

104

L101 FBSMT

C107

104

R110

OPEN

C108

104

+

C4

100uF

12

C110

104

+

C11

100uF

12

RB7 33x4

1 8

2 7

3 6

4 5

C113

104

Q1

8050

2

13

C123

104

C111

104

+

C10

100uF

12

C113

104

C114

104

R114

OPEN R106

OPEN

C117

104

X1

OSC 27MHz

5

1

8

4

OUT

N/C

VCC

GND

RB12 33x4

1 8

2 7

3 6

4 5

C116

104

U2

4Mx16 SDRAM

1

2

4

6

5

7

3

8

10

12

11

13

9

15

16

17

18

19

35

22

23

24

25

26

14

28

29

30

31

32

33

34

36

37

38

39

40

43

42

44

46

45

47

49

48

50

52

51

53

41

20

21

27

54

VCC

DQ0

DQ1

VSSQ

DQ2

DQ3

VCCQ

DQ4

DQ5

VSSQ

DQ6

DQ7

VCCQ

DQML

WE

CAS

RAS

CS

A11

A10

A0

A1

A2

A3

VCC

VSS

A4

A5

A6

A7

A8

A9

NC

CKE

CLK

DQMH

NC

VCCQ

DQ8

DQ9

VSSQ

DQ10

DQ11

VCCQ

DQ12

DQ13

VSSQ

DQ14

DQ15

VSS

BA0

BA1

VCC

VSS

R111

4K7

+

C3

100uF

12

C119

104

R105

4K7

RB9 33X4

1 8

2 7

3 6

4 5

C121

104

A

A

B

B

C

C

D

D

E

E

4 4

3 3

2 2

1 1

文件名称:

日期:

硬件版本:

页次:

3/7

审核:

CDI10主机型号: 2005-08

拟制:

文件编号:

主板原理图

ESS_SPDIF

DAB_SPDIF

CS_DATA

CS_BCK

CS_LRCK

CS_RST

DAC_BCK

DAC_MCLK

12.288MHz

DAC_CS

DAC_CLK

DAC_DATA

DAC_TDS

DAC_LRCK

RST#

REC_L-OUT

REC_R-OU T

SPDIF_SEL 0

SPDIF_SEL 1

MAIN_ SDA

MAIN_S CL

SPDIF-IN

12.288MHz

RST#

12.288MHz

ESS_SPDIF

DAB_SPDIF

DAC_VCOM

RST#

DAC_CLK

DAC_R_IOUT+

DAC_CS

SPDIF_IN

RST#

DAC_L_IOUT+

DAC_R_IOUT-

DAC_DATA

DAC_L_IOUT-

AV33 AV33

AV33

IEC_VCC

AVCC

DAC_5V AVCC

DAC_V33

AV33

AVCC

AV33 AV33

AVCC

AV33AVCC IEC_VCC IEC_VCCIEC_VCC

1R8

16K

R53 33

R43

FBSMT

+

1C2

470uF

R49 FBSMT

1RB1 33x4

1 8

2 7

3 6

4 5

1C9

103

1X1

12.288MHz

5

1

8

4

OUT

N/C

VCC

GND

R57

100

C54

104

1R2 33

+

1C17 100uF

R41 33R50 33

L4 EMI

1

2

3

+

C44

100uF

U15

74ACT253

6

5

4

3

10

11

12

13

14

2

1

15

7

9

168

1C0

1C1

1C2

1C3

2C0

2C1

2C2

2C3

A

B

1G

2G

1Y

2Y

VCCGND

C45

104

1C4

104

+

1C19

100uF

U16C

74ACT125

98

10

1L2 4.7uH

R52 33

+

C53

100uF

1R5 33

D2 1N4148

RB23 33x4

1 8

2 7

3 6

4 5

R54

10

+

1C3

100uF

1R7 1K

D3 1N4148

+

C50

100uF C43

104

R51 FBSMT

R115 OPEN

1R1 FBSMT

R47

24K9 JP10 SHARP

1

2

3

IN

VCC

GND

R48

24K9 C52

104

1C18 104

1C12

104

R45

24K9

U13 CS8405

1

2

3

4

5

6

7

8

9

10

11

12

13

14 15

16

17

18

19

20

21

22

23

24

25

26

27

28

SDA

AD0/CS#

AD2

RXP

DGND2

VD

DGND4

DGND3

RST#

NC1

NC2

ILRCK

ISCLK

SDIN TCBL

NC3

NC4

NC5

INT

U

OMCK

DGND

VL+

H/S#

TXN

TXP

AD1/CDIN

SCLK

4U6 APL1117

3 2

1

IN OUT

GND

C130 103

1C14

104

R46

24K9

+

C51

100uF

U14 PCM1802

1

2

3

4

5

6

7

8

9

10 11

12

13

14

15

16

17

18

19

20

VINL

VINR

VREF1

VREF2

VCC

AGND

PDWN

BYPAS

FSYNC

LRCK BCK

DOUT

DGND

VDD

SCKI

OSR

FMT0

FMT1

MODE0

MODE1

1U1 DIR1703E

1

2

3

4

5

6

7

8

9

10

11

12

13

1415

16

17

19

20

21

22

23

24

25

26

18

27

28 ADFLG

BRATE0

BRATE1

SCKO

VDD

DGND

XTO

XTI

CKTRNS

LRCKO

BCKO

DOUT

SCF0

SCF1CSBIT

URBIT

EMFLG

BRSEL

DIN

RST

FILT

AGND

VCC

FMT0

FMT1

BFRAME

UNLOCK

CKSEL

+

C48

10uF

R42

47K

C58

100uF

1C16

104

C47

104

+

1C1

470uF

+

1C11

100uF

+

C49

10uF

1C8 104

+

C55

100uF

JP9

RCA

1

2

+

1C13

100uF

R44 33

U16B

74ACT125

56

4

+

C46

100uF

1C20

104

1R6 10

1C7

104

C57

104

R55 100

1C21

104

C56

104

C59

104

1C6

104

R56 300

1L1 4.7uH

1R4

1.18K

+

1C5

100uF

+

1C15

100uF

U16D

74ACT125

12 11

13

R40

FBSMT

U16A

74ACT125

23

1

1R2

FBSMT

1C10

683

1U2 PCM1738E

1

2

3

4

5

6

7

8

9

10

11

12

13

14 15

16

17

18

19

20

21

22

23

24

28

25

26

27

RST

ZEROL

ZEROR

LRCK

DATA

BCK

SCKI

DGND

VDD

SCKO

MDO

MDI

MC

CS MUTE

IOUTR-

IOUTR+

AGND1

VCOM1

VCOM2

IREF

VCOM3

VCC1

VCC2

VCC3

IOUTL+

IOUTL-

AGND2

A

A

B

B

C

C

D

D

E

E

4 4

3 3

2 2

1 1

文件名称:

日期:

硬件版本:

页次:

4/7

审核:

CDI10主机型号: 2005-08

拟制:

文件编号:

主板原理图

A-12V

A+12V

A+12V

A-12V

A-12V

A+12V

A-12V

A+12V

A+12V

A-12V

A-12V

A+12V

CD_L-OUT

A+12V

A-12V

A+12V

A-12V

CD_R-OUT

DAC_L-IOUT-

DAC_L-IOUT+

DAC_R-IOUT +

DAC-VCOM

DAC_R-IOUT-

CD_R-OUT

CD_L-OUT

DAC-VCOM

A+12V

A-12V

A+12V

A-12V

A+12V A+12V A+12V A+12V A+12V A+12V A+12V A-12V A-12V A-12V A-12V A-12V A-12V A-12VA+12V A-12V

1C29 272

1R31

10

1R10 620

1C25

104

1C110

101

1R25 4K7

1R38 1M

1Q1

BS170

+

1C26

100uF

1R29 300

1C38

152

1R11 620

1C27

104

1R12 620

1R16 620

1R37 1K

+

-

1U6A

OPA2134

3

21

8 4

1R33 3K9

+

1C24

100uF

1C37

682

1R22 620

1R35 4K7

1C31

104

1R19 620

1R32

33

1R13 620

1R39 300

1R24 620

1C22 272

1R41

10

1C39 152

1R20 620

1C23 272

1R18 620

1C33

104

1R21

620

1C35

152

+

1C50 10U 1R36

47K

+

1C32

100uF

1C52

100U/16V

1C42

104

1R23 620

+

1C44 10U

1R14 620

1R40

10

+

1C30

100uF

1C34

682

1C53

104

+

-

1U4A

NE5532

3

21

8 4

+

1C43

100uF

1R34 100

1R15

620

1C44

104

1C47

100U/16V

1C36 152

LED2

GREED 1R42

33

+

1C41

100uF

+

-

1U7A

OPA2134

3

21

84

1R17 620

+

-

1U4B

NE5532

5

67

84

1Q4

BC850B

1C46 10pF

1R43 3K9

1R44 100

1C48

104

1Q2

BC850B

1R26

47K

+

-

1Y7B

OPA2134

5

67

84

+

1C56

100uF 1C57

104

+

-

1U6A

OPA2134

3

21

8 4

1C45 1U/1160V

1C111

101

1R30

10

1R28 1M

LED1

GREED

+

-

1U5A

NE5532

3

21

8 4

1C51 10pF

1C28 272

1R9 620

+

1C54

100uF

+

-

1U5B

NE5532

5

67

84

1R27 1K

1Q3

BS170

1C55

104

1C49 1U/160V

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

页次:日期:

硬件版本:

文件名称:

主机型号:

5/7

审核:拟制:

2005-08

文件编号:

CDI10

主板原理图

CD_L-IN

CD_R-IN

AUX1_L-IN

AUX4_R-IN

AUX3_R-IN

AUX1_R-IN

AUX4_L-IN

AUX2_L-IN

AUX3_L-IN

AUDIO_L-IN

AUDIO_R-IN

A-12V

A+12V

A+12V

A-12V

A-12V

A+12V

A+12V

A-12V

A-12V

A-12V

AUX2_R-IN

REC_R-OUT

PRE_R-OUT

PRE_L-OUT

A-12V

A-12V

A+12V

A-12V

A+12V

A+12V

A+12V

A+12V

A-12V

A+12V

REC_L-OUT

CD_SEL

AUX4_SEL

AUX3_SEL

AUX2_SEL

AUX1_SEL

CD_R-IN

CD_L-IN

AUX4_R-IN

AUX4_L-IN

VOL_CLK

VOL_DATA

VOL_CS

REC_MUTE

PRE_MUTE

VOL_L-OUT

VOL_R-OUT

D12V

D12V

D12V

D12V

D12V

AVCC A-5VAVCC

D12V

D12V

VD5V

VD5V VD5V

1R74 10

1U10 PGA2311

1

2

3

4

5

6

7

8 9

10

11

12

13

14

15

16

ZCEN

/CS

SDI

VD+

DGND

SCLK

SDO

/MUTE VINR

AGND

VOUTR

VA+

VA-

VOUTL

AGND

VINL

+

-

1U11A

OPA2134

3

2

1

84

1R58

47K

1R80 0

1R78 1K

1R62

47K

1R68

1M

1C71

104

1R52 0

1R84

47K

1C75

104

1R66 1K

+

-

1U12A

OPA2134

3

2

1

84

+

1C74

100uF

1R45 1K

1R76

1M

1R70

10K

+

-

1U13A

OPA2134

3

21

84

1R65

1K

1R71 1K

1R72 1K

1C77

105

1KJ2 P-12

3

2

4

6

7

51

8

1R55

24K9

1D2

1N4148

1R75

1M

1C78 105

1KJ4 P-12

3

2

4

6

7

51

8

1C83

101

1R59

24K9

1R69

1M

1C85 105

1R60

24K9

1R85 0

1KJ5 P-12

3

2

4

6

7

51

8

1R56

24K9

1D5

1N4148

1KJ8 P-12

3

2

4

6

7

51

8

+

-

1U12B

OPA2134

5

67

84

+

-

1U13B

OPA2134

5

67

84

1R82 100

1R47 0

1KJ7 P-12

3

2

4

6

7

51

8

1C69

104

+

1C68

100uF

1R49 100

+

-

1U9B

OPA2134

5

67

8 4

+

-

1U9A

OPA2134

3

21

84

1D4

1N4148

1R54 100

+

-

1U8B

OPA2134

5

67

84

1D8

1N4148

1KJ1 P-12

3

2

4

6

7

51

81D1

1N4148

1R50 1K

1L4

4.7uH

1R57 10

1L3

4.7uH

1JP1 HPJ-246

1

2

3

4

5

6

7

8

9

1C84

105

1JP2 HPJ-244

1

2

3

4

5

6

1R83 1K

+

-

1U8A

OPA2134

3

21

84

1R67 10

1R77

10K

1R73

1K

1R61 10

+

-

1U11B

OPA2134

5

67

84

1C73

104

+

1C72

100uF

1D7

1N4148

1R63 1K

1C70

104

1R79

47K

1R87 100

1KJ3 P-12

3

2

4

6

7

51

81C76

101

1D3

1N4148

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

文件名称:

审核:

主板原理图

日期:

拟制:

6/7

主机型号: 硬件版本:2005-08

页次:

CDI10

文件编号:

A+12V

A-12V

A+12V

A-12V

AMP_L-OUT+

AMP_L-OUT-

AMP_MUTE

AMP_MUTE

A+12V

AMP_R-OUT+

A-12V

AMP_R-OUT-

A+12V

HP_R-OUT

HP_L-OUT

A-12V

VOL_L-OUT

AMP_MUTE

VOL_R-OUT

AMP_MUTE

PRE_L-OUT

AUX4_L-IN

AUX4_R-IN

PRE_R-OUT HP_AUX4_SEL

OPEN_KEY

POWER_ON

A-12V A-12VA-12V A-12VA-12V A-12VA-12VA-12V A-12VA-12VA-12VA-12VA-12V A-12V

AVCC

D12V

HPVCC HPVCC

A+12VA+12VA+12V A+12VA+12V A+12V A+12VA+12V A+12VA+12V A+12VA+12V A+12V A+12V

P10V A-12V A-5V D+5V DAB_VCC AVCC VFD_VCC D+12V A+12V

+

1C64

100uF

1C97

104

1R90 100

1C89

104

1C82

104

JP8

CP3524P1V00

12 34 56 78 910 1112 1314 1516 1718 1920 2122 2324

+

1C98

100uF

1R92 1K

+

-

1U16A

TDA1308T

3

21

84

+

1C112

2200uF

1C117 103

+

1C102

10uF

1C80

104

+

1C113

2200uF

1C93

104

1KJ6 P-12

3

2

4

6

7

51

8

+

-

1U14A

OPA2134

3

21

8 4

1R103 47K

1R101 47K

L6 47uH/3A

1R96 100

+

1C94

100uF

1C101

104

+

1C107 220uF

R61 10

1R97 1K

1R107 OPEN

+

1C96

100uF

+

1C115

1000uF

1R105

4K7

1R110

OPEN

1R91 1K

1C59

104

+

1C104

100uF

1R100 16K

+

1C106 220uF

+

1C90

100uF

1C105

104

+

1C86

100uF

1R109 OPEN

L5 47uH/3A

1C65

104

+

C37

2200uF

1L7 47uH/3A

1R111

OPEN

L8 47uH/3A C64 103

1JP4

CP3504P1V00

1

2

3

4

+

-

1U16B

TDA1308T

5

67

8 4

1C116 103

1R93 100

1R88 0

+

C38

2200uF

+

1C66

100uF

1L8 47uH/3A

+

1C100

100uF

1D6

1N4148

1C95

104

1R94 0

1C61

104

1L6 47uH/3A

+

1C92

100uF

1R102 16K

+

-

1U14B

OPA2134

5

67

84

JP6

XH-5A

1

2

3

4

5

1C118 103

1L5 47uH/3A

1C99

104

+

1C60

100uF

+

1C114

1000uF

L7 47uH/3A

+

1C58

100uF

1R99 100

1R89

OPEN

+

-

1U15B

OPA2134

5

67

84

1R106

10

1C87

104

+

1C79

100uF

1R104 4K7

+

C35

2200uF

1R95

OPEN

1JP3

CP3504P1V00

1

2

3

4

1R98 1K

1R108 OPEN

+

1C88

100uF

+

1C108

100uF

1C67

104

+

1C81

100uF

+

1C103

10uF

1C109

104

1R112

47

1C91

104

+

C36

2200uF

+

-

1U15A

OPA2134

3

21

8 4

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

文件名称:

日期:

硬件版本:

页次:

7/7

审核:

CDI10主机型号: 2005-08

拟制:

文件编号:

主板原理图

DAB_RXD

DAB_TXD

DAB_POWER

165_DATA

IR-IN

165_CLK

TXD1

TXD_SEL

VFD_TXD

165_CS

VFD_RST

IR2-IN

AUX7

AUX6

AUX5

AUX4

ESS_RST

RXD0

SPDIF_SEL0

TXD0

SPDIF_SEL1

MAIN_SDA

DAC_CS

DAC_CLK

DAC_DATA

#RST

VOL_CS

VOL_DATA

VOL_CLK

AUX1_SEL

AUX2_SEL

CD_SEL

AUX3_SEL

AUX4_SEL

REC_MUTE

PRE_MUTE

HP_AUX4_SEL

AMP_MUTE

CD_POWER_ON

POWER_ON

DAB_SPDIF

OPEN_KEY

MAIN_ SDA

MAIN_S CL

TXD0

RXD0

MAIN_SCL

P5V P5VP5V

PV33 PV33

PV33 PV33 P5V

DAB_VCCDAB_VCC

D5VD5VP5V P5V

P5V PV33P10V

P5V P5V

P5V P5V P5V PV 33 PV33 PV33 PV33 PV33 PV33

Q10

2N3904

C60

103

R22 33X4 18 27 36 45

+

C33

1000uF

R21 33X4 18 27 36 45

U18D 74LVC00

12

13

11

Q13

2N3904

C21

104

U18B 74LVC00

4

5

6

U18A 74LVC00

1

2

3

U18C 74LVC00

9

10

8

RB23 33X4 18 27 36 45

C31

104

R14 4K7 Q8

2N3904

R23

1K

C22

104

Q4

2N3906

+

C25

10uF

Q3

2N3906

R17 4K7

R10

47K

R24

4K7

+

C65

100uF

C131

22pF

JP7

HEADER 7X2

12 34 56 78 910 1112 1314

R33

4K7

R20 4K7

L3 EMI

1

2

3

R31

4K7

RB15 33X4

18 27 36 45

C23

104

R32 4K7

R27

4K7

R30

4K7

Q11

2N3904

+

C29

470uF

C34

104

Q14

2N3904

L1 EMI

1

2

3

C24

104

R15 4K7

R22

1K

RB16 33X4

18 27 36 45

U10 APL1117

3 2

1

IN OUT

GND

+

C13

100uF

C132

22pF

R18 4K7

R11 4K7

R9 1K

JP3

DB9-F

5

9

4

8

3

7

2

6

1

Q9

2N3904

R34

4K7

R21 4K7

C14

104

U12 7805

3 2

1

IN OUT

GND

RB18

33X4

18 27 36 45

Q2

2N3904

C67

104

JP5

HEADER 7X2

12 34 56 78 910 1112 1314

Q12

2N3904

U7

MAX232CSE

3

4

2

15

12

9

1

5

10

11

16

6

14

7

13

8

C1-

C2+

V+

GND

R1OUT

R2OUT

C1+

C2-

T2IN

T1IN

VCC

V-

T1OUT

T2OUT

R1IN

R2IN

R12

4K7

+

C30

470uF

R26

4K7

RB19

33X4

18 27 36 45

+

C30

1000uF

Q15

2N3904

R25

4K7

RB20

33X4

18 27 36 45

C20

104

JP4

HSJ-035-09A

5

4

3

2

1

R35

4K7

C15 105

R16 4K7

U9

24C01A

1

2

3

4 5

6

7

8

S0

S1

S2

GND SDA

SCL

WC

VCC

U8

LPC2132

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

P0.21

P0.22

RTXC1

P1.19

RTXC2

VSS

VDDA

P1.18

P0.25

P0.26

P0.27

P1.7

P0.28

P0.29

P0.30/EINT3

P1.16

P0.31

VSS

PO.0/TXD0

P1.31

P0.1/RXD0

P0.2/SCL0

VDD

P1.26

VVS

P0.3/SDA0

P0.4/SCK0

P1.25/EXTIN0

P0.5/MISO0

P0.6/MOSI0

P0.7/SSEL0

P1.24

P0.8/TXD1

P0.9/RXD1

P0.10

P1.23

P0.11/SCL1

P0.12

P0.13

P1.22

P0.14/SDA1

VSS

VDD

P1.21

P0.15/EINT2

P0.16/EINT0

P0.17/SCK1

P1.20

VBAT

VSS

VDD

P1.30

P0.18/MISO1

P0.19/MOSI1

P0.20/SSEL1

P1.29/TCK

RESET

P0.23

VSSA

P1.28/TDI

XTAL2

XTAL1

VREF

P1.27/TDO

C17 105

D1

1N4148

L2 EMI

1

2

3

C18 105

R28

33

C19

104

R19 4K7

RB17 33X4

18 27 36 45

C16

105

Y2

11.0592MHz

Q5

2N3904

R29

4K7

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

文件名称:

审核:

文件编号:

硬件版本:主机型号:

按键板原理图

拟制:

日期:

CDI10

页次:

2005-08

1/1

MAIN_SDA

MAIN_SCL

165_CLK

165_CS

165_DATA

OPEN_KEY

GND

HP_R-OUT

AGND

HP_L-OUT

P5V

P5V

P5V

P5V

P5VP5VP5VP5V

4U1

SAA1064T

1

2

3

4

5

6

7

8

9

10

11

1213

14

15

16

17

18

19

20

21

22

23

24 ADR

CEXT

P8

P7

P6

P5

P4

P3

P2

P1

MX1

VEEVCC

MX2

P9

P10

P11

P12

P13

P14

P15

P16

SDA

SCL

4LED5 DE2G

4

3

2

1

A2

K2

A1

K1

4R6

4K7

4R12 820

+

4C1

10uF

4R14 820 4R15 820

4R9

4K7 4R10

4K7 4R5

4K7

4LED4 DE2G

4

3

2

1

A2

K2

A1

K1

4C8 104

4R7

4K7

4R8

4K7

4R16 OPEN

4U2

74HC165

8

7

6

5

4

3

2

1

9

10

11

12

13

14

15

16

GND

/Q7

D7

D6

D5

D4

CLK

LD

Q7

DIN

D0

D1

D2

D3

/CE

VCC

4R11 820

4K4 4K1

+

4C3

10uF

4LED3 DE2G

4

3

2

1

A2

K2

A1

K1

4K3

4K7

4JP1

PH-7A

1

2

3

4

5

6

7

4LED1 DE2G

4

3

2

1

A2

K2

A1

K1

4C2

104

4K2

4JP4

XH-2A

1

2

4R13 820

4C7 104

4C4

104

4JP3

SCJ340

3

2

1

4LED2 DE2G

4

3

2

1

A2

K2

A1

K1

4JP2

XH-3A

1

2

3

4K6

4R17 10

4K5

CD_R_F1.job - Tue Jan 17 13:58:45 2006

CDRM3.job - Tue Jan 17 13:46:24 2006

CDRM3.job - Tue Jan 17 13:50:55 2006

Other manuals for CDI10

1

Table of contents

Other Primare Car Receiver manuals