7

ICD-B17

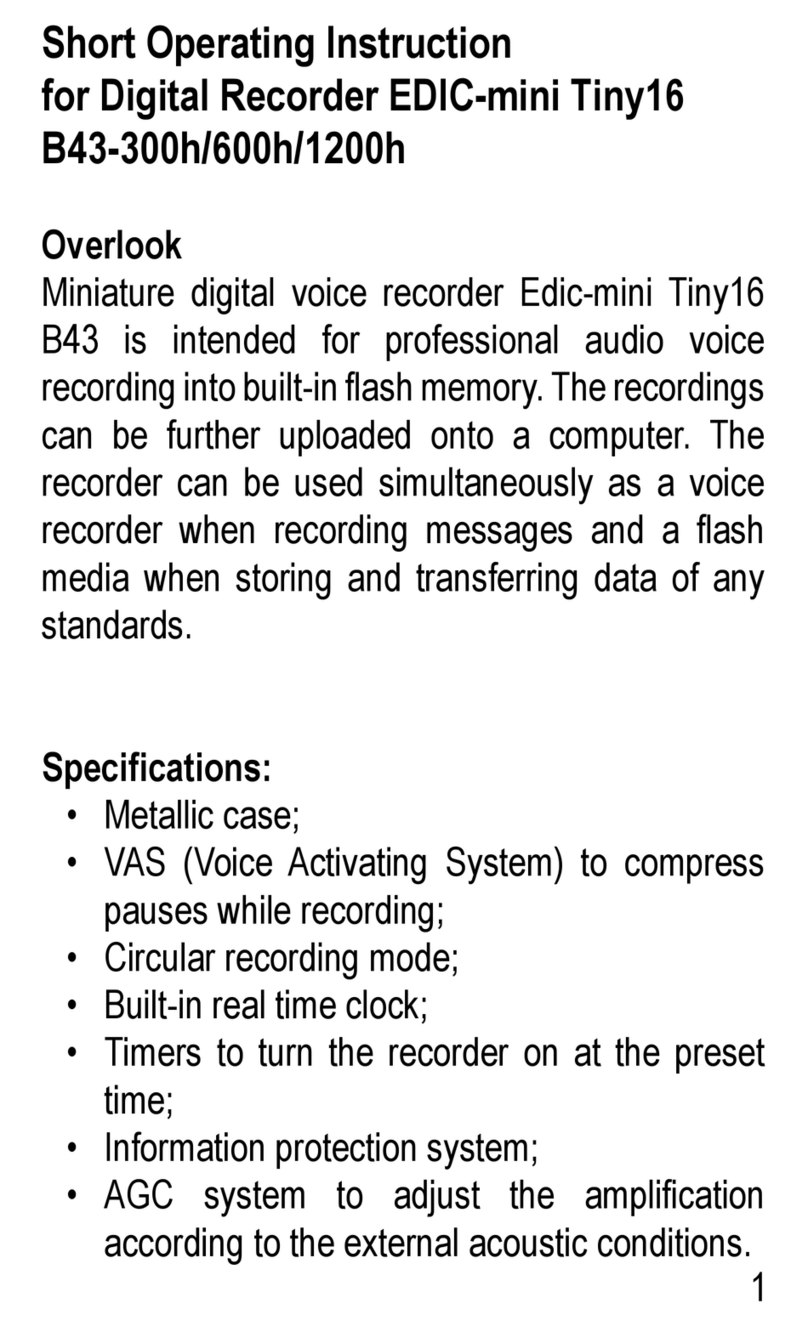

4-1. IC PIN DESCRIPTION

• IC703 µPD780308GC-A66-8EU (MEMORY CONTROL, SYSTEM CONTROL)

Pin No. Pin Name I/O Pin Description

1 – 3 KEY0 – KEY2 I Key signal input

4XHOLD I Hold switch signal input

5AMPPOW O Power down control signal output to the power amplifier IC (IC103)

6AVREFON I A/D reference voltage input

7 XFMCE O Chip enable signal output to the flash memory IC (IC701)

8VDD0 — Power supply pin (+3.3V)

9AVREF — A/D reference voltage

10 XFMWE O Write enable signal output to the flash memory IC (IC701)

11 XFMALE O ALE signal output to the flash memory IC (IC701)

12 VSS1 — Ground pin

13 XFMR/B I Ready/Busy signal input from the flash memory IC (IC701)

14 XFMCLE O CLE signal output to the flash memory IC (IC701)

15, 16 NC O Not used. (Open)

17 XFMRE O Read enable signal output to the flash memory IC (IC701)

18 XFMSE O SE signal output to the flash memory IC (IC701)

19 XFMWP O WP signal output to the flash memory IC (IC701)

20 CLKOUT O Not used in this set. (Open)

21 BEEP O Beep signal output (2.4 kHz)

22 LIGHT O LCD back light control output Not used in this set. (Open)

23 – 26 COM0 – COM3 O LCD common signal output

27 BIAS O Connect to VDD. (LCD bias)

28 – 30 VLC0 – VLC2 — LCD drive power supply pin

31 VSS0 — Ground pin

32 – 61 S0 – S29 O LCD segment signal output

62 NC I Not used. (Open)

63 NC O Not used. (Open)

64 XTEST I Test pin

65 DSPPOW O Digital signal processor registor control I/F enable signal output

66 LEDREC O OPR (REC) LED (D701: red) ON/OFF signal output

67 LEDPB O OPR (PLAY) LED (D701: green) ON/OFF signal output

68 RTCCE O Real time clock chip enable signal output

69 XDSPIFRQ O I/F request signal output to the DSP IC (IC101)

70 DSPIFRW O I/F data read/write signal output to the DSP IC (IC101)

71 XDSPRST O Reset signal output to the A/D, D/A converter, DSP IC (IC101)

72 SI0 I I/F data signal input to the DSP IC (IC101)

73 SO0 O I/F data signal output to the DSP IC (IC101)

74 SCK0 O I/F signal clock output to the DSP IC (IC101)

75 RTCDI I Real time clock data signal input

76 RTCDO O Real time clock data and digital signal processor registor control data output

77 RTCCLK O Real time clock I/F data and digital signal processor registor control clock output

78 IC — Connect to ground.

79 X2 O System clock output (5 MHz)

80 X1 I System clock input (5 MHz)

81 VDD1 — Power supply pin

82 XT1 — Sub clock input (32.768 kHz)

83 XT2 — Not used in this set. (Open)

84 XRESET I Reset signal input

85 NC — Not used. (Open)

SECTION 4

DIAGRAMS