┠ḟ

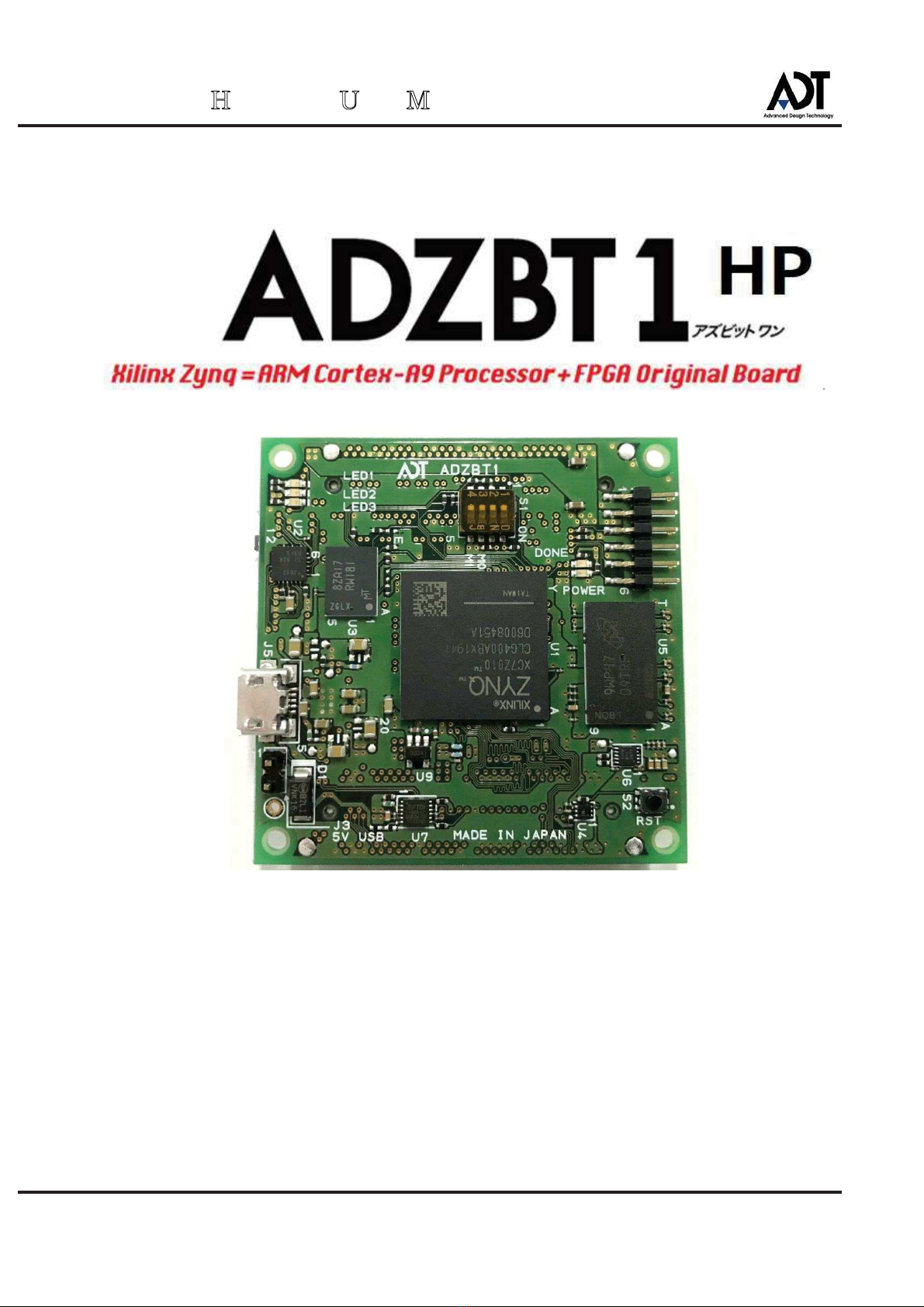

1Overview............................................................................................................................................. 4

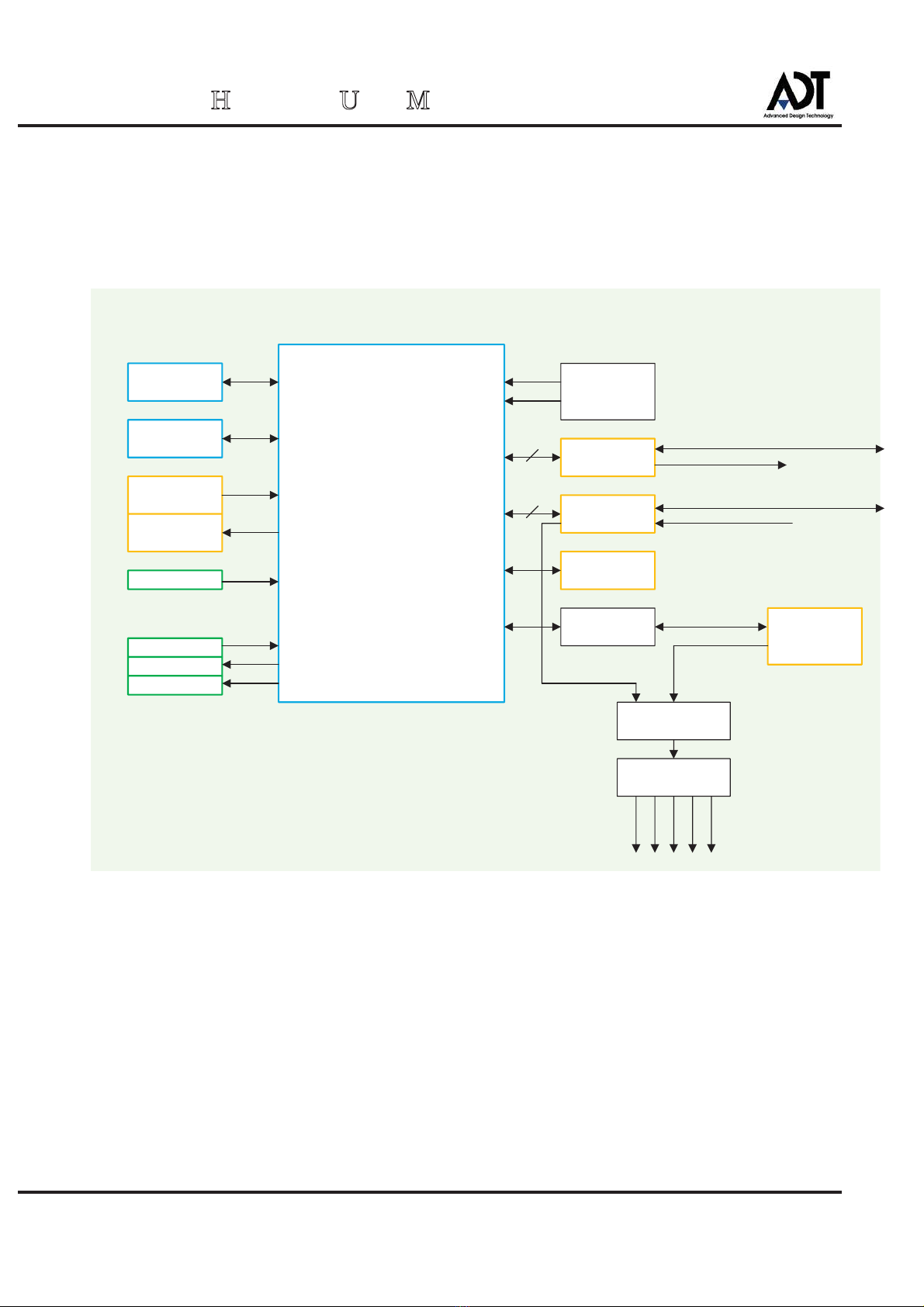

2Block Diagram ................................................................................................................................... 5

3ᶵ⬟ㄝ.............................................................................................................................................. 6

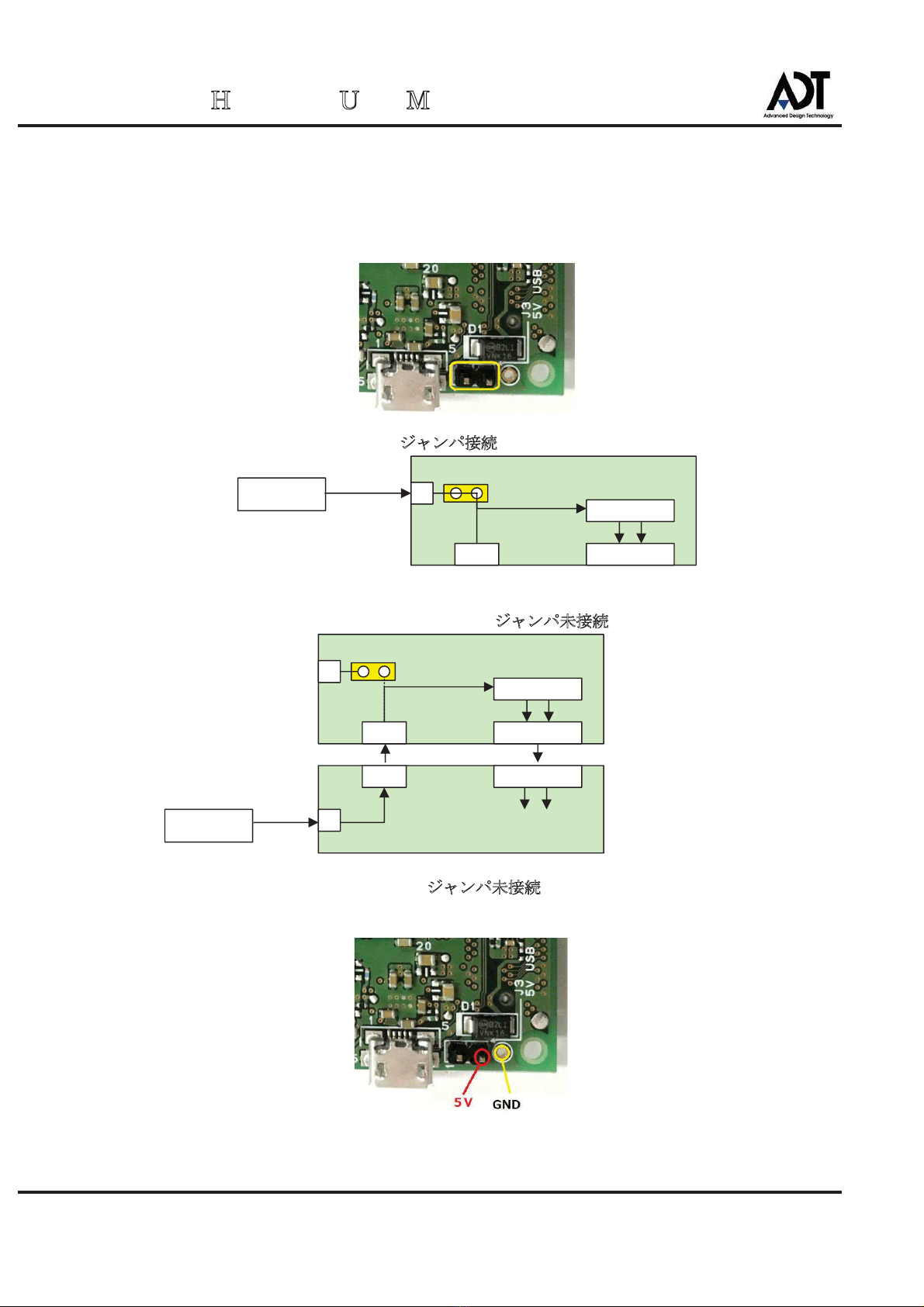

3.1Power Supply.............................................................................................................................. 7

3.2Zynq FPGA Configration ........................................................................................................... 8

3.3JTAG I/F.................................................................................................................................... 10

3.4QSPI Flash................................................................................................................................ 10

3.5DDR Memory ............................................................................................................................ 10

3.6USB Serial Port........................................................................................................................ 11

3.7MicroSD Slot............................................................................................................................. 11

3.8Clock Source ............................................................................................................................. 11

3.9User I/O..................................................................................................................................... 12

3.10LED ........................................................................................................................................... 15

3.11DIP SW...................................................................................................................................... 16

4Appendix .......................................................................................................................................... 17