Cyclone 10 LP RefKit User Guide www.arrow.com

Page | 2 February 2022

Table of Contents

Table of Figures ..................................................................................................................... 4

Cyclone 10 LP RefKit Development Board ............................................................. 5

1.1 About Arrow Cyclone 10 LP RefKit Board.........................................................................5

1.2 Useful Links.......................................................................................................................5

1.3 Getting Help......................................................................................................................6

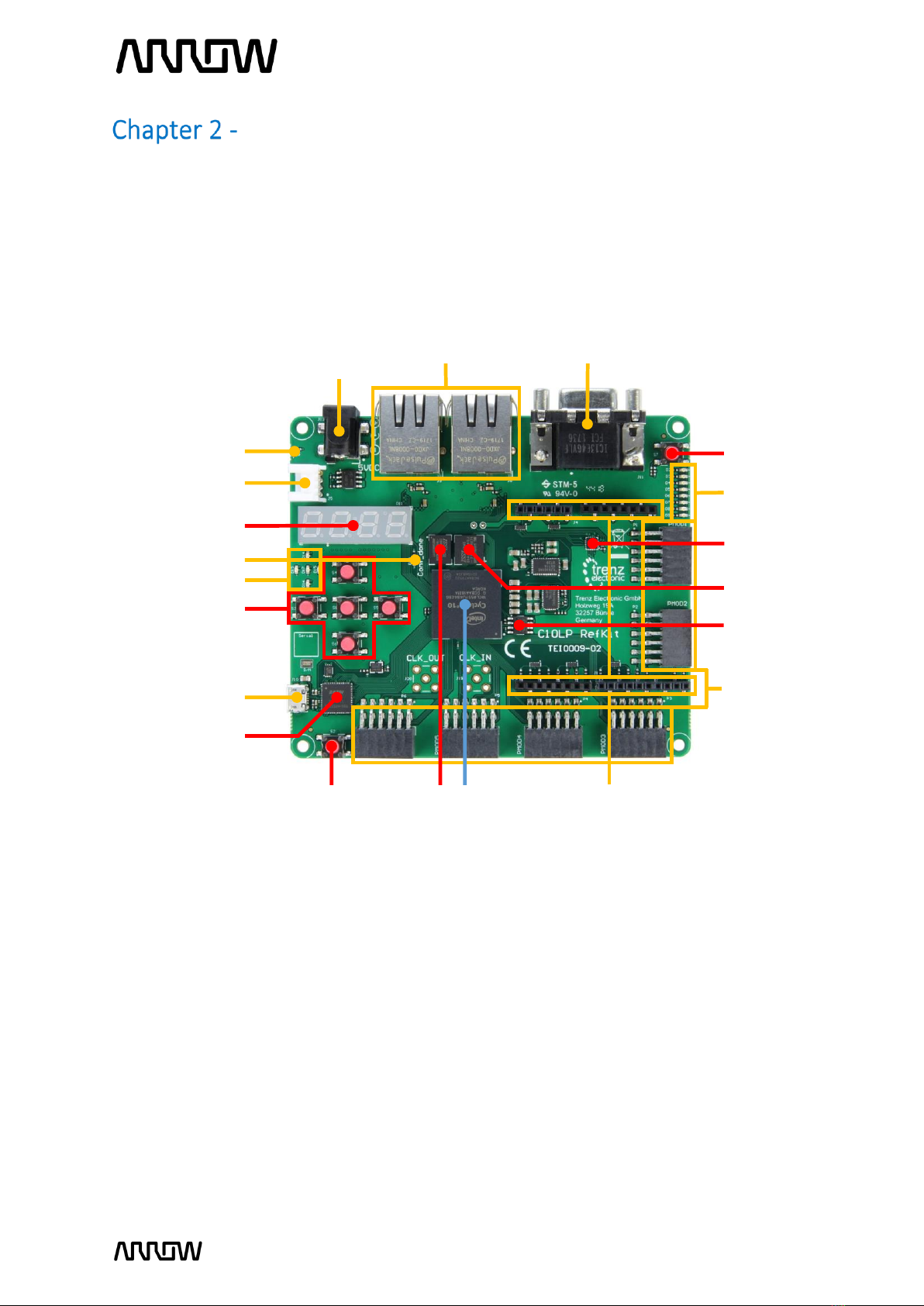

Introduction to the Cyclone 10 LP RefKit Board..................................................... 7

2.1 Layout and Components...................................................................................................7

2.2 Hardware variations .........................................................................................................9

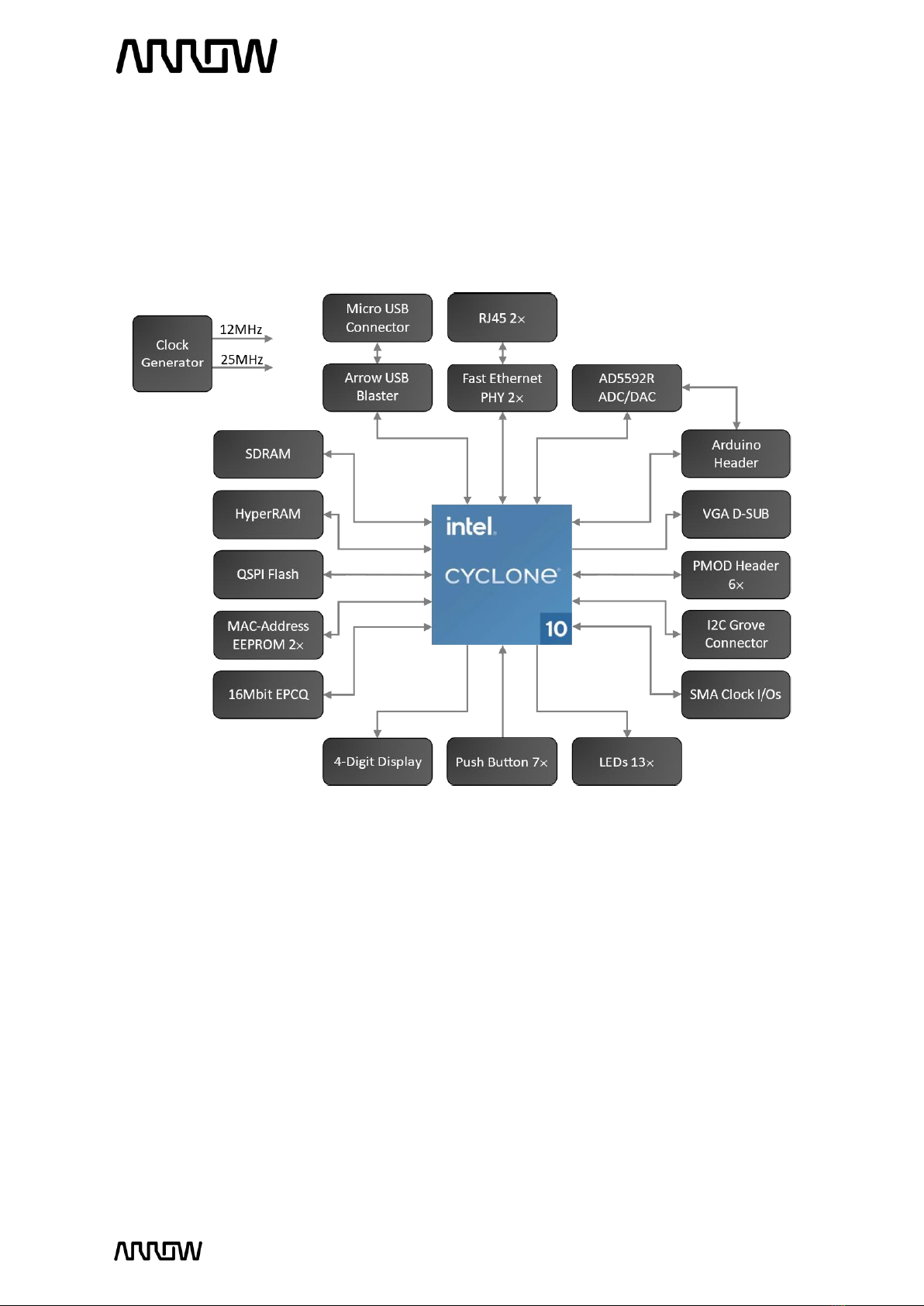

2.3 Block Diagram.................................................................................................................10

Connections and Peripherals of the Cyclone 10 LP RefKit Board .......................... 11

3.1 Board Status Elements....................................................................................................11

3.2 Clock Circuitry.................................................................................................................11

3.3 Peripherals Connected to the FPGA ...............................................................................12

3.3.1 Communication and Configuration.........................................................................12

3.3.2 Fast Ethernet...........................................................................................................14

3.3.3 Serial Configuration Flash Memory ........................................................................15

3.3.4 HyperRAM...............................................................................................................16

3.3.5 SDRAM Memory......................................................................................................17

3.3.6 QSPI Flash Memory.................................................................................................18

3.3.7 EEPROMs.................................................................................................................18

3.3.8 ADC/DAC .................................................................................................................19

3.3.9 I2C Grove Connector...............................................................................................20

3.3.10 Arduino Header.......................................................................................................21

3.3.11 PMOD Connectors...................................................................................................22

3.3.12 VGA..........................................................................................................................24

3.3.13 LEDs.........................................................................................................................25

3.3.14 Push Buttons ...........................................................................................................26

3.3.15 7-segment LED Display............................................................................................27

3.3.16 Power Tree..............................................................................................................28

Software and Driver Installation......................................................................... 30

4.1 Installing Quartus Prime Software..................................................................................30

4.2 Installing Arrow USB Programmer2................................................................................31

4.3 License ............................................................................................................................33