Features

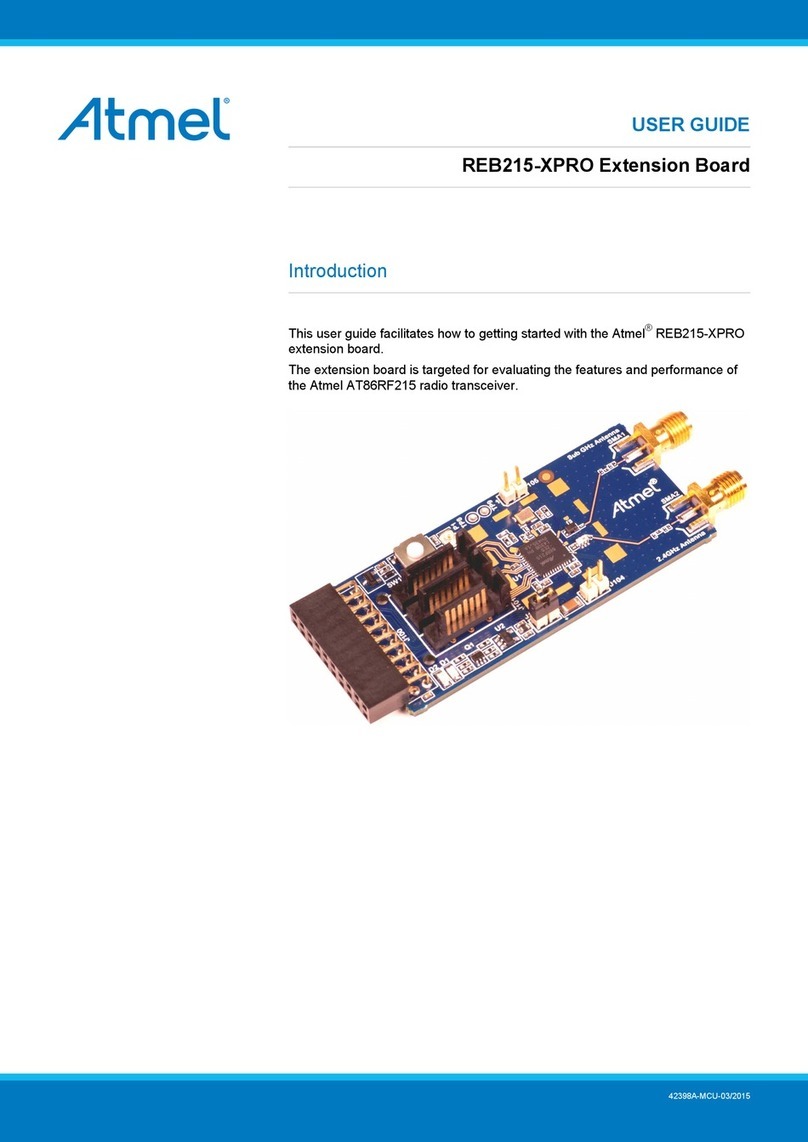

•High Performance RF-CMOS 2.4GHz radio transceiver targeted for

IEEE®802.15.4, ZigBee®, RF4CE, 6LoWPAN, and ISM applications

•Industry leading link budget:

- Receiver sensitivity -100dBm

- Programmable output power from -17dBm up to +3dBm

•Ultra-low current consumption:

- SLEEP = 0.4µA

- TRX_OFF = 330µA

- RX_ON = 11.8mA (LISTEN)

- BUSY_TX = 13.8mA (at max. transmit power)

•Ultra-low supply voltage (1.8V to 3.6V) with internal regulator

•Support for coin cell operation

•Optimized for low BoM cost and ease of production:

- Few external components necessary (crystal, capacitors and antenna)

•Easy to use interface:

- Registers, frame buffer and AES accessible through fast SPI

- Only two microcontroller GPIO lines necessary

- One interrupt pin from radio transceiver

- Clock output

•Radio transceiver features:

- 128-byte FIFO (SRAM) for data buffering

- Fully integrated, fast settling PLL to support Frequency Hopping

- Battery monitor

- Fast Wake-Up time < 0.4msec

•Special IEEE 802.15.4™-2011 hardware support:

- FCS computation and Clear Channel Assessment

- RSSI measurement, Energy Detection and Link Quality Indication

•MAC hardware accelerator:

- Automated acknowledgement, CSMA-CA and retransmission

- Automatic address filtering

- Automated FCS check

•Extended feature set hardware support:

- AES 128-bit hardware accelerator

- Antenna Diversity

- True Random Number Generation for security application

•Commercial temperature range:

- 0°C to +70°C

•I/O and packages:

- 32-pin low-profile QFN package 5 x 5 x 0.9mm³

- RoHS/Fully Green

•Compliant to IEEE 802.15.4-2011, IEEE 802.15.4-2006 and IEEE 802.15.4-2003

•Compliant to EN 300 328/440, FCC-CFR-47 Part 15, ARIB STD-66, RSS-210