Multiple test points

•Test points for input voltage and supercapacitor voltage measurement

•Includes 1Ωresistors for input and output current sensing

Easy to use

Purchase from CAP-XX, visit www.cap-xx.com or email sales@cap-xx.com

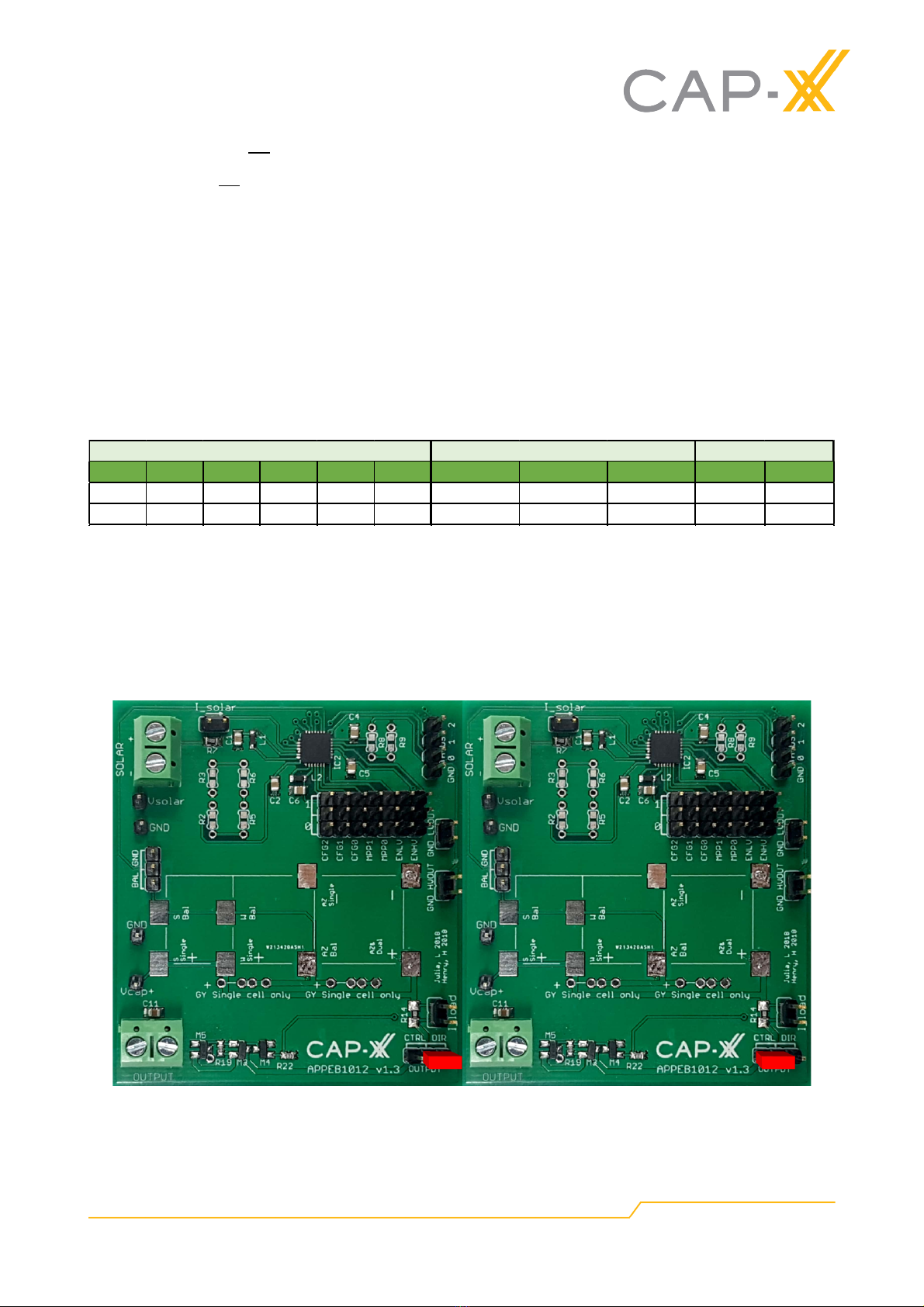

Description

The APPEB1012 is designed to aid the development of energy harvesting applications with a

supercapacitor, particularly solar energy harvesting, using a PMIC to achieve a highly-efficient,

regulated dual-output supply using a supercapacitor as the high power energy storage element.

A cold-start circuit allows the board to start operation with a discharged supercapacitor with an

input voltage as low as 380 mV and input power of just 3 µW. The board incorporates a maximum

power point tracking (MPPT) switch mode power management IC (PMIC), AEM10941 from e-peas.

The IC senses the open-circuit voltage of the solar cell array or other energy harvester every 5

seconds to set the peak power point. For a simpler lower cost alternative that utilises direct

charging from an energy harvester into a supercapacitor please refer to Applications Evaluation

Board, APPEB1011 on our website, www.cap-xx.com .

The AEM10941 has a boost regulator output that charges the supercapacitor. The dual-outputs of

the PMIC are driven by LDO regulators that can be enabled or disabled dynamically by external

control. The low-voltage LDO outputs either 1.2V or 1.8V and the high-voltage output is

configurable between 1.8V and 4.2V. There are configuration headers to determine pre-set charge

for the supercapacitor or external resistors that can be used to set these voltages to other values.

The output of the board can be either directly connected to a load or controlled by the PMIC. The

PMIC enables the output when the supercapacitor is > an upper threshold voltage and disables the

output when the supercapacitor discharges below a lower threshold voltage. The threshold

voltages are defined by the system configuration headers or configuration resistors if the custom

mode is chosen.

The APPEB1012 also includes an inbuilt active balance control which is a feature of the

AEM10941 so dual cell supercapacitors can be used as well as single cell supercapacitors.

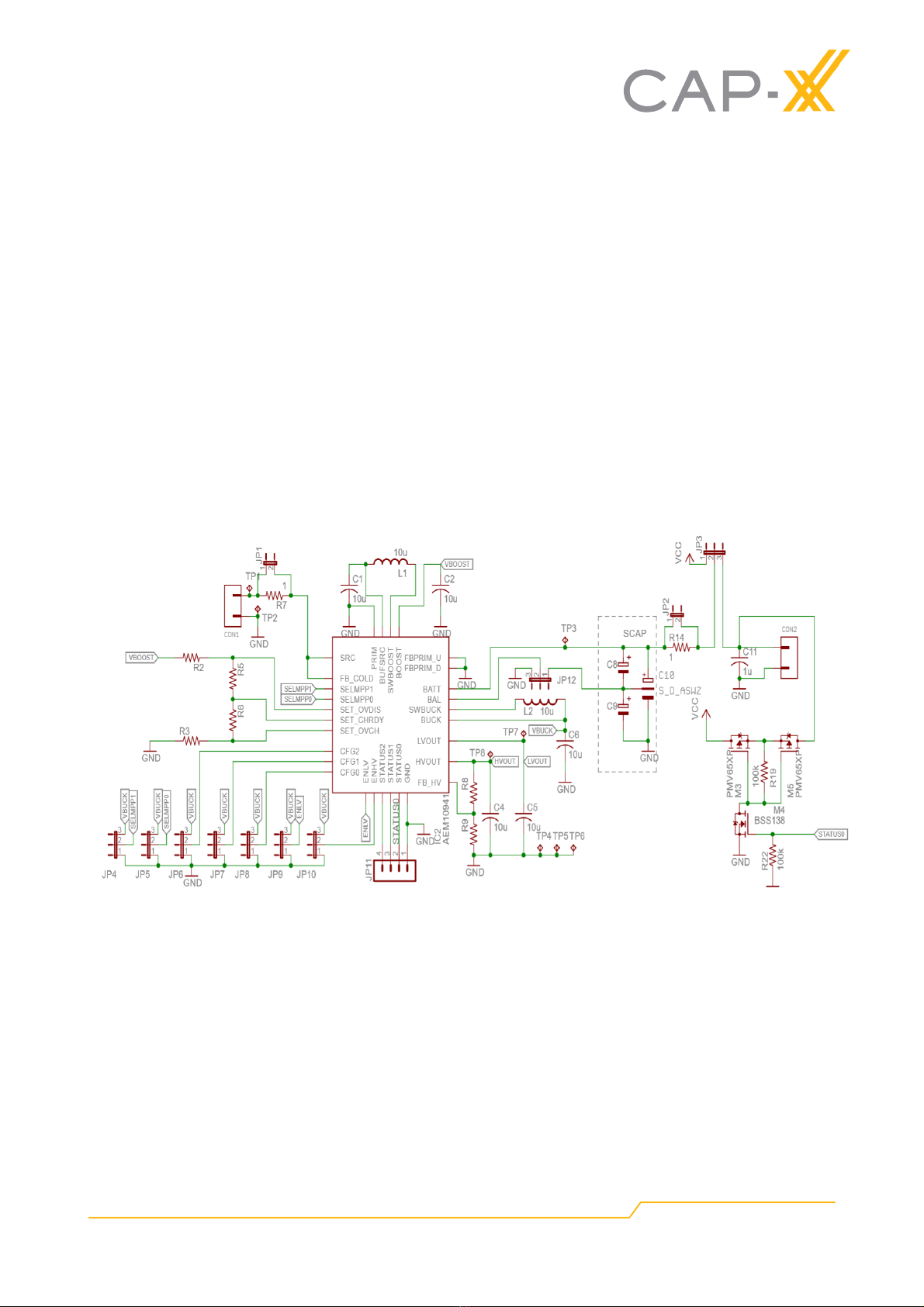

Circuit description

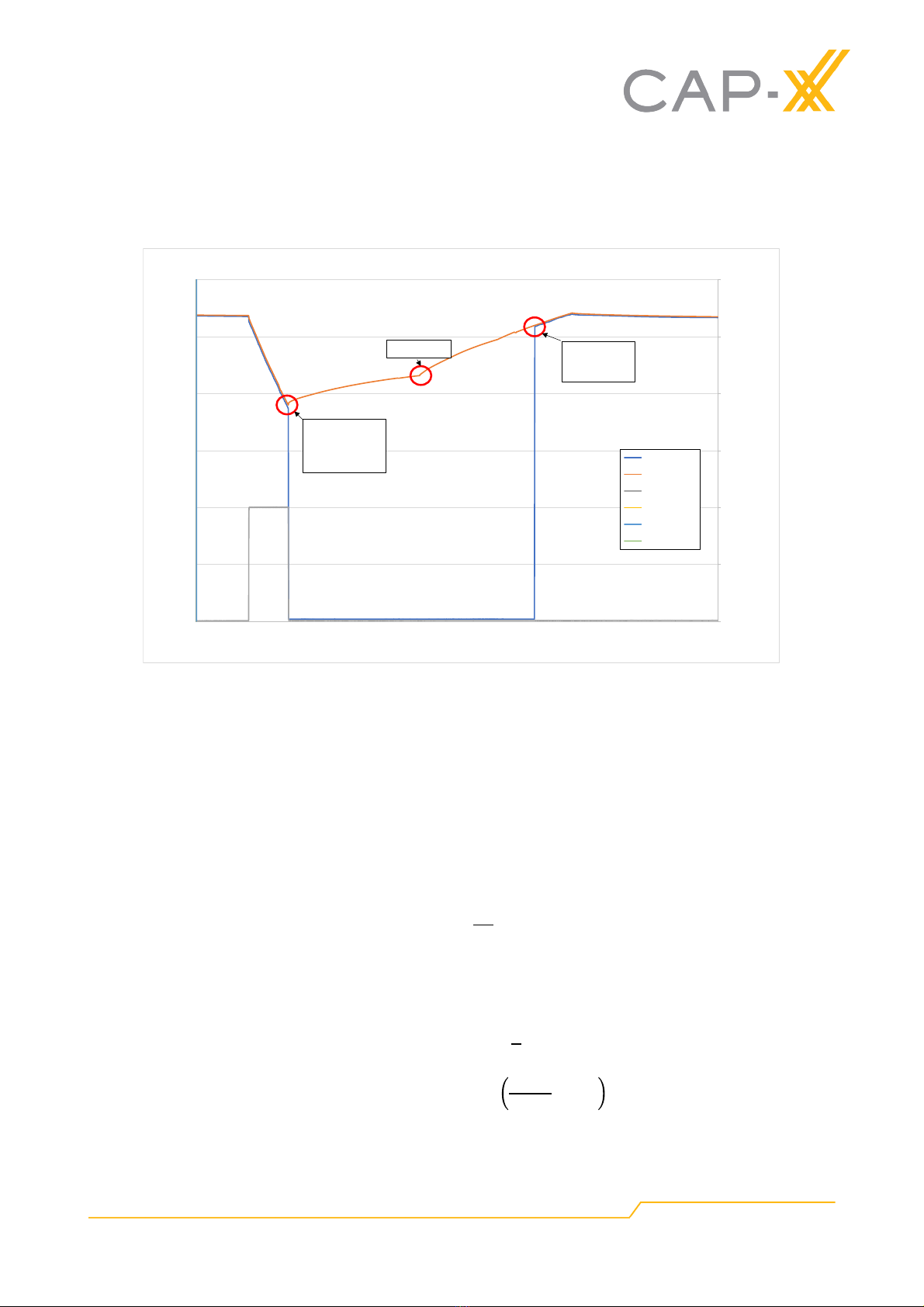

The circuit in figure 1 is separated into two sections. The left half of the schematic contains the

input and the PMIC. The right half is the output control circuit and the output. Where CON1 is the

energy harvester input terminal and CON2 is the output.

The left half of the circuit consists of the e-peas AEM10941 PMIC. Jumper headers JP4 – JP10

configure the AEM10941, as explained in the section on System Configuration. Resistors R2, R3,

R5 and R6 are optional external resistor pads used for a customising the maximum supercapacitor

voltage. The voltage of the dual LDO outputs can also be found in table 3 and the high voltage

LDO can be externally customised by R8 and R9. The landing pad design for resistors R2, R3, R5,

R6, R8 and R9 can accept either SMD 0603 or 5mm pitch through hole packages.

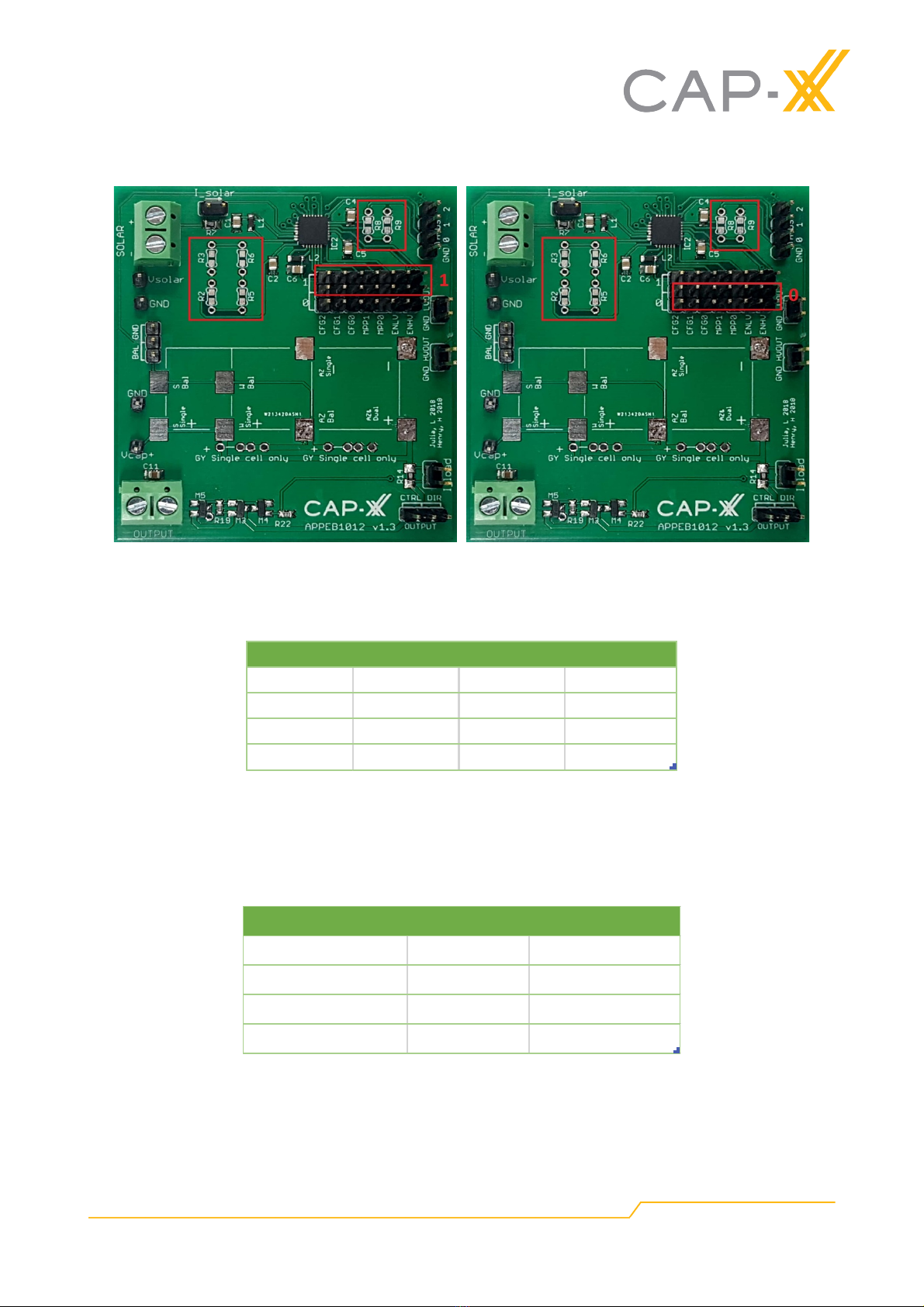

JP12 is the header that either connects the in-built active balance circuit of the PMIC to ground if a

single cell supercapacitor is used or to the midpoint of a dual cell supercapacitor. If a dual cell

supercapacitor is installed then the active balance circuit must be connected to the mid-point to

ensure the voltage on the top and bottom cells are equal. Please refer to AN1002: Cell Balancing

for information in the importance of balancing dual cell supercapacitors.