Casio SF-7900E Troubleshooting guide

SF-7900E(LX-552A)

SF-8900(LX-552I/J)

R

(with price)

(without price)

SF-7900E

JAN. 1995

CONTENTS

SPECIFICATIONS ................................................................................................................ 1

TO REPLACE THE BATTERY ............................................................................................. 2

TO CHECK THE MEMORY CAPACITY............................................................................... 2

ERROR MESSAGE............................................................................................................... 3

TO RESET THE SF UNIT'S MEMORY................................................................................. 4

TO SAVE THE DATA TO ANOTHER UNIT ......................................................................... 5

BLOCK DIAGRAM................................................................................................................ 8

CIRCUIT EXPLANATIONS

System chart................................................................................................................. 9

Power supply circuit .................................................................................................. 10

CPU pin description (HD62076C03).......................................................................... 12

Gate array pin descriptions (SSC2571F0A) ............................................................. 13

Gate array pin descriptions (SSC2571F0B) ............................................................. 14

Operation program ROM pin descriptions .............................................................. 15

RAM pin descriptions ................................................................................................ 15

DIAGNOSTIC OPERATION................................................................................................ 16

TROUBLESHOOTING........................................................................................................ 21

SCHEMATIC DIAGRAM

Main PCB .................................................................................................................... 23

Display PCB................................................................................................................ 25

Key Matrix ................................................................................................................... 26

Key Matrix (Display side)........................................................................................... 27

PARTS LIST........................................................................................................................ 29

ASSEMBLY VIEW .............................................................................................................. 31

— 1 —

SPECIFICATIONS

Main modes: Telephone Directory, Business Card Library, Memo, Schedule Keeper,

Expense, Reminder, Calendar, Home Time, World Time and Calculator

Data storage: Storage and recall of telephone, business card, memo, schedule, expense,

reminder data, calendar display, secret area; editing; memory status display

Clock: World Time; reminder alarm; schedule alarm; daily alarm; accuracy under

normal temperatures: ±3 seconds average

Calculation: 12-digit arithmetic calculations; arithemetic constants (+, –, ×, ÷); independ-

entmemory;percentages;squareroots;24-digitapproximations;datecalcula-

tions; other mixed calculations

General:

Display element: 16-column ×8-line LCD

Memory capacity: SF-7900E: 128KB (103436 bytes)

SF-8900: 256KB (234508 bytes)

Main component: LSI

Power supply: 3 lithium batteries (CR2032)

Power consumption: 0.07 W

Battery life*: Approximately 170 hours continuous operation in Telephone Directory;

approximately 130 hours repeating one minute of input and 10 minutes of

display in Telephone Directory; approximately 12 months for memory back

up

* The batteries that come installed in this unit when you purchase it are for

factory test purposes, so they will probably not provide normal service life.

Auto power off: Approximately 6 minutes after last key operation

Operating temperature: 0°C ~ 40°C (32°F ~ 104°F)

Dimensions: Unfolded: 9.55H ×144W ×155D mm (3/8"H ×5 11/16"W ×6 1/8"D)

Folded: 15.95H ×144W ×77.5D mm(5/8"H ×5 11/16"W ×3 1/16"D)

Weight: 123g (4.3 oz.)

• Design and specifications are subject to change without notice.

Current consumption:

Power switch TYP. [µA] MAX [µA]

OFF 11.7 37.1

ON 1,670.0 13,711.0

ON (Operating) 4,520.0 16,645.0

— 2 —

Hold down

CAPA

to display a screen that shows the current memory status. To clear the memory

status display, release

CAPA

.

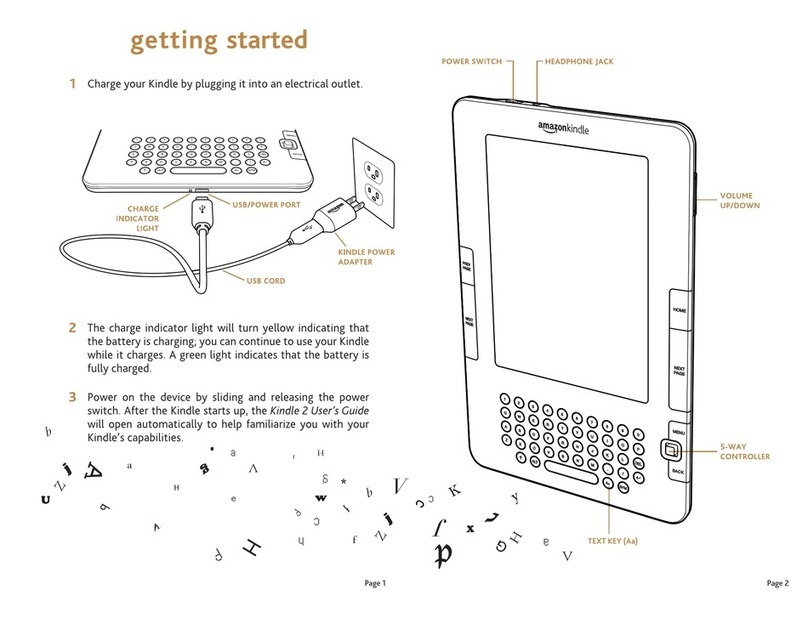

TO CHECK THE MEMORY CAPACITY

Remaining memory

capacity

Total number of characters stored in memory

TO REPLACE THE BATTERY

To replace the batteries

1. Loosen the screw on the back of the SF unit that holds the battery compartment cover in

place, and remove the cover.

Caution

In the next step, be sure to remove only one battery at a time.

Otherwise, you will lose all data stored in memory.

2. Loosen the screw that secures one of the three battery holders

in place and remove the battery holder.

3. Replace the old battery with a new one, making sure that the

positive (+) side of the new battery is facing up (so you can see

it).

4. Replace the battery holder and secure it by tightening its screw.

Screw

RESET

+

10050

0

C

A

P

A

C

I

T

Y

76420BytesFREE

27016BytesUSED

26

%

— 3 —

Message Meaning Action

DATA ITEM Search operation Current search operation

NOT FOUND! attempted when no data cannot be performed.

NO DATA is stored in memory.

IN MEMORY!

DATA ITEM Data specified in search Change specification or

NOT FOUND! operation does not exist cancel search.

in memory.

MEMORY FULL! No more room in memory Delete unnecessary data

for storage of data. items from memory.

ALARM TIME Attempt to set a Schedule Set a different alarm time

ALREADY USED! Keeper alarm time that or change the existing alarm

is already used for time to another one.

another entry.

ALARM TIME Attempt to set a Schedule Set a different alarm time

ALREADY PASSED! Keeper alarm time for a (for a future time/date.)

time/date that is already

passed.

SECRET DATA! Alarm for a secret Enter the secret memory

memory area data item is area to view details of the

sounding. alarm.

PASSWORD Attempt to enter the Use the correct password.

MISMATCH! secret memory area

using a password that

does not match the one

preset for the secret area.

TRANSMIT ERROR! Error during data Cancel the data

communications. communications

STOPPED! operation and try again.

DATA ERROR! Data corrupted by strong See page 11 of the

CONSULT THE impact, electrostatic owner's manual.

OWNER'S MANUAL! charge, etc.

SAME TYPE Attempt to store a label Use a different label.

ALREADY USED! that is identical to one

already stored.

ERROR MESSAGE

— 4 —

TO RESET THE SF UNIT'S MEMORY

The following procedure erases all data stored in the memory of the SF unit.

Perform the following operation only when you want to delete all data and initialize the settings of the SF

unit.

Remember – you should always keep copies of important data by writing it down, by transferring it to a

personal computer or other SF unit.

To reset the SF Unit's memory

1. Switch on power and press the RESET button with a thin, pointed object.

Warning!

The next step deletes all data stored in the SF unit's memory. Make sure that you really want

to delete the data before you continue!

2. Press Yto reset the memory and delete all data or Nto abort the reset operation without

deleting anything.

Following the reset operation described above, the Home Time display appears and the SF unit

settings are initialized as noted below.

Home Time: 12-hour format

JAN/1/1995

AM/12:00 00

World Time: Washington D.C.

Daily Alarm: 12:00 PM

Sound: Schedule alarm →ON

Reminder alarm →ON

Daily alarm →OFF

Key →ON

Character input: CAPS

RESET

RESET button

— 5 —

2) Turn on the power switch of both units.

3) The slave unit must be set the date of Feb. 3rd, 1901 into the memory under the calculator

mode.

Operation: 1 DATE 2 DATE 3 DATE M+

If you don't set the date, the "PASSWORD" isn't transferred to the slave unit.

TO SAVE THE DATA TO ANOTHER UNIT

SF-7900 can transfer customers data to another SF-7900 with memory protection only when replacing

the LCD or the outer case.

How to transfer the data

* Before connecting the cable (SB-60 or SB-62), be sure to reset the slave unit to clear all

data.

1) Turn off the power switch and connect the two units using the cable (SB-60 or SB-62) as shown in

the drawing.

To change the hardware

parameters, press the

, , and

cursol keys.

4) Check the hardware parameters, and if the units have another condition, reset as follows.

TEL

To set the hardware

parameters, press the SET

key.

SET UP

PARITY NONE

BIT LENGTH 7

BPS 9600

ON CAL

CLEAR

FUNC 4 4

— 6 —

5) Set up the slave unit.

1 While in the Calendar Display, Telephone Directory, Business Card Library, Memo Mode, or

Schedule Keeper, press the FUNCTION key followed by 4 to select " DATA COMM", and

the following menu appears.

2 Press 2 to select "RECEIVE" and the following display appears to indicate that the slave unit

is ready to receive data.

6) Set up the customer's unit.

1 While the transmitting unit is in the Calendar Display, Telephone Directory, Business Card

Library, Memo Mode, or Schedule Keeper, press the FUNCTION key followed by 4 to

select "DATA COMM", and the following menu appears.

2 Press 1 to select "SEND" and the following menu appears.

1 SEND

2 RECEIVE

3 PRINT

4 SET UP

DATA

RECEIVE OK

TO STOP

PRESS [ESC]

FUNCTION 4

TEL

2

TEL FUNCTION 4

1

SEND

1 ONE ITEM

2 MODE DATA

3 ALL DATA

1 SEND

2 RECEIVE

3 PRINT

4 SET UP

— 7 —

3 Press 3 to select "ALL DATA". The following display appears to confirm if you wish to

proceed.

4 Press the SET key to proceed with the data transmission, or press ESC if you wish to

cancel.

TEL MEMO REMINDER

HOME/WORLDSCHEDULE

Data are transmitted in the sequence of Telephone Directory data, Memo data, Reminder data,

Schedule Keeper data and Calendar data.

* The following messages appear on the display of the receiving unit when a problem occurs during

data communications. All data transferred up to display of the message is retained in memory, but

data communication is terminated.

If one of the following error messages appear, press the , , , , ,

, keys, to clear the error message. Then, take corrective action and try data

communication again.

CAL CALENDAR

Message Meaning Action

TRANSMIT ERROR! Error during data Cancel the data

STOPPED! communications. communications operation

and try again.

DATA ERROR! Data corrupted by strong See page 9 of the owner's

CONSULT THE impact, electrostatic manual.

OWNER'S MANUAL! charge, etc.

SEND ALL

DATA ITEM ?

SET / ESC

NOW SENDING !

TO STOP, PRESS ESC

3

SET

— 8 —

LOCK (ON)

C0~C63

CPU

GATE ARRAY

Power supply circuit

LCD DRIVE

VOLTAGES

DATA BUS

S16~S95S0~S15

LCD 96 × 64 dots

INTERFACE FOR

DATA TRANSMISSION

& DATA RECEPTION

OPEN (OFF)

MSM6585AV

-Z-358B

LCD DRIVERLCD DRIVER

MSM6585AV

-Z-358B

MAIN SWITCH

BLOCK DIAGRAM

CD760-TS

VDD

GND

SSC2571

LSI2

HD62076C03

LSI1

PCB-L589-E4

TO KEYBOARD

KEYBOARD

RAM

MSM51008AFP-10LL

LSI3, LSI4

ROM

(Operation Program)

LSI5

V1 ~ V5 PCB-L522-1(SF-7900E)

or

PCB-L552-1(SF-8900)

PCB-L589-E2

SF-7900E: RAM ×1

SF-8900: RAM ×2

Other manuals for SF-7900E

1

This manual suits for next models

3

Table of contents

Other Casio Ebook Reader manuals