Cirrus Logic CS2100-CP User manual

Cirrus Logic Confidential

Copyright Cirrus Logic, Inc. 2009–2015

(All Rights Reserved)

http://www.cirrus.com

Fractional-N Clock Multiplier

Features

Clock Multiplier / Jitter Reduction

– Generates a Low Jitter 6 - 75 MHz Clock

from a Jittery or Intermittent 50 Hz to 30

MHz Clock Source

Highly Accurate PLL Multiplication Factor

– Maximum Error Less Than 1 PPM in High-

Resolution Mode

I²C / SPI™ Control Port

Configurable Auxiliary Output

Flexible Sourcing of Reference Clock

– External Oscillator or Clock Source

– Supports Inexpensive Local Crystal

Minimal Board Space Required

– No External Analog Loop-filter

Components

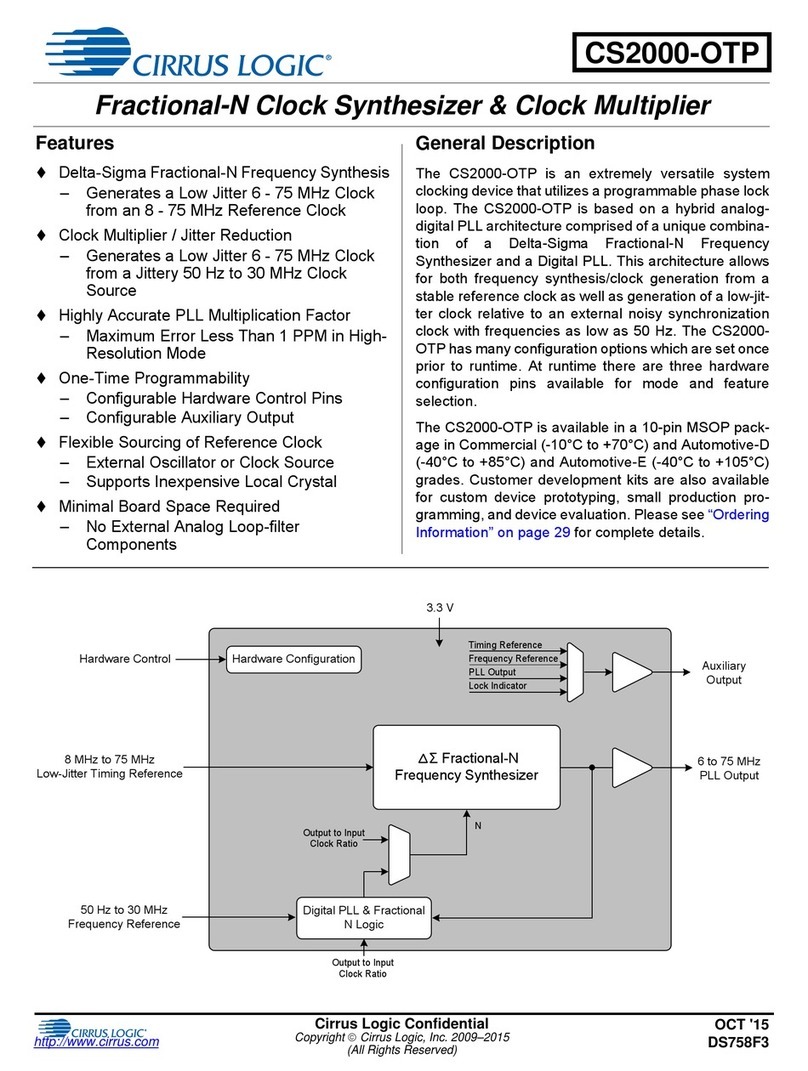

General Description

The CS2100-CP is an extremely versatile system

clocking device that utilizes a programmable phase

lock loop. The CS2100-CP is based on a hybrid ana-

log-digital PLL architecture comprised of a unique

combination of a Delta-Sigma Fractional-N Frequency

Synthesizer and a Digital PLL. This architecture allows

for generation of a low-jitter clock relative to an exter-

nal noisy synchronization clock at frequencies as low

as 50 Hz. The CS2100-CP supports both I²C and SPI

for full software control.

The CS2100-CP is available in a 10-pin MSOP pack-

age in Commercial (-10°C to +70°C) and Automotive-

D (-40°C to +85°C) and Automotive-E (-40°C to

+105°C) grades. Customer development kits are also

available for device evaluation. Please see “Ordering

Information” on page 32 for complete details.

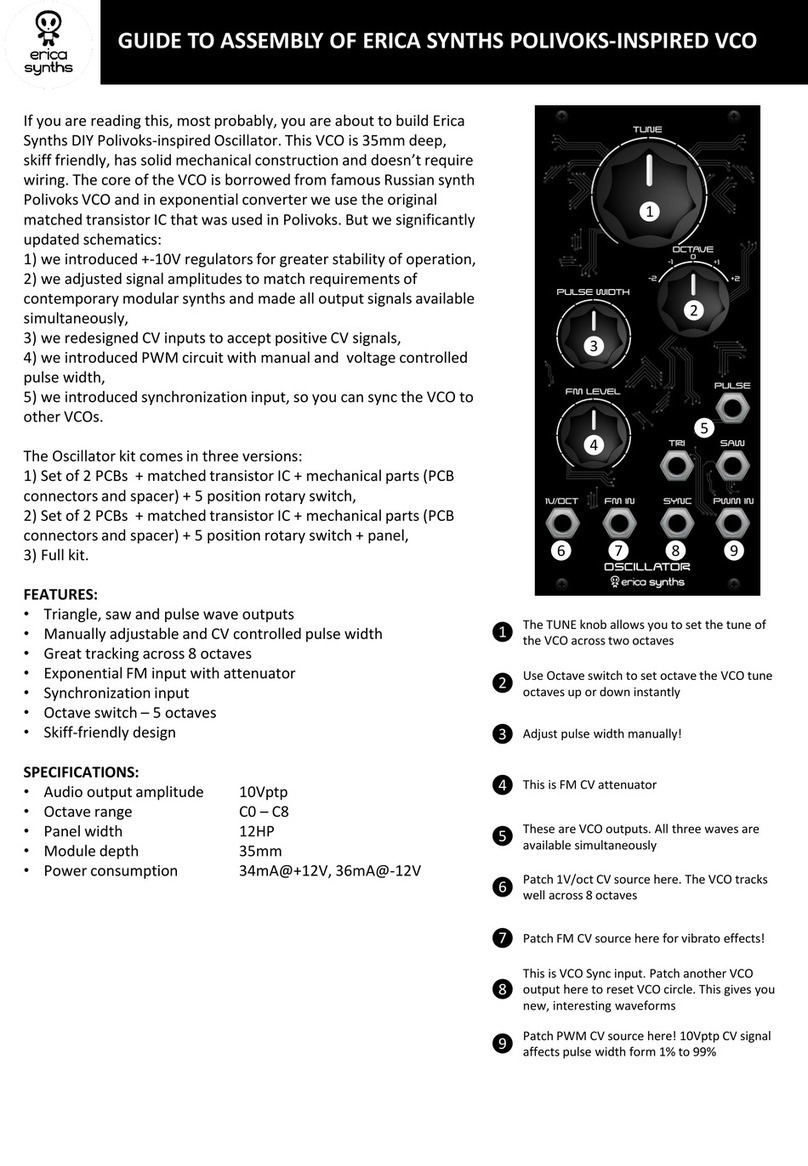

I²C / SPI Auxiliary

Output

6 to 75 MHz

PLL Output

3.3 V

I²C/SPI

Software Control

8 MHz to 75 MHz

Low-Jitter Timing

Reference

Fractional-N

Frequency Synthesizer

Digital PLL & Fractional

N Logic

Output to Input

Clock Ratio

N

Timing Reference

PLL Output

Lock Indicator

50 Hz to 30 MHz

Frequency

Reference

Frequency Reference

OCT '15

DS840F3

CS2100-CP

CS2100-CP

2DS840F3

TABLE OF CONTENTS

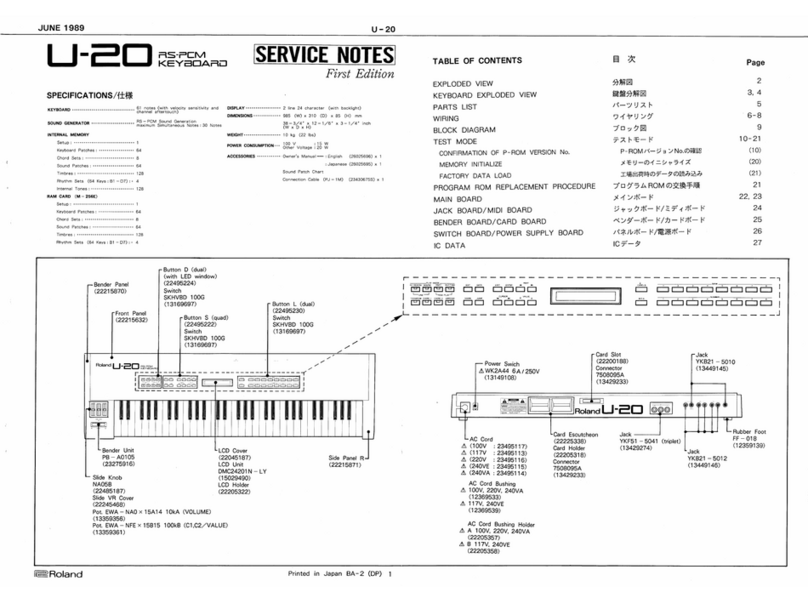

1. PIN DESCRIPTION ................................................................................................................................. 5

2. TYPICAL CONNECTION DIAGRAM ..................................................................................................... 6

3. CHARACTERISTICS AND SPECIFICATIONS ...................................................................................... 7

RECOMMENDED OPERATING CONDITIONS .................................................................................... 7

ABSOLUTE MAXIMUM RATINGS ........................................................................................................ 7

DC ELECTRICAL CHARACTERISTICS ................................................................................................ 7

AC ELECTRICAL CHARACTERISTICS ................................................................................................ 8

PLL PERFORMANCE PLOTS ............................................................................................................... 9

CONTROL PORT SWITCHING CHARACTERISTICS- I²C FORMAT ................................................. 10

CONTROL PORT SWITCHING CHARACTERISTICS - SPI FORMAT ............................................... 11

4. ARCHITECTURE OVERVIEW ............................................................................................................. 12

4.1 Delta-Sigma Fractional-N Frequency Synthesizer ......................................................................... 12

4.2 Hybrid Analog-Digital Phase Locked Loop ....................................................................................12

5. APPLICATIONS ................................................................................................................................... 14

5.1 Timing Reference Clock Input ........................................................................................................ 14

5.1.1 Internal Timing Reference Clock Divider ............................................................................... 14

5.1.2 Crystal Connections (XTI and XTO) ...................................................................................... 15

5.1.3 External Reference Clock (REF_CLK) .................................................................................. 15

5.2 Frequency Reference Clock Input, CLK_IN ................................................................................... 15

5.2.1 CLK_IN Skipping Mode ......................................................................................................... 15

5.2.2 Adjusting the Minimum Loop Bandwidth for CLK_IN ............................................................ 17

5.3 Output to Input Frequency Ratio Configuration ............................................................................. 18

5.3.1 User Defined Ratio (RUD) ..................................................................................................... 18

5.3.2 Ratio Modifier (R-Mod) .......................................................................................................... 19

5.3.3 Effective Ratio (REFF) .......................................................................................................... 20

5.3.4 Ratio Configuration Summary ............................................................................................... 20

5.4 PLL Clock Output ........................................................................................................................... 21

5.5 Auxiliary Output .............................................................................................................................. 21

5.6 Clock Output Stability Considerations ............................................................................................ 22

5.6.1 Output Switching ................................................................................................................... 22

5.6.2 PLL Unlock Conditions .......................................................................................................... 22

5.7 Required Power Up Sequencing .................................................................................................... 22

6. SPI / I²C CONTROL PORT ................................................................................................................... 22

6.1 SPI Control ..................................................................................................................................... 23

6.2 I²C Control ...................................................................................................................................... 23

6.3 Memory Address Pointer ............................................................................................................... 25

6.3.1 Map Auto Increment .............................................................................................................. 25

7. REGISTER QUICK REFERENCE ........................................................................................................ 25

8. REGISTER DESCRIPTIONS ................................................................................................................ 26

8.1 Device I.D. and Revision (Address 01h) ....................................................................................... 26

8.1.1 Device Identification (Device[4:0]) - Read Only ..................................................................... 26

8.1.2 Device Revision (Revision[2:0]) - Read Only ........................................................................ 26

8.2 Device Control (Address 02h) ........................................................................................................ 26

8.2.1 Unlock Indicator (Unlock) - Read Only .................................................................................. 26

8.2.2 Auxiliary Output Disable (AuxOutDis) ................................................................................... 26

8.2.3 PLL Clock Output Disable (ClkOutDis) .................................................................................. 27

8.3 Device Configuration 1 (Address 03h) ........................................................................................... 27

8.3.1 R-Mod Selection (RModSel[2:0]) ...........................................................................................27

8.3.2 Auxiliary Output Source Selection (AuxOutSrc[1:0]) ............................................................. 27

8.3.3 Enable Device Configuration Registers 1 (EnDevCfg1) ........................................................ 28

8.4 Global Configuration (Address 05h) ............................................................................................... 28

8.4.1 Device Configuration Freeze (Freeze) ................................................................................ 28

CS2100-CP

DS840F3 3

8.4.2 Enable Device Configuration Registers 2 (EnDevCfg2) ....................................................... 28

8.5 Ratio (Address 06h - 09h) .............................................................................................................. 28

8.6 Function Configuration 1 (Address 16h) ........................................................................................ 29

8.6.1 Clock Skip Enable (ClkSkipEn) ............................................................................................. 29

8.6.2 AUX PLL Lock Output Configuration (AuxLockCfg) .............................................................. 29

8.6.3 Reference Clock Input Divider (RefClkDiv[1:0]) .................................................................... 29

8.7 Function Configuration 2 (Address 17h) ........................................................................................ 30

8.7.1 Enable PLL Clock Output on Unlock (ClkOutUnl) ................................................................. 30

8.7.2 Low-Frequency Ratio Configuration (LFRatioCfg) ................................................................ 30

8.8 Function Configuration 3 (Address 1Eh) ........................................................................................ 30

8.8.1 Clock Input Bandwidth (ClkIn_BW[2:0]) ................................................................................ 30

9. CALCULATING THE USER DEFINED RATIO .................................................................................... 31

9.1 High Resolution 12.20 Format ....................................................................................................... 31

9.2 High Multiplication 20.12 Format ................................................................................................... 31

10. PACKAGE DIMENSIONS .................................................................................................................. 32

THERMAL CHARACTERISTICS ......................................................................................................... 32

11. ORDERING INFORMATION .............................................................................................................. 33

12. REFERENCES .................................................................................................................................... 33

13. REVISION HISTORY .......................................................................................................................... 34

LIST OF FIGURES

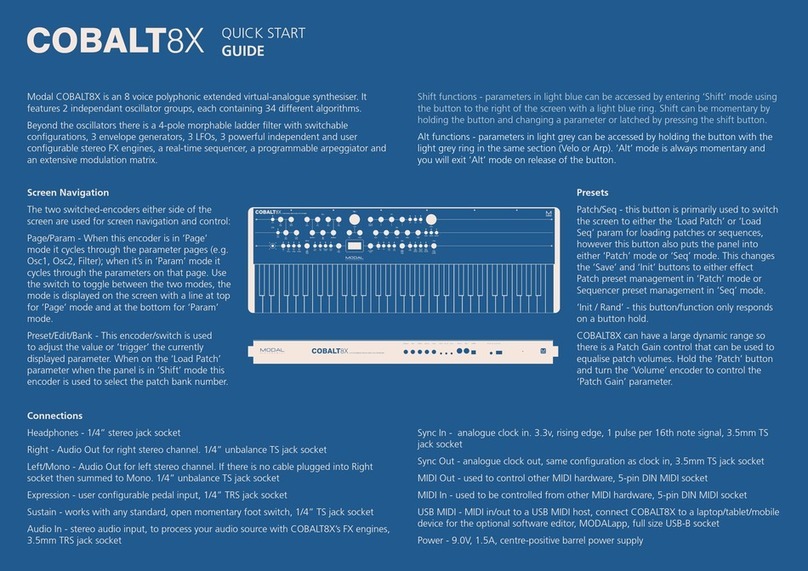

Figure 1. Typical Connection Diagram ........................................................................................................ 6

Figure 2. CLK_IN Sinusoidal Jitter Tolerance ............................................................................................. 9

Figure 3. CLK_IN Sinusoidal Jitter Transfer ................................................................................................ 9

Figure 4. CLK_IN Random Jitter Rejection and Tolerance .........................................................................9

Figure 5. Control Port Timing - I²C Format ................................................................................................ 10

Figure 6. Control Port Timing - SPI Format (Write Only) .......................................................................... 11

Figure 7. Delta-Sigma Fractional-N Frequency Synthesizer ..................................................................... 12

Figure 8. Hybrid Analog-Digital PLL .......................................................................................................... 13

Figure 9. Internal Timing Reference Clock Divider ................................................................................... 14

Figure 10. REF_CLK Frequency vs. a Fixed CLK_OUT ........................................................................... 14

Figure 11. External Component Requirements for Crystal Circuit ............................................................ 15

Figure 12. CLK_IN removed for > 223 SysClk cycles ................................................................................ 16

Figure 13. CLK_IN removed for < 223 SysClk cycles but > tCS .................................................................................. 16

Figure 14. CLK_IN removed for < tCS .................................................................................................................................. 17

Figure 15. Low bandwidth and new clock domain .................................................................................... 18

Figure 16. High bandwidth with CLK_IN domain re-use ........................................................................... 18

Figure 17. Ratio Feature Summary ........................................................................................................... 20

Figure 18. PLL Clock Output Options ....................................................................................................... 21

Figure 19. Auxiliary Output Selection ........................................................................................................ 21

Figure 20. Control Port Timing in SPI Mode ............................................................................................. 23

Figure 21. Control Port Timing, I²C Write .................................................................................................. 24

Figure 22. Control Port Timing, I²C Aborted Write + Read .......................................................................24

LIST OF TABLES

Table 1. Ratio Modifier .............................................................................................................................. 19

Table 2. Example 12.20 R-Values ............................................................................................................ 31

Table 3. Example 20.12 R-Values ............................................................................................................ 31

CS2100-CP

4DS840F3

1. PIN DESCRIPTION

Pin Name # Pin Description

VD 1 Digital Power (Input) - Positive power supply for the digital and analog sections.

GND 2 Ground (Input) - Ground reference.

CLK_OUT 3 PLL Clock Output (Output) - PLL clock output.

AUX_OUT 4Auxiliary Output (Output) - This pin outputs a buffered version of one of the input or output clocks,

or a status signal, depending on register configuration.

CLK_IN 5 Frequency Reference Clock Input (Input) - Clock input for the Digital PLL frequency reference.

XTO

XTI/REF_CLK

6

7

Crystal Connections (XTI/XTO) / Timing Reference Clock Input (REF_CLK) (Input/Output) -

XTI/XTO are I/O pins for an external crystal which may be used to generate the low-jitter PLL input

clock. REF_CLK is an input for an externally generated low-jitter reference clock.

AD0/CS 8Address Bit 0 (I²C) / Control Port Chip Select (SPI) (Input) - AD0 is a chip address pin in I²C

Mode. CS is the chip select signal in SPI Mode.

SCL/CCLK 9Control Port Clock (Input) - SCL/CCLK is the serial clock for the serial control port in I²C and SPI

mode.

SDA/CDIN 10 Serial Control Data (Input/Output) - SDA is the data I/O line in I²C Mode. CDIN is the input data

line for the control port interface in SPI Mode.

1

2

3

4

56

7

8

9

10

XTO

CLK_OUT

GND

VD

XTI/REF_CLK

AD0/CS

SCL/CCLK

SDA/CDIN

AUX_OUT

CLK_IN

CS2100-CP

DS840F3 5

2. TYPICAL CONNECTION DIAGRAM

2

1

GND

SCL/CCLK

SDA/CDIN

2 k

XTI/REF_CLK

Frequency Reference CLK_IN

XTO

CLK_OUT

AUX_OUT

0.1 µF

VD

+3.3 V

Notes:

1. Resistors

required for I2C

operation. 2 k

AD0/CS

Low-Jitter

Timing Reference

System MicroController

1 µF

Note1

1

or

2

REF_CLK

XTO

XTI

XTO

or

40 pF

x

40 pF

Crystal

To circuitry which requires

a low-jitter clock

N.C.

To other circuitry or

Microcontroller

Figure 1. Typical Connection Diagram

CS2100-CP

CS2100-CP

6DS840F3

3. CHARACTERISTICS AND SPECIFICATIONS

RECOMMENDED OPERATING CONDITIONS

GND = 0 V; all voltages with respect to ground. (Note 1)

Notes: 1. Device functionality is not guaranteed or implied outside of these limits. Operation outside of these limits

may adversely affect device reliability.

ABSOLUTE MAXIMUM RATINGS

GND = 0 V; all voltages with respect to ground.

WARNING:Operation at or beyond these limits may result in permanent damage to the device.

Notes: 2. The maximum over/under voltage is limited by the input current except on the power supply pin.

DC ELECTRICAL CHARACTERISTICS

Test Conditions (unless otherwise specified): VD = 3.1 V to 3.5 V; TA= -10°C to +70°C (Commercial Grade);

TA= -40°C to +85°C (Automotive-D Grade); TA= -40°C to +105°C (Automotive-E Grade).

Notes: 3. To calculate the additional current consumption due to loading (per output pin), multiply clock output

frequency by load capacitance and power supply voltage.

For example, fCLK_OUT (49.152 MHz) * CL (15 pF) * VD (3.3 V) = 2.4 mA of additional current due to

these loading conditions on CLK_OUT.

Parameters Symbol Min Typ Max Units

DC Power Supply VD 3.1 3.3 3.5 V

Ambient Operating Temperature (Power Applied)

Commercial Grade

Automotive-D Grade

Automotive-E Grade

TAC

TAD

TAE

-10

-40

-40

-

-

-

+70

+85

+105

°C

°C

°C

Parameters Symbol Min Max Units

DC Power Supply VD -0.3 6.0 V

Input Current IIN -±10mA

Digital Input Voltage (Note 2)V

IN -0.3 VD + 0.4 V

Ambient Operating Temperature (Power Applied) TA-55 125 °C

Storage Temperature Tstg -65 150 °C

Parameters Symbol Min Typ Max Units

Power Supply Current - Unloaded (Note 3)I

D-1218mA

Power Dissipation - Unloaded (Note 3)P

D-4060mW

Input Leakage Current IIN --±10µA

Input Capacitance IC-8-pF

High-Level Input Voltage VIH 70% - - VD

Low-Level Input Voltage VIL --30%VD

High-Level Output Voltage (IOH = -1.2 mA) VOH 80% - - VD

Low-Level Output Voltage (IOH = 1.2 mA) VOL --20%VD

CS2100-CP

DS840F3 7

AC ELECTRICAL CHARACTERISTICS

Test Conditions (unless otherwise specified): VD = 3.1 V to 3.5 V; TA= -10°C to +70°C (Commercial Grade);

TA= -40°C to +85°C (Automotive-D Grade); TA= -40°C to +105°C (Automotive-E Grade); CL=15pF.

Notes: 4. 1 UI (unit interval) corresponds to tSYS_CLK or 1/fSYS_CLK.

5. tCS represents the time from the removal of CLK_IN by which CLK_IN must be re-applied to ensure that

PLL_OUT continues while the PLL re-acquires lock. This timeout is based on the internal VCO frequen-

cy, with the minimum timeout occurring at the maximum VCO frequency. Lower VCO frequencies will

result in larger values of tCS.

6. Only valid in clock skipping mode; See “CLK_IN Skipping Mode” on page 14 for more information.

7. fCLK_OUT is ratio-limited when fCLK_IN is below 72 Hz.

8. fCLK_OUT = 24.576 MHz; Sample size = 10,000 points; AuxOutSrc[1:0] =11.

9. In accordance with AES-12id-2006 section 3.4.2. Measurements are Time Interval Error taken with 3rd

order 100 Hz to 40 kHz bandpass filter.

10. In accordance with AES-12id-2006 section 3.4.1. Measurements are Time Interval Error taken with 3rd

order 100 Hz Highpass filter.

11. 1 UI (unit interval) corresponds to tCLK_IN or 1/fCLK_IN.

12. The frequency accuracy of the PLL clock output is directly proportional to the frequency accuracy of the

reference clock.

Parameters Symbol Conditions Min Typ Max Units

Crystal Frequency

Fundamental Mode XTAL

fXTAL RefClkDiv[1:0] = 10

RefClkDiv[1:0] = 01

RefClkDiv[1:0] = 00

8

16

32

-

-

-

18.75

37.5

50

MHz

MHz

MHz

Reference Clock Input Frequency fREF_CLK RefClkDiv[1:0] = 10

RefClkDiv[1:0] = 01

RefClkDiv[1:0] = 00

8

16

32

-

-

-

18.75

37.5

75

MHz

MHz

MHz

Reference Clock Input Duty Cycle DREF_CLK 45 - 55 %

Internal System Clock Frequency fSYS_CLK 8 18.75 MHz

Clock Input Frequency fCLK_IN 50 Hz - 30 MHz

Clock Input Pulse Width (Note 4)pw

CLK_IN fCLK_IN < fSYS_CLK/96

fCLK_IN > fSYS_CLK/96

2

10

-

-

-

-

UI

ns

Clock Skipping Timeout tCS (Notes 5, 6)20--ms

Clock Skipping Input Frequency fCLK_SKIP (Note 6) 50 Hz - 80 kHz

PLL Clock Output Frequency fCLK_OUT (Note 7)6-75MHz

PLL Clock Output Duty Cycle tOD Measured at VD/2 45 50 55 %

Clock Output Rise Time tOR 20% to 80% of VD - 1.7 3.0 ns

Clock Output Fall Time tOF 80% to 20% of VD - 1.7 3.0 ns

Period Jitter tJIT (Note 8) - 70 - ps rms

Base Band Jitter (100 Hz to 40 kHz) (Notes 8, 9) - 50 - ps rms

Wide Band JItter (100 Hz Corner) (Notes 8, 10) - 175 - ps rms

PLL Lock Time - CLK_IN (Note 11)t

LC fCLK_IN < 200 kHz

fCLK_IN > 200 kHz

-

-

100

1

200

3

UI

ms

PLL Lock Time - REF_CLK tLR fREF_CLK = 8 to 75 MHz - 1 3 ms

Output Frequency Synthesis Resolution (Note 12)f

err High Resolution

High Multiplication

0

0

-

-

±0.5

±112

ppm

ppm

CS2100-CP

8DS840F3

PLL PERFORMANCE PLOTS

Test Conditions (unless otherwise specified): VD = 3.3 V; TA=25°C;C

L=15pF;f

CLK_OUT = 12.288 MHz;

fCLK_IN = 12.288 MHz; Sample size = 10,000 points; Base Band Jitter (100 Hz to 40 kHz); AuxOutSrc[1:0] =11.

110 100 1,000 10,000

0.1

1

10

100

1,000

10,000

Input Jitter Frequency (Hz)

Max Input Jitter Level (usec)

1 Hz Bandwidth

128 Hz Bandwidth

110 100 1000 10000

-60

-50

-40

-30

-20

-10

0

10

Input Jitter Frequency (Hz)

Jitter Transfer (dB)

1 Hz Bandwidth

128 Hz Bandwidth

Figure 2. CLK_IN Sinusoidal Jitter Tolerance Figure 3. CLK_IN Sinusoidal Jitter Transfer

Samples size = 2.5M points; Base Band Jitter (100Hz to 40kHz). Samples size = 2.5M points; Base Band Jitter (100Hz to 40kHz).

Figure 4. CLK_IN Random Jitter Rejection and Tolerance

0.01 0.1 110 100 1000

0.01

0.1

1

10

100

1000

Input Jitter Level (nsec)

Output Jitter Level (nsec)

1 Hz Bandwidth

128 Hz Bandwidth

Unlock

Unlock

CS2100-CP

DS840F3 9

CONTROL PORT SWITCHING CHARACTERISTICS- I²C FORMAT

Inputs: Logic 0 = GND; Logic 1 = VD; CL=20pF.

Notes: 13. Data must be held for sufficient time to bridge the transition time, tf, of SCL.

Parameter Symbol Min Max Unit

SCL Clock Frequency fscl - 100 kHz

Bus Free-Time Between Transmissions tbuf 4.7 - µs

Start Condition Hold Time (prior to first clock pulse) thdst 4.0 - µs

Clock Low Time tlow 4.7 - µs

Clock High Time thigh 4.0 - µs

Setup Time for Repeated Start Condition tsust 4.7 - µs

SDA Hold Time from SCL Falling (Note 13)t

hdd 0-µs

SDA Setup Time to SCL Rising tsud 250 - ns

Rise Time of SCL and SDA tr-1µs

Fall Time SCL and SDA tf- 300 ns

Setup Time for Stop Condition tsusp 4.7 - µs

Acknowledge Delay from SCL Falling tack 300 1000 ns

Delay from Supply Voltage Stable to Control Port Ready tdpor 100 - µs

tbuf thdst thdst

tlow tr

tf

thdd

thigh

tsud tsust

tsusp

Stop Start

Start Stop

Repeated

SDA

SCL

VD tdpor

Figure 5. Control Port Timing - I²C Format

CS2100-CP

10 DS840F3

CONTROL PORT SWITCHING CHARACTERISTICS - SPI FORMAT

Inputs: Logic 0 = GND; Logic 1 = VD; CL=20pF.

Notes: 14. tspi is only needed before first falling edge of CS after power is applied. tspi = 0 at all other times.

15. Data must be held for sufficient time to bridge the transition time of CCLK.

16. For fcclk < 1 MHz.

Parameter Symbol Min Max Unit

CCLK Clock Frequency fccllk -6MHz

CCLK Edge to CS Falling (Note 14)t

spi 500 - ns

CS High Time Between Transmissions tcsh 1.0 - µs

CS Falling to CCLK Edge tcss 20 - ns

CCLK Low Time tscl 66 - ns

CCLK High Time tsch 66 - ns

CDIN to CCLK Rising Setup Time tdsu 40 - ns

CCLK Rising to DATA Hold Time (Note 15)t

dh 15 - ns

Rise Time of CCLK and CDIN (Note 16)t

r2 - 100 ns

Fall Time of CCLK and CDIN (Note 16)t

f2 - 100 ns

Delay from Supply Voltage Stable to Control Port Ready tdpor 100 - µs

tr2 tf2

tdsu tdh

tsch

tscl

CS

CCLK

CDIN

tcss tcsh

tspi

tdpor

VD

Figure 6. Control Port Timing - SPI Format (Write Only)

CS2100-CP

DS840F3 11

4. ARCHITECTURE OVERVIEW

4.1 Delta-Sigma Fractional-N Frequency Synthesizer

The core of the CS2100 is a Delta-Sigma Fractional-N Frequency Synthesizer which has very high-resolu-

tion for Input/Output clock ratios, low phase noise, very wide range of output frequencies and the ability to

quickly tune to a new frequency. In very simplistic terms, the Fractional-N Frequency Synthesizer multiplies

the Timing Reference Clock by the value of N to generate the PLL output clock. The desired output to input

clock ratio is the value of N that is applied to the delta-sigma modulator (see Figure 7).

The analog PLL based frequency synthesizer uses a low-jitter timing reference clock as a time and phase

reference for the internal voltage controlled oscillator (VCO). The phase comparator compares the fraction-

al-N divided clock with the original timing reference and generates a control signal. The control signal is fil-

tered by the internal loop filter to generate the VCO’s control voltage which sets its output frequency. The

delta-sigma modulator modulates the loop integer divide ratio to get the desired fractional ratio between the

reference clock and the VCO output (thus the one’s density of the modulator sets the fractional value). This

allows the design to be optimized for very fast lock times for a wide range of output frequencies without the

need for external filter components. As with any Fractional-N Frequency Synthesizer the timing reference

clock should be stable and jitter-free.

Figure 7. Delta-Sigma Fractional-N Frequency Synthesizer

4.2 Hybrid Analog-Digital Phase Locked Loop

The addition of the Digital PLL and Fractional-N Logic (shown in Figure 8) to the Fractional-N Frequency

Synthesizer creates the Hybrid Analog-Digital Phase Locked Loop with many advantages over classical an-

alog PLL techniques. These advantages include the ability to operate over extremely wide frequency ranges

without the need to change external loop filter components while maintaining impressive jitter reduction per-

formance. In the Hybrid architecture, the Digital PLL calculates the ratio of the PLL output clock to the fre-

quency reference and compares that to the desired ratio. The digital logic generates a value of N which is

then applied to the Fractional-N frequency synthesizer to generate the desired PLL output frequency. Notice

that the frequency and phase of the timing reference signal do not affect the output of the PLL since the

digital control loop will correct for the PLL output. A major advantage of the Digital PLL is the ease with which

the loop filter bandwidth can be altered. The PLL bandwidth is automatically set to a wide-bandwidth mode

to quickly achieve lock and then reduced for optimal jitter rejection.

Fractional-N

Divider

Timing Reference

Clock PLL Output

Voltage Controlled

Oscillator

Internal

Loop Filter

Phase

Comparator

N

Delta-Sigma

Modulator

CS2100-CP

12 DS840F3

Figure 8. Hybrid Analog-Digital PLL

N

Digital Filter

Frequency

Comparator for

Frac-N Generation

Frequency Reference

Clock

Delta-Sigma Fractional-N Frequency Synthesizer

Digital PLL and Fractional-N Logic

Output to Input Ratio for Hybrid mode

Fractional-N

Divider

Timing Reference

Clock PLL Output

Voltage Controlled

Oscillator

Internal

Loop Filter

Phase

Comparator

Delta-Sigma

Modulator

CS2100-CP

DS840F3 13

5. APPLICATIONS

5.1 Timing Reference Clock Input

The low jitter timing reference clock (RefClk) can be provided by either an external reference clock or an

external crystal in conjunction with the internal oscillator. In order to maintain a stable and low-jitter PLL out-

put the timing reference clock must also be stable and low-jitter; the quality of the timing reference clock

directly affects the performance of the PLL and hence the quality of the PLL output.

5.1.1 Internal Timing Reference Clock Divider

The Internal Timing Reference Clock (SysClk) has a smaller maximum frequency than what is allowed on

the XTI/REF_CLK pin. The CS2100 supports the wider external frequency range by offering an internal

divider for RefClk. The RefClkDiv[1:0] bits should be set such that SysClk, the divided RefClk, then falls

within the valid range as indicated in “AC Electrical Characteristics” on page 7.

It should be noted that the maximum allowable input frequency of the XTI/REF_CLK pin is dependent

upon its configuration as either a crystal connection or external clock input. See the “AC Electrical Char-

acteristics” on page 7 for more details.

For the lowest possible output jitter, attention should be paid to the absolute frequency of the Timing Ref-

erence Clock relative to the PLL Output frequency (CLK_OUT). To minimize output jitter, the Timing Ref-

erence Clock frequency should be chosen such that fRefClk is at least +/-15 kHz from fCLK_OUT*N/32

where N is an integer. Figure 10 shows the effect of varying the RefClk frequency around fCLK_OUT*N/32.

It should be noted that there will be a jitter null at the zero point when N = 32 (not shown in Figure 10). An

example of how to determine the range of RefClk frequencies around 12 MHz to be used in order to

achieve the lowest jitter PLL output at a frequency of 12.288 MHz is as follows:

where:

and

Referenced Control Register Location

RefClkDiv[1:0] .......................“Reference Clock Input Divider (RefClkDiv[1:0])” on page 28

Figure 9. Internal Timing Reference Clock Divider

N

Internal Timing

Reference Clock

PLL Output

Fractional-N

Frequency

Synthesizer

Timing Reference

Clock Divider

1

2

4

XTI/REF_CLK

RefClkDiv[1:0]

8 MHz < SysClk < 18.75 MHz

8 MHz < RefClk <

Timing Reference Clock

50 MHz (XTI)

75 MHz (REF_CLK)

-80 -60 -40 -20 0 20 40 60 80

20

40

60

80

100

120

140

160

180

Normalized REF__CLK Frequency (kHz)

Typical Base Band Jitter (psec)

CLK__OUT Jit ter

-15 kHz +15 kHz

CLK__OUT

f *32/N

Figure 10. REF_CLK Frequency vs. a Fixed CLK_OUT

fLfRefClk fH

fLfCLK_OUT 31

32

------15kHz+=

12.288MHz 0.96875 15kHz+=

11.919MHz=

fHfCLK_OUT 32

32

------15kHz–=

12.288MHz 115kHz+=

12.273MHz=

CS2100-CP

14 DS840F3

5.1.2 Crystal Connections (XTI and XTO)

An external crystal may be used to generate RefClk. To accomplish this, a 20 pF fundamental mode par-

allel resonant crystal must be connected between the XTI and XTO pins as shown in Figure 11. As shown,

nothing other than the crystal and its load capacitors should be connected to XTI and XTO. Please refer

to the “AC Electrical Characteristics” on page 7 for the allowed crystal frequency range.

5.1.3 External Reference Clock (REF_CLK)

For operation with an externally generated REF_CLK signal, XTI/REF_CLK should be connected to the

reference clock source and XTO should be left unconnected or pulled low through a 47 kresistor to

GND.

5.2 Frequency Reference Clock Input, CLK_IN

The frequency reference clock input (CLK_IN) is used by the Digital PLL and Fractional-N Logic block to

dynamically generate a fractional-N value for the Frequency Synthesizer (see “Hybrid Analog-Digital PLL”

on page 12). The Digital PLL first compares the CLK_IN frequency to the PLL output. The Fractional-N logic

block then translates the desired ratio based off of CLK_IN to one based off of the internal timing reference

clock (SysClk). This allows the low-jitter timing reference clock to be used as the clock which the Frequency

Synthesizer multiplies while maintaining synchronicity with the frequency reference clock through the Digital

PLL. The allowable frequency range for CLK_IN is found in the “AC Electrical Characteristics” on page 7.

5.2.1 CLK_IN Skipping Mode

CLK_IN skipping mode allows the PLL to maintain lock even when the CLK_IN signal has missing pulses

for up to 20 ms (tCS) at a time (see “AC Electrical Characteristics” on page 7 for specifications). CLK_IN

skipping mode can only be used when the CLK_IN frequency is below 80 kHz and CLK_IN is reapplied

within 20 ms of being removed. The ClkSkipEn bit enables this function.

Regardless of the setting of the ClkSkipEn bit the PLL output will continue for 223 SysClk cycles (466 ms

to 1048 ms) after CLK_IN is removed (see Figure 12). This is true as long as CLK_IN does not glitch or

have an effective change in period as the clock source is removed, otherwise the PLL will interpret this as

a change in frequency causing clock skipping and the 223 SysClk cycle time-out to be bypassed and the

PLL to immediately unlock. If the prior conditions are met while CLK_IN is removed and 223 SysClk cycles

pass, the PLL will unlock and the PLL_OUT state will be determined by the ClkOutUnl bit; See “PLL Clock

Output” on page 20. If CLK_IN is re-applied after such time, the PLL will remain unlocked for the specified

time listed in the “AC Electrical Characteristics” on page 7 after which lock will be acquired and the PLL

XTI XTO

40 pF 40 pF

Figure 11. External Component Requirements for Crystal Circuit

CS2100-CP

DS840F3 15

output will resume.

If it is expected that CLK_IN will be removed and then reapplied within 223 SysClk cycles but later than

tCS, the ClkSkipEn bit should be disabled. If it is not disabled, the device will behave as shown in

Figure 13; note that the lower figure shows that the PLL output frequency may change and be incorrect

without an indication of an unlock condition.

Figure 12. CLK_IN removed for > 223 SysClk cycles

CLK_IN

PLL_OUT

UNLOCK

ClkSkipEn=0 or 1

ClkOutUnl=0

Lock Time

CLK_IN

PLL_OUT

UNLOCK

ClkSkipEn=0 or 1

ClkOutUnl=1

Lock Time

= invalid clocks

223 SysClk cycles 223 SysClk cycles

CLK_IN

PLL_OUT

UNLOCK

ClkSkipEn=0 or 1

ClkOutUnl=0

Lock Time

CLK_IN

PLL_OUT

UNLOCK

ClkSkipEn=0 or 1

ClkOutUnl=1

Lock Time

tCS tCS

= invalid clocks

CLK_IN

PLL_OUT

UNLOCK

ClkSkipEn= 1

ClkOutUnl= 0 or 1

Lock Time

tCS

= invalid clocks

223 SysClk cycles 223 SysClk cycles

223 SysClk cycles

Figure 13. CLK_IN removed for < 223 SysClk cycles but > tCS

CS2100-CP

16 DS840F3

If CLK_IN is removed and then re-applied within tCS, the ClkSkipEn bit determines whether PLL_OUT

continues while the PLL re-acquires lock (see Figure 14). When ClkSkipEn is disabled and CLK_IN is re-

moved the PLL output will continue until CLK_IN is re-applied at which point the PLL will go unlocked only

for the time it takes to acquire lock; the PLL_OUT state will be determined by the ClkOutUnl bit during this

time. When ClkSkipEn is enabled and CLK_IN is removed the PLL output clock will remain continuous

throughout the missing CLK_IN period including the time while the PLL re-acquires lock.

5.2.2 Adjusting the Minimum Loop Bandwidth for CLK_IN

The CS2100 allows the minimum loop bandwidth of the Digital PLL to be adjusted between 1 Hz and 128

Hz using the ClkIn_BW[2:0] bits. The minimum loop bandwidth of the Digital PLL directly affects the jitter

transfer function; specifically, jitter frequencies below the loop bandwidth corner are passed from the PLL

input directly to the PLL output without attenuation. In some applications it is desirable to have a very low

minimum loop bandwidth to reject very low jitter frequencies, commonly referred to as wander. In others

it may be preferable to remove only higher frequency jitter, allowing the input wander to pass through the

PLL without attenuation.

Typically, applications in which the PLL_OUT signal creates a new clock domain from which all other sys-

tem clocks and associated data are derived will benefit from the maximum jitter and wander rejection of

Referenced Control Register Location

ClkSkipEn..............................“Clock Skip Enable (ClkSkipEn)” on page 28

ClkOutUnl..............................“Enable PLL Clock Output on Unlock (ClkOutUnl)” on page 29

Figure 14. CLK_IN removed for < tCS

CLK_IN

PLL_OUT

UNLOCK

ClkSkipEn=1

ClkOutUnl=0 or 1

CLK_IN

PLL_OUT

UNLOCK

ClkSkipEn=0

ClkOutUnl=1

Lock Time

CLK_IN

PLL_OUT

UNLOCK

ClkSkipEn=0

ClkOutUnl=0

Lock Time

tCS tCS

tCS

= invalid clocks

CS2100-CP

DS840F3 17

the lowest PLL bandwidth setting. See Figure 15.

Systems in which some clocks and data are derived from the PLL_OUT signal while other clocks and data

are derived from the CLK_IN signal will often require phase alignment of all the clocks and data in the

system. See Figure 16. If there is substantial wander on the CLK_IN signal in these applications, it may

be necessary to increase the minimum loop bandwidth allowing this wander to pass through to the

CLK_OUT signal in order to maintain phase alignment. For these applications, it is advised to experiment

with the loop bandwidth settings and choose the lowest bandwidth setting that does not produce system

timing errors due to wandering between the clocks and data synchronous to the CLK_IN domain and

those synchronous to the PLL_OUT domain.

It should be noted that manual adjustment of the minimum loop bandwidth is not necessary to acquire

lock; this adjustment is made automatically by the Digital PLL. While acquiring lock, the digital loop band-

width is automatically set to a large value. Once lock is achieved, the digital loop bandwidth will settle to

the minimum value selected by the ClkIn_BW[2:0] bits.

5.3 Output to Input Frequency Ratio Configuration

5.3.1 User Defined Ratio (RUD)

The User Defined Ratio, RUD, is a 32-bit un-signed fixed-point number, stored in the Ratio register set,

which determines the basis for the desired input to output clock ratio. The 32-bit RUD can be expressed

Referenced Control Register Location

ClkIn_BW[2:0] ....................... “Clock Input Bandwidth (ClkIn_BW[2:0])” on page 29

Figure 15. Low bandwidth and new clock domain

LRCK

SCLK

SDATA

MCLK

MCLK

Wander > 1 Hz

Wander and Jitter > 1 Hz Rejected

D0 D1

LRCK

SCLK

SDATA

Subclocks generated

from new clock domain.

or

PLL

BW = 1 Hz

CLK_IN PLL_OUT

D0 D1

Jitter

Figure 16. High bandwidth with CLK_IN domain re-use

D0 D1

LRCK

SCLK

SDATA

MCLK

MCLK

Wander < 128 Hz

Jitter > 128 Hz Rejected

Wander < 128 Hz Passed to Output

LRCK

SCLK

SDATA

or

PLL

BW = 128 Hz

CLK_IN PLL_OUT

Subclocks and data re-used

from previous clock domain.

Jitter

D0 D1

CS2100-CP

18 DS840F3

in either a high resolution (12.20) or high multiplication (20.12) format selectable by the LFRatioCfg bit,

with 20.12 being the default.

The RUD for high resolution (12.20) format is encoded with 12 MSBs representing the integer binary por-

tion with the remaining 20 LSBs representing the fractional binary portion. The maximum multiplication

factor is approximately 4096 with a resolution of 0.954 PPM in this configuration. See “Calculating the

User Defined Ratio” on page 30 for more information.

The RUD for high multiplication (20.12) format is encoded with 20 MSBs representing the integer binary

portion with the remaining 12 LSBs representing the fractional binary portion. In this configuration, the

maximum multiplication factor is approximately 1,048,575 with a resolution of 244 PPM. It is recommend-

ed that the 12.20 High-Resolution format be utilized whenever the desired ratio is less than 4096 since

the output frequency accuracy of the PLL is directly proportional to the accuracy of the timing reference

clock and the resolution of the RUD.

The status of internal dividers, such as the internal timing reference clock divider, are automatically taken

into account. Therefore RUD is simply the desired ratio of the output to input clock frequencies.

5.3.2 Ratio Modifier (R-Mod)

The Ratio Modifier is used to internally multiply/divide the RUD (the Ratio stored in the register space re-

mains unchanged). The available options for RMOD are summarized in Table 1 on page 18.

The R-Mod value selected by RModSel[2:0] is always used in the calculation for the Effective Ratio

(REFF), see “Effective Ratio (REFF)” on page 19. If R-Mod is not desired, RModSel[2:0] should be left at

its default value of ‘000’, which corresponds to an R-Mod value of 1, thereby effectively disabling the ratio

modifier.

Table 1. Ratio Modifier

Referenced Control Register Location

Ratio......................................“Ratio (Address 06h - 09h)” on page 27

LFRatioCfg ............................ “Low-Frequency Ratio Configuration (LFRatioCfg)” on page 29

RModSel[2:0] Ratio Modifier

000 1

001 2

010 4

011 8

100 0.5

101 0.25

110 0.125

111 0.0625

Referenced Control Register Location

Ratio......................................“Ratio (Address 06h - 09h)” on page 27

RModSel[2:0] ........................“R-Mod Selection (RModSel[2:0])” section on page 26

CS2100-CP

DS840F3 19

5.3.3 Effective Ratio (REFF)

The Effective Ratio (REFF) is an internal calculation comprised of RUD and the appropriate modifiers, as

previously described. REFF is calculated as follows:

REFF = RUD RMOD

To simplify operation the device handles some of the ratio calculation functions automatically (such as

when the internal timing reference clock divider is set). For this reason, the Effective Ratio does not need

to be altered to account for internal dividers.

Ratio modifiers which would produce an overflow or truncation of REFF should not be used; For example

if RUD is 1024 an RMOD of 8 would produce an REFF value of 8192 which exceeds the 4096 limit of the

12.20 format. In all cases, the maximum and minimum allowable values for REFF are dictated by the fre-

quency limits for both the input and output clocks as shown in the “AC Electrical Characteristics” on

page 7.

5.3.4 Ratio Configuration Summary

The RUD is the user defined ratio stored in the register space. The resolution for the RUD is selectable by

setting LFRatioCfg. R-Mod is applied if selected. The user defined ratio, and ratio modifier make up the

effective ratio REFF, the final calculation used to determine the output to input clock ratio. The effective

ratio is then corrected for the internal dividers. The conceptual diagram in Figure 17 summarizes the fea-

tures involved in the calculation of the ratio values used to generate the fractional-N value which controls

the Frequency Synthesizer.

Figure 17. Ratio Feature Summary

Referenced Control Register Location

Ratio......................................“Ratio (Address 06h - 09h)” on page 27

LFRatioCfg ............................ “Low-Frequency Ratio Configuration (LFRatioCfg)” on page 29

RModSel[2:0] ........................“R-Mod Selection (RModSel[2:0])” section on page 26

RefClkDiv[1:0] .......................“Reference Clock Input Divider (RefClkDiv[1:0])” on page 28

Effective Ratio REFF

Ratio Format

Frequency Reference Clock

(CLK_IN)

SysClk PLL Output

Frequency

Synthesizer

Digital PLL &

Fractional N Logic

N

Ratio 12.20

20.12

LFRatioCfg

RModSel[2:0]

Ratio

Modifier R Correction

RefClkDiv[1:0]

Timing Reference Clock

(XTI/REF_CLK) Divide

RefClkDiv[1:0]

User Defined Ratio RUD

CS2100-CP

20 DS840F3

5.4 PLL Clock Output

The PLL clock output pin (CLK_OUT) provides a buffered version of the output of the frequency synthesizer.

The driver can be set to high-impedance with the ClkOutDis bit.

The output from the PLL automatically drives a static low condition while the PLL is un-locked (when the

clock may be unreliable). This feature can be disabled by setting the ClkOutUnl bit, however the state

CLK_OUT may then be unreliable during an unlock condition.

Figure 18. PLL Clock Output Options

5.5 Auxiliary Output

The auxiliary output pin (AUX_OUT) can be mapped, as shown in Figure 19, to one of four signals: refer-

ence clock (RefClk), input clock (CLK_IN), additional PLL clock output (CLK_OUT), or a PLL lock indicator

(Lock). The mux is controlled via the AuxOutSrc[1:0] bits. If AUX_OUT is set to Lock, the AuxLockCfg bit is

then used to control the output driver type and polarity of the LOCK signal (see section 8.6.2 on page 28).

In order to indicate an unlock condition, REF_CLK must be present. If AUX_OUT is set to CLK_OUT the

phase of the PLL Clock Output signal on AUX_OUT may differ from the CLK_OUT pin. The driver for the

pin can be set to high-impedance using the AuxOutDis bit.

Figure 19. Auxiliary Output Selection

Referenced Control Register Location

ClkOutUnl..............................“Enable PLL Clock Output on Unlock (ClkOutUnl)” on page 29

ClkOutDis .............................. “PLL Clock Output Disable (ClkOutDis)” on page 26

Referenced Control Register Location

AuxOutSrc[1:0]......................“Auxiliary Output Source Selection (AuxOutSrc[1:0])” on page 26

AuxOutDis ............................. “Auxiliary Output Disable (AuxOutDis)” on page 25

AuxLockCfg...........................“AUX PLL Lock Output Configuration (AuxLockCfg)” section on page 28

PLL Locked/Unlocked

PLL Output

2:1 Mux

ClkOutDis

2:1 Mux

ClkOutUnl

0

PLL Clock Output Pin

(CLK_OUT)

0

1

0

1

PLL Clock Output

PLLClkOut

Frequency Reference Clock

(CLK_IN)

PLL Lock/Unlock Indication

(Lock)

Timing Reference Clock

(RefClk)

PLL Clock Output

(PLLClkOut)

4:1 Mux Auxiliary Output Pin

(AUX_OUT)

AuxOutDis

AuxOutSrc[1:0]

AuxLockCfg

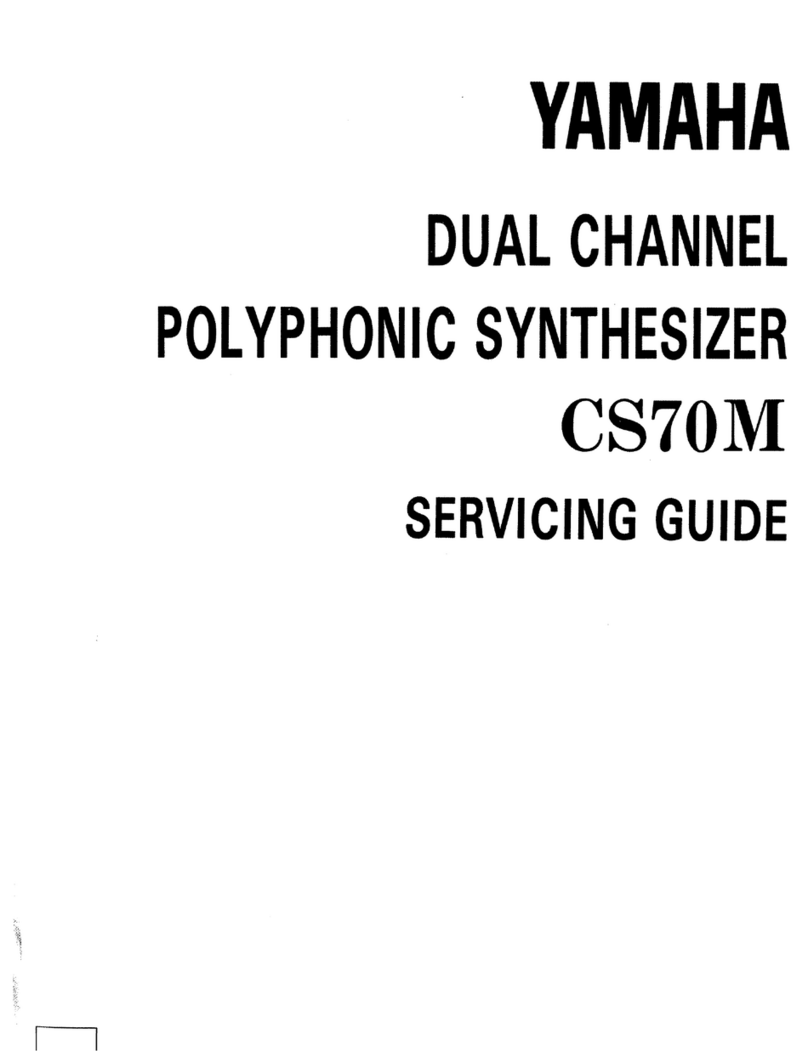

This manual suits for next models

2

Table of contents

Other Cirrus Logic Synthesizer manuals