Crystal CS4392 User manual

Advance Product Information

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

1

Copyright

Cirrus Logic, Inc. 2000

(All Rights Reserved)

P.O. Box 17847, Austin, Texas 78760

(512) 445 7222 FAX: (512) 445 7581

http://www.cirrus.com

CS4392

24-Bit, 192 kHz Stereo DAC with Volume Control

Features

lComplete StereoDAC System: Interpolation,

D/A, Output Analog Filtering

l114 dB Dynamic Range

l100 dB THD+N

lUp to 192kHz Sample Rates

lDirect Stream Digital Mode

lLow Clock Jitter Sensitivity

lSingle +5 V Power Supply

lSelectable Digital Filters

– Fast and Slow roll-off

lVolume Control with Soft Ramp

– 1 dB Step Size

– Zero Crossing Click-Free Transitions

lDirect Interface with 5 V to 1.8 V Logic

lATAPI mixing functions

lPin compatible with the CS4391

Description

The CS4392 is a complete stereo digital-to-analog sys-

tem including digital interpolation, fifth-order delta-sigma

digital-to-analog conversion, digital de-emphasis, vol-

ume control, channel mixing and analog filtering. The

advantages of this architecture include: ideal differential

linearity, no distortion mechanisms due to resistor

matching errors, no linearity drift over time and tempera-

ture, and a high tolerance to clock jitter.

The CS4392 accepts PCM data at sample rates from

4 kHz to 192 kHz, DSD audio data, has selectable digital

filters, and consumes very little power. These features

are ideal for DVD, SACD players, A/V receivers, CD and

set-top box systems. The CS4392 is pin and register

compatible with the CS4391, making easy performance

upgrades possible.

ORDERING INFORMATION

CS4392-KS -10 to 70 °C 20-pin SOIC

CS4392-KZ -10 to 70 °C 20-pinTSSOP

CDB4392 Evaluation Board

I

LRCK

SDATA

(SDA/CDIN)

MCLK

AMUTEC

AOUTA-

AOUTB-

SERIAL

PORT

INTERPOLATION

INTERPOLATOR

(CONTROL PORT)

∆Σ

DAC

DAC

EXTERNAL

ANALOG

FILTER

ANALOG

FILTER

∆Σ

MUTE CONTROL

FILTER

FILTER

RST

SCLK

VOLUME

CONTROL

VOLUME

CONTROL

MIXER

(SCL/CCLK) (AD0/CS)

AOUTA+

AOUTB+

CMOUT

REFERENCE

FILT+BMUTEC

M1 M3 M2

MODE SELECT

M0

OCT ‘00

DS459PP1

CS4392

2DS459PP1

TABLE OF CONTENTS

1. CHARACTERISTICS/SPECIFICATIONS .................................................................................5

ANALOG CHARACTERISTICS................................................................................................5

POWER AND THERMAL CHARACTERISTICS.......................................................................7

DIGITAL CHARACTERISTICS.................................................................................................8

ABSOLUTE MAXIMUM RATINGS ...........................................................................................8

RECOMMENDED OPERATING CONDITIONS.......................................................................8

SWITCHING CHARACTERISTICS - PCM MODES.................................................................9

SWITCHING CHARACTERISTICS - DSD..............................................................................10

SWITCHING CHARACTERISTICS - CONTROL PORT - TWO-WIRE MODE.......................11

SWITCHING CHARACTERISTICS - CONTROL PORT - SPI MODE....................................12

2. TYPICAL CONNECTION DIAGRAMS ...................................................................................13

3. REGISTER QUICK REFERENCE ..........................................................................................15

4. REGISTER DESCRIPTION ....................................................................................................16

4.1 Mode Control 1 - Address 01h .........................................................................................16

4.1.1 Auto-Mute (Bit 7) .................................................................................................16

4.1.2 Digital Interface Formats (Bits 6:4) ......................................................................16

4.1.3 De-Emphasis Control (Bits 3:2) ...........................................................................17

4.1.4 Functional Mode (Bits 1:0) ..................................................................................17

4.2 Volume and Mixing Control (Address 02h) ......................................................................18

4.2.1 Channel A Volume = Channel B Volume (Bit 7) .................................................18

4.2.2 Soft Ramp or Zero Cross Enable (Bits 6:5) .........................................................18

4.2.3 ATAPI Channel Mixing and Muting (Bits 4:0) ......................................................18

4.3 Channel A Volume Control - Address 03h .......................................................................20

4.4 Channel B Volume Control - Address 04h........................................................................20

4.4.1 Mute (Bit 7) ..........................................................................................................20

4.4.2 Volume Control (Bits 6:0) ....................................................................................20

4.5 Mode Control 2 - Address 05h .........................................................................................20

4.5.1 Invert Signal Polarity (Bits 7:6) ............................................................................20

4.5.2 Control Port Enable (Bit 5) ..................................................................................21

4.5.3 Power Down (Bit 4) .............................................................................................21

4.5.4 AMUTEC = BMUTEC (Bit 3) ...............................................................................21

4.5.5 Freeze (Bit 2) ......................................................................................................21

4.5.6 Master Clock Divide (Bit 1) ..................................................................................21

Contacting Cirrus Logic Support

For a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at:

http://www.cirrus.com/corporate/contacts/sales.cfm

I

2

C is a registered trademark of Philips Semiconductors.

Preliminary product information describes products which are in production, but for which full characterization data is not yetavailable. Advance product infor-

mation describes products which are in development and subject to development changes. Cirrus Logic, Inc. has made best efforts to ensure that the information

contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided “AS IS” without warranty of

any kind (express or implied). No responsibility is assumed by Cirrus Logic, Inc. for the use of this information, nor for infringements of patents or other rights

of third parties. This document is the property of Cirrus Logic, Inc. and implies no license under patents, copyrights, trademarks, or trade secrets. No part of

this publication may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or

otherwise) without the prior written consent of Cirrus Logic, Inc. Items from any Cirrus Logic website or disk may be printed for use by the user. However, no

part of the printout or electronic files may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical,

photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc.Furthermore, no part of this publication maybe used as a basis for manufacture

or sale of any items without the prior written consent of Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or other vendors and suppliers appearing

in this document may be trademarks or service marks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. trade-

marks and service marks can be found at http://www.cirrus.com.

CS4392

DS459PP1 3

4.6 Mode Control 3 - Address 06h ......................................................................................... 21

4.6.1 Interpolation Filter Select (Bit 4) .......................................................................... 21

4.6.2 Soft Volume Ramp-up after Reset (Bit 3) ........................................................... 22

4.6.3 Soft Ramp-down before Reset (Bit 2) ................................................................. 22

4.7 Chip ID - Register 07h .....................................................................................................22

5. PIN DESCRIPTION - PCM DATA MODE ............................................................................... 23

6. PIN DESCRIPTION - DSD MODE .......................................................................................... 27

7. APPLICATIONS ..................................................................................................................... 31

7.1 Recommended Power-up Sequence for Hardware Mode ............................................... 31

7.2 Recommended Power-up Sequence and Access to Control Port Mode ......................... 31

7.3 Analog Output and Filtering ............................................................................................. 31

7.4 Interpolation Filter ............................................................................................................ 31

8. CONTROL PORT INTERFACE .............................................................................................. 33

8.1 SPI Mode ......................................................................................................................... 33

8.2 Two-Wire Mode ............................................................................................................... 33

9. PARAMETER DEFINITIONS .................................................................................................. 35

Total Harmonic Distortion + Noise (THD+N) ................................................................... 35

Dynamic Range ............................................................................................................... 35

Interchannel Isolation ...................................................................................................... 35

Interchannel Gain Mismatch ........................................................................................... 35

Gain Error........................................................................................................................ 35

Gain Drift ......................................................................................................................... 35

10. REFERENCES ...................................................................................................................... 35

11. PACKAGE DIMENSIONS ................................................................................................. 36

CS4392

4DS459PP1

LIST OF TABLES

Table 1. Digital Interface Formats - PCM Modes ..........................................................................16

Table 2. Digital Interface Formats - DSD Mode ............................................................................17

Table 3. De-Emphasis Mode Selection........................................................................................17

Table 4. Functional Mode Selection..............................................................................................17

Table 5. Soft Cross or Zero Cross Mode Selection......................................................................18

Table 6. ATAPI Decode.................................................................................................................19

Table 7. Digital Volume Control Example Settings........................................................................20

Table 8. Common Clock Frequencies...........................................................................................24

Table 9. Single Speed (4 to 50 kHz) Digital Interface Format, Stand-Alone Mode Options..........25

Table 10. Single Speed Only (4 to 50 kHz) De-Emphasis, Stand-Alone Mode Options...............25

Table 11. Double Speed (50 to 100 kHz) Digital Interface Format, Stand-Alone Mode Options ..25

Table 12. Quad Speed (100 to 200 kHz) Digital Interface Format, Stand-Alone Mode Options...25

Table 13. Direct Stream Digital (DSD), Stand-Alone Mode Options .............................................28

Table 14. Memory Address Pointer (MAP)....................................................................................34

LIST OF FIGURES

Figure 1. Serial Mode Input Timing .................................................................................................9

Figure 2. Direct Stream Digital - Serial Audio Input Timing...........................................................10

Figure 3. Two-Wire Mode Control Port Timing..............................................................................11

Figure 4. SPI Control Port Timing .................................................................................................12

Figure 5. Typical Connection Diagram - PCM Mode.....................................................................13

Figure 6. Typical Connection Diagram - DSD Mode.....................................................................14

Figure 7. De-Emphasis Curve.......................................................................................................17

Figure 8. ATAPI Block Diagram ....................................................................................................19

Figure 9. Format 0, Left Justified up to 24-Bit Data.......................................................................29

Figure 10. Format 1, I2S up to 24-Bit Data ...................................................................................29

Figure 11. Format 2, Right Justified 16-Bit Data...........................................................................29

Figure 12. Format 3, Right Justified 24-Bit Data...........................................................................29

Figure 13. Format 4, Right Justified 20-Bit Data. (Available in Control Port Mode only)..............30

Figure 14. Format 5, Right Justified 18-Bit Data. (Available in Control Port Mode only)...............30

Figure 15. CS4392 Output Filter ...................................................................................................32

Figure 16. Control Port Timing, SPI mode ....................................................................................34

Figure 17. Control Port Timing, Two-Wire Mode...........................................................................34

CS4392

DS459PP1 5

1. CHARACTERISTICS/SPECIFICATIONS

ANALOG CHARACTERISTICS (TA= 25° C; Logic "1" = VL = VA; Logic "0" = AGND; Full-Scale Out-

put Sine Wave, 997 Hz; MCLK = 12.288 MHz; SCLK = 3.072 MHz, Sample Rate = 48, 96, or 192 kHz, 24-bit data,

Measurement Bandwidth 10 Hz to 20 kHz, unless otherwise specified. Test load RL= 3 kΩ, CL= 10 pF)

Parameter

VA = 5 V

Symbol Min Typ Max Unit

Dynamic Performance - Single Speed Mode (48kHz)

Dynamic Range (Note 1) unweighted

A-Weighted TBD

TBD 111

114 -

-dB

dB

Total Harmonic Distortion + Noise (Note 1) 0 dB

-20 dB

-60 dB

THD+N -

-

-

-100

-91

-51

TBD

-

TBD

dB

dB

dB

Idle Channel Noise / Signal-to-Noise Ratio - 114 - dB

Interchannel Isolation (1 kHz) - 100 - dB

Dynamic Performance - Double Speed Mode (96kHz)

Dynamic Range (Note 1) unweighted

A-Weighted TBD

TBD 111

114 -

-dB

dB

Total Harmonic Distortion + Noise (Note 1) 0 dB

-20 dB

-60 dB

THD+N -

-

-

-100

-91

-51

TBD

-

TBD

dB

dB

dB

Idle Channel Noise / Signal-to-Noise Ratio - 114 - dB

Interchannel Isolation (1 kHz) - 100 - dB

Dynamic Performance - Quad Speed Mode (192kHz)

Dynamic Range (Note 1) unweighted

A-Weighted TBD

TBD 111

114 -

-dB

dB

Total Harmonic Distortion + Noise (Note 1) 0 dB

-20 dB

-60 dB

THD+N -

-

-

-100

-91

-51

TBD

-

TBD

dB

dB

dB

Idle Channel Noise / Signal-to-Noise Ratio - 114 - dB

Interchannel Isolation (1 kHz) - 100 - dB

Parameter Symbol Min Typ Max Units

Analog Output

Full Scale Differential Output Voltage TBD 1.0xVA TBD Vpp

Common Mode Voltage CMOUT - 0.5xVA - VDC

Interchannel Gain Mismatch - 0.1 - dB

Gain Drift - 100 - ppm/°C

AC-Load Resistance RL3--kΩ

Load Capacitance CL--100pF

CS4392

6DS459PP1

ANALOG CHARACTERISTICS (continued)

Notes: 1. Triangular PDF dithered data.

2. Filter response is not tested but is guaranteed by design.

3. Valid with the recommended capacitor values on FILT+ and CMOUT as shown in Figure 5. Increasing

the capacitance will also increase the PSRR.

4. Response is clock dependent and will scale with Fs.

5. For Single-Speed Mode, the Measurement Bandwidth is 0.5465 Fs to 3 Fs.

For Double-Speed Mode, the Measurement Bandwidth is 0.577 Fs to 1.4 Fs.

Parameter Symbol Fast Roll-Off Slow Roll-Off UnitMin Typ Max Min Typ Max

Combined Digital and On-chip Analog Filter Response - Single Speed Mode (Note2)

Passband (Note 3) to -0.01 dB corner

to -3 dB corner 0

0-

-.4535

.4998 0

0-

-0.4166

0.4998 Fs

Fs

Frequency Response 10 Hz to 20 kHz -0.01 - +0.01 -0.01 - +0.01 dB

StopBand .5465 - - .5834 - - Fs

StopBand Attenuation (Note 5) 90 - - 64 - - dB

Group Delay tgd - TBD - - TBD - s

Passband Group Delay Deviation 0 - 20 kHz - - TBD - TBD s

De-emphasis Error Fs = 32 kHz

(Relative to 1kHz) Fs = 44.1 kHz

Fs = 48 kHz

-

-

-

-

-

-

±0.23

±0.14

±0.09

-

-

-

-

-

-

±0.23

±0.14

±0.09

dB

dB

dB

Combined Digital and On-chip Analog Filter Response - Double Speed Mode - 96kHz (Note 2)

Passband (Note 4) to -0.01 dB corner

to -3 dB corner 0

0-

-.4166

.4998 0

0-

-.2083

.4998 Fs

Fs

Frequency Response 10 Hz to 20 kHz -0.01 - 0.01 -0.01 - 0.01 dB

StopBand .5834 - - .7917 - - Fs

StopBand Attenuation (Note 5) 80 - - 70 - - dB

Group Delay tgd - TBD - - TBD - s

Passband Group Delay Deviation 0 - 20 kHz - - TBD - - TBD s

Combined Digital and On-chip Analog Filter Response - Quad Speed Mode - 192kHz (Note 2)

Passband (Note 4) to -0.01 dB corner

to -3 dB corner 0

0-

-.1046

.4897 0

0-

-.1042

.4813 Fs

Fs

Frequency Response 10 Hz to 20 kHz -0.01 - 0.01 -0.01 - 0.01 dB

StopBand .6355 - - .8683 - - Fs

StopBand Attenuation (Note 5) 75 - - 75 - - dB

Group Delay tgd - TBD - - TBD - s

Passband Group Delay Deviation 0 - 20 kHz - - TBD - - TBD s

Combined Digital and On-chip Analog Filter Response - DSD Mode (Note 2)

Passband (Note 4) to -3 dB corner TBD - TBD TBD - TBD Fs

Frequency Response 10 Hz to 20 kHz TBD - TBD TBD - TBD dB

CS4392

DS459PP1 7

POWER AND THERMAL CHARACTERISTICS GND = 0 V ( All voltages with respect to

ground. All measurements taken with all zeros input and open outputs, unless otherwise specified.)

Notes: 6. GND = 0 V ( All voltages with respect to ground. All measurements taken with all zeros input and open

outputs, unless otherwise specified.) Power Down Mode is defined as RST = LO with all clocks and

data lines held static.

7. Valid with the recommended capacitor values on FILT+ as shown in Figure 5. Increasing the

capacitance will also increase the PSRR. NOTE: Care should be taken when selecting capacitor type,

as any leakage current in excess of 1.0 µA will cause degradation in analog performance.

Base-rate Mode

Parameters Symbol Min Typ Max Units

Power Supplies

Power Supply Current- VA=5V

Normal Operation VL=3V IA

ID_L

-

-- TBD

TBD -

-mA

µA

Power Supply Current- VA=5V

Power Down Mode (Note 6) VL=3V IA

ID_L

-

-TBD

TBD -

-µA

µA

Power Supply Current- VA=5V

Normal Operation VL=5V IA

ID_L

-

-25

TBD -

-mA

µA

Power Supply Current- VA=5V

Power Down Mode (Note 6) VL=5V IA

ID_L

-

-60

TBD -

-µA

µA

Total Power Dissipation- All Supplies=5V

Normal Operation VA=5V, VL=1.8V -

-125

TBD -

-mW

mW

Package Thermal Resistance θJA -TBD-°C/Watt

Power Supply Rejection Ratio (Note 7) 1 kHz

60 Hz PSRR -

-60

40 -

-dB

dB

CS4392

8DS459PP1

DIGITAL CHARACTERISTICS (TA= 25° C)

ABSOLUTE MAXIMUM RATINGS (AGND = 0 V; all voltages with respect to ground.)

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is

not guaranteed at these extremes.

RECOMMENDED OPERATING CONDITIONS (AGND = 0V; all voltages with respect to ground.)

Parameters Symbol Min Typ Max Units

High-Level Input Voltage VIH 70% - - VL

Low-Level Input Voltage VIL - 20% VL

Input Leakage Current Iin --±10µA

Input Capacitance - 8 - pF

Maximum MUTEC Drive Current - 3 - mA

Parameters Symbol Min Max Units

DC Power Supply VA

VL -0.3

-0.3 6.0

VA V

V

Input Current, Any Pin Except Supplies Iin - ±10 mA

Digital Input Voltage VIND -0.3 VL+0.4 V

Ambient Operating Temperature (power applied) TA-55 125 °C

Storage Temperature Tstg -65 150 °C

Parameters Symbol Min Typ Max Units

DC Power Supply VA

VL 4.75

1.8 5.0

-5.5

VA V

V

CS4392

DS459PP1 9

SWITCHING CHARACTERISTICS - PCM MODES (TA= -10 to 70° C; VL = 5.5 to 1.8 Volts;

Inputs: Logic 0 = 0 V, Logic 1 = VL, CL = 20 pF)

Notes: 8. This serial clock is available only in Control Port Mode when the MCLK Divide bit is enabled.

Parameters Symbol Min Typ Max Units

Input Sample Rate Fs 4 - 200 kHz

LRCK Duty Cycle 45 50 55 %

MCLKDutyCycle 405060%

SCLK Frequency --MCLK/2Hz

SCLK Frequency Note 8 --MCLK/4Hz

SCLK rising to LRCK edge delay tslrd 20 - - ns

SCLK rising to LRCK edge setup time tslrs 20 - - ns

SDATA valid to SCLK rising setup time tsdlrs 20 - - ns

SCLK rising to SDATA hold time tsdh 20 - - ns

slrs

t

slrd

t

sdlrs

t

sdh

t

SDATA

SCLK

LRCK

Figure 1. Serial Mode Input Timing

CS4392

10 DS459PP1

SWITCHING CHARACTERISTICS - DSD (TA= -10 to 70° C; Logic 0 = AGND = DGND;

Logic 1 = VL = 5.5 to 1.8 Volts; CL=20pF)

Parameter Symbol Min Typ Max Unit

MCLKDutyCycle 405060%

DSD_SCLK Pulse Width Low tsclkl TBD - - ns

DSD_SCLK Pulse Width High tsclkh TBD - - ns

DSD_SCLK Period tsclkw TBD --ns

DSD_L or DSD_R valid to DSD_SCLK rising setup time tsdlrs TBD - - ns

DSD_SCLK rising to DSD_L or DSD_R hold time tsdh TBD - - ns

sclkh

t

sclkl

t

DSD_L, DSD_R

DSD_SCLK

sdlrs

tsdh

t

Figure 2. Direct Stream Digital - Serial Audio Input Timing

CS4392

DS459PP1 11

SWITCHING CHARACTERISTICS - CONTROL PORT - TWO-WIRE MODE

(TA= 25° C; VL = 5.5 to 1.8 Volts; Inputs: logic 0 = AGND, logic 1 = VL, CL= 30 pF)

Notes: 9. The Two-Wire mode is compatible with the I2C protocol.

10. Data must be held for sufficient time to bridge the 300 ns transition time of SCL.

Parameter Symbol Min Max Unit

Two-Wire Mode

SCL Clock Frequency fscl -100KHz

RST Rising Edge to Start tirs 500 - ns

Bus Free Time Between Transmissions tbuf 4.7 - µs

Start Condition Hold Time (prior to first clock pulse) thdst 4.0 - µs

Clock Low time tlow 4.7 - µs

Clock High Time thigh 4.0 - µs

Setup Time for Repeated Start Condition tsust 4.7 - µs

SDA Hold Time from SCL Falling (Note 10) thdd 0-µs

SDA Setup time to SCL Rising tsud 250 - ns

Rise Time of Both SDA and SCL Lines tr-1µs

Fall Time of Both SDA and SCL Lines tf-300ns

Setup Time for Stop Condition tsusp 4.7 - µs

t

buf thdst

t

hdst

t

low

t

r

t

f

t

hdd

thigh

t

sud

t

sust

t

susp

Stop Start

Start

Stop

Repeated

SDA

SCL

t

irs

RST

Figure 3. Two-Wire Mode Control Port Timing

CS4392

12 DS459PP1

SWITCHING CHARACTERISTICS - CONTROL PORT - SPI MODE

(TA= 25° C; VL = 5.5 to 1.8 Volts; Inputs: logic 0 = AGND, logic 1 = VL, CL= 30 pF)

Notes: 11. tspi only needed before first falling edge of CS after RST rising edge. tspi = 0 at all other times.

12. Data must be held for sufficient time to bridge the transition time of CCLK.

13. For FSCK < 1 MHz

Parameter Symbol Min Max Unit

SPI Mode

CCLK Clock Frequency fsclk -6MHz

RST Rising Edge to CS Falling tsrs 500 - ns

CCLK Edge to CS Falling (Note 11) tspi 500 - ns

CS High Time Between Transmissions tcsh 1.0 - µs

CS Falling to CCLK Edge tcss 20 - ns

CCLK Low Time tscl 66 - ns

CCLK High Time tsch 66 - ns

CDIN to CCLK Rising Setup Time tdsu 40 - ns

CCLK Rising to DATA Hold Time (Note 12) tdh 15 - ns

Rise Time of CCLK and CDIN (Note 13) tr2 -100ns

Fall Time of CCLK and CDIN (Note 13) tf2 -100ns

t

r2 tf2

t

dsu

t

dh

t

sch

tscl

CS

CCLK

CDIN

tcss t

csh

tspi

tsrs

RST

Figure 4. SPI Control Port Timing

CS4392

DS459PP1 13

2. TYPICAL CONNECTION DIAGRAMS

SCLK

Audio

Data

Processor

*

External Clock

MCLK

AGND

AOUTB+

CS4392

SDATA

VA

AOUTB-

+5V Analog

Mode

Select

M1 (SDA/ CDIN)

M0 (AD0/CS)

AOUTA-

AOUTA+

Analog

Conditioning

&

Mute

Analog

Conditioning

&

Mute

17

19

18

14

15

16

1

3

4

5

8

9

10

M2 (SCL/CCLK)

LRCK

1.0

µ

f

+

RST

6

M3

7

12

1.0 µf

0.1 µf 1.0 µf

11

FILT+

0.1 µf

+

+

CMOUT

BMUTEC

13

AMUTEC

20

(Control Port)

*

2

VL

Logic Power

+5V to 1.8V

0.1 µf

Figure 5. Typical Connection Diagram - PCM Mode

* A high logic level for all digital inputs should not exceed VL.

CS4392

14 DS459PP1

DSD_B

Audio

Data

Processor

*

External Clock

MCLK

AGND

AOUTB+

CS4392

DSD_A

VA

AOUTB-

+5V Analog

Mode

Select

M1 (SDA/ CDIN)

M0 (AD0/CS)

AOUTA-

AOUTA+

VL

Analog

Conditioning

&

Mute

Analog

Conditioning

&

Mute

17

19

18

14

15

16

1

2

3

4

7

8

9

10

M2 (SCL/CCLK)

DSD_CLK

1.0

µ

f

+

RST

612

1.0 µf

0.1 µf 1.0 µf

11

FILT+

0.1 µf

+

+

CMOUT

BMUTEC

13

AMUTEC

20

(Control Port)

5DSD_MODE

Logic Power

+5V to 1.8V

0.1 µf

Figure 6. Typical Connection Diagram - DSD Mode

* A high logic level for all digital inputs should not exceed VL.

CS4392

DS459PP1 15

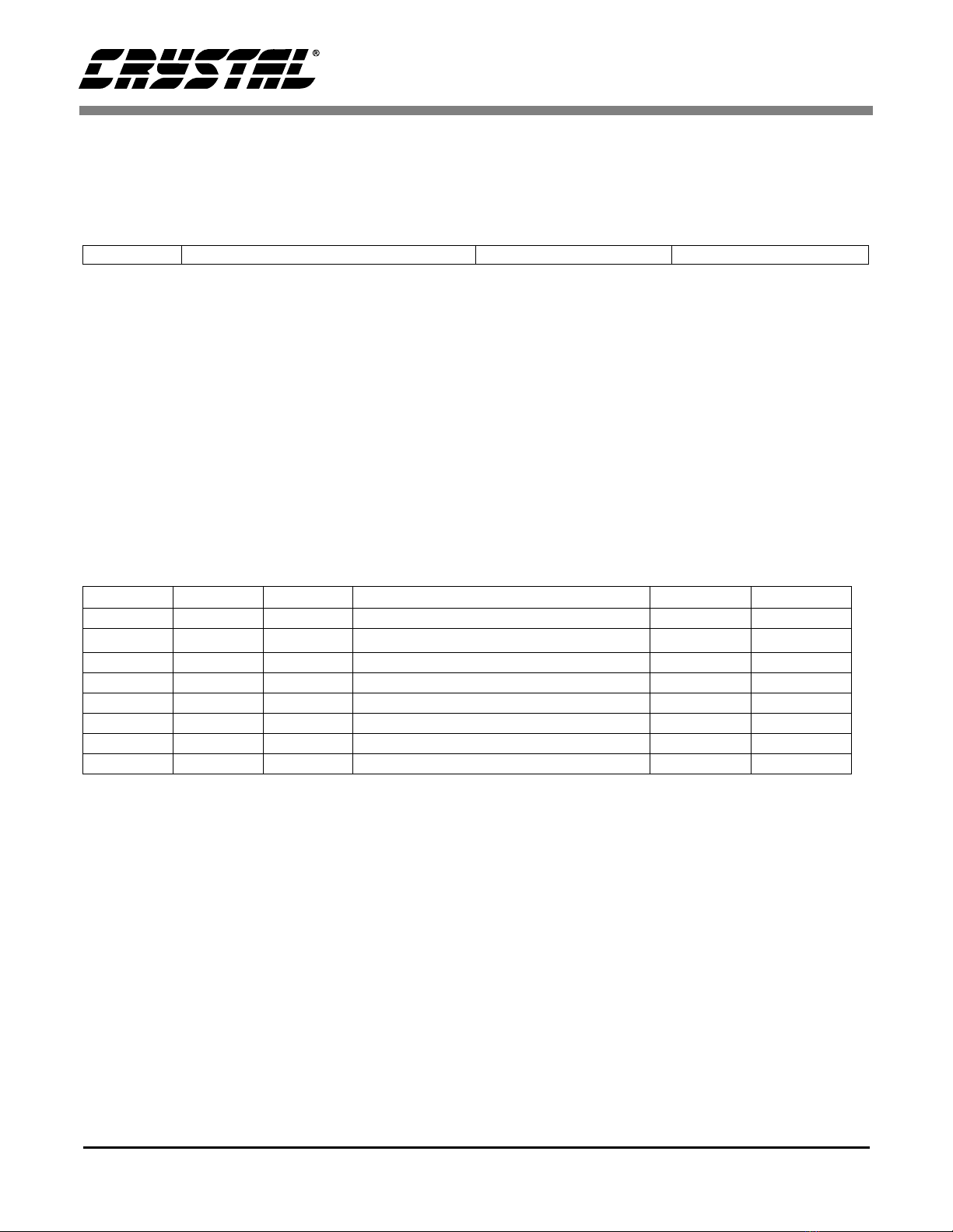

3. REGISTER QUICK REFERENCE

This table shows the register names and their associated default values.

Addr Function 7 6 5 4 3 2 1 0

01h Mode Control 1 AMUTE DIF2 DIF1 DIF0 DEM1 DEM0 FM1 FM0

1000 0 0 00

02h Volume and

MIxing Control A = B Soft Zero

Cross ATAPI4 ATAPI3 ATAPI2 ATAPI1 ATAPI0

0100 1 0 01

03h Channel A Vol-

ume Control MUTE VOL6 VOL5 VOL4 VOL3 VOL2 VOL1 VOL0

0000 0 0 00

04h Channel B Vol-

ume Control MUTE VOL6 VOL5 VOL4 VOL3 VOL2 VOL1 VOL0

0000 0 0 00

05h Mode Control 2 INVERT_A INVERT_B CPEN PDN MUTEC A = B FREEZE MCLK

Divide Reserved

0001 0 0 00

06h Mode Control 3 Reserved Reserved Reserved Filt_rolloff rst_rmp_up rst_rmp_dwn Reserved Reserved

0000 0 0 00

07h Chip ID PART3 PART2 PART1 PART0 REV3 REV2 REV1 REV0

1000 - - --

CS4392

16 DS459PP1

4. REGISTER DESCRIPTION

** All registers are read/write in Two-Wire mode and write only in SPI mode, unless otherwise noted**

4.1 Mode Control 1 - Address 01h

4.1.1 Auto-Mute (Bit 7)

Function:

The Digital-to-Analog converter output will mute following the reception of 8192 consecutive audio

samples of static 0 or -1. A single sample of non-static data will release the mute. Detection and

muting is done independently for each channel. (However, Auto-Mute detection and muting can be-

come dependent on either channel if the Mute A = B function is enabled.) The common mode on the

output will be retained and the Mute Control pin for that channel will go active during the mute period.

The muting function is effected, similar to volume control changes, by the Soft and Zero Cross bits in

the Volume and Mixing Control register.

4.1.2 Digital Interface Formats (Bits 6:4)

Function:

PCM Mode - The required relationship between the Left/Right clock, serial clock and serial data is

defined by the Digital Interface Format and the options are detailed in Table 1 and Figures 9-14.

76543210

AMUTE DIF2 DIF1 DIF0 DEM1 DEM0 FM1 FM0

DIF2 DIF1 DIFO DESCRIPTION Format Figure

0 0 0 Left Justified, up to 24-bit data (default) 0 9

001 I

2

S, up to 24-bit data 110

0 1 0 Right Justified, 16-bit Data 2 11

0 1 1 Right Justified, 24-bit Data 3 12

1 0 0 Right Justified, 20-bit Data 4 13

1 0 1 Right Justified, 18-bit Data 5 14

110 Reserved

111 Reserved

Table 1. Digital Interface Formats - PCM Modes

CS4392

DS459PP1 17

DSD Mode - The relationship between the oversampling ratio of the DSD audio data and the required

Master clock to DSD data rate is defined by the Digital interface Format pins. Note that the Functional

Mode registers must be set to DSD Mode. See Table 2 for register options.

4.1.3 De-Emphasis Control (Bits 3:2)

Function:

Implementation of the standard 15 µs/50 µs digital de-emphasis filter response, Figure 7, requires re-

configuration of the digital filter to maintain the proper filter response for 32, 44.1 or 48 kHz sample

rates. NOTE: De-emphasis is available only in Single-Speed Mode. See Table 3 below.

4.1.4 Functional Mode (Bits 1:0)

Function:

Selects the required range of input sample rates or DSD Mode. See Table 4

DIF2 DIF1 DIFO DESCRIPTION

0 0 0 64x oversampled DSD data with a 4x MCLK to DSD data rate (default)

0 0 1 64x oversampled DSD data with a 6x MCLK to DSD data rate

0 1 0 64x oversampled DSD data with a 8x MCLK to DSD data rate

0 1 1 64x oversampled DSD data with a 12x MCLK to DSD data rate

1 0 0 128x oversampled DSD data with a 2x MCLK to DSD data rate

1 0 1 128x oversampled DSD data with a 3x MCLK to DSD data rate

1 1 0 128x oversampled DSD data with a 4x MCLK to DSD data rate

1 1 1 128x oversampled DSD data with a 6x MCLK to DSD data rate

Table 2. Digital Interface Formats - DSD Mode

DEM1 DEMO DESCRIPTION

0 0 Disabled (default)

0 1 44.1 kHz de-emphasis

1 0 48 kHz de-emphasis

1 1 32 kHz de-emphasis

Table 3. De-Emphasis Mode Selection

Gain

dB

-10dB

0dB

Frequency

T2 = 15 µs

T1=50 µs

F1 F2

3.183 kHz 10.61 kHz

Figure 7. De-Emphasis Curve

FM1 FM0 MODE

0 0 Single-Speed Mode: 4 to 50 kHz sample rates (default)

0 1 Double-Speed Mode: 50 to 100 kHz sample rates

1 0 Quad-Speed Mode: 100 to 200 kHz sample rates

1 1 Direct Stream Digital Mode

Table 4. Functional Mode Selection

CS4392

18 DS459PP1

4.2 Volume and Mixing Control (Address 02h)

4.2.1 Channel A Volume = Channel B Volume (Bit 7)

Function:

The AOUTA and AOUTB volume levels are independently controlled by the A and the B Channel Vol-

ume Control Bytes when this function is disabled. The volume on both AOUTA and AOUTB are de-

termined by the A Channel Volume Control Byte and the B Channel Byte is ignored when this function

is enabled.

4.2.2 Soft Ramp or Zero Cross Enable (Bits 6:5)

Function:

Soft Ramp Enable

Soft Ramp allows level changes, both muting and attenuation, to be implemented by incrementally

ramping, in 1/8 dB steps, from the current level to the new level at a rate of 1dB per 8 left/right clock

periods.

Zero Cross Enable

Zero Cross Enable dictates that signal level changes, either by attenuation changes or muting, will

occur on a signal zero crossing to minimize audible artifacts. The requested level change will occur

after a timeout period between 512 and 1024 sample periods (10.7 ms to 21.3 ms at 48 kHz sample

rate) if the signal does not encounter a zero crossing. The zero cross function is independently mon-

itored and implemented for each channel.

Soft Ramp and Zero Cross Enable

Soft Ramp and Zero Cross Enable dictates that signal level changes, either by attenuation changes

or muting, will occur in 1/8 dB steps and be implemented on a signal zero crossing. The 1/8 dB level

change will occur after a timeout period between 512 and 1024 sample periods (10.7 ms to 21.3 ms

at 48 kHz sample rate) if the signal does not encounter a zero crossing. The zero cross function is

independently monitored and implemented for each channel. See Table 5

4.2.3 ATAPI Channel Mixing and Muting (Bits 4:0)

Function:

The CS4392 implements the channel mixing functions of the ATAPI CD-ROM specification. See

Table 6 on page 19

76543210

A = B Soft Zero Cross ATAPI4 ATAPI3 ATAPI2 ATAPI1 ATAPI0

SOFT ZERO Mode

0 0 Changes to affect immediately

0 1 Zero Cross enabled

1 0 Soft Ramp enabled (default)

1 1 Soft Ramp and Zero Cross enabled

Table 5. Soft Cross or Zero Cross Mode Selection

CS4392

DS459PP1 19

ATAPI4 ATAPI3 ATAPI2 ATAPI1 ATAPI0 AOUTA AOUTB

00000 MUTE MUTE

00001 MUTE bR

00010 MUTE bL

00011 MUTE b[(L+R)/2]

00100 aR MUTE

00101 aR bR

00110 aR bL

00111 aR b[(L+R)/2]

01000 aL MUTE

01001 aL bR

01010 aL bL

01011 aL b[(L+R)/2]

01100 a[(L+R)/2] MUTE

01101 a[(L+R)/2] bR

0 1 1 1 0 a[(L+R)/2] bL

0 1 1 1 1 a[(L+R)/2] b[(L+R)/2]

10000 MUTE MUTE

10001 MUTE bR

10010 MUTE bL

10011 MUTE [(bL+aR)/2]

10100 aR MUTE

10101 aR bR

10110 aR bL

10111 aR [(aL+bR)/2]

11000 aL MUTE

11001 aL bR

11010 aL bL

11011 aL [(aL+bR)/2]

11100 [(aL+bR)/2] MUTE

11101 [(aL+bR)/2] bR

11110 [(bL+aR)/2] bL

1 1 1 1 1 [(aL+bR)/2] [(aL+bR)/2]

Table 6. ATAPI Decode

ΣΣ

A Channel

Volume

Control AoutA

AoutB

Left Channel

Audio Data

Right Channel

Audio Data

B Channel

Volume

Control

MUTE

MUTE

Figure 8. ATAPI Block Diagram

CS4392

20 DS459PP1

4.3 Channel A Volume Control - Address 03h

See 4.4

Channel B Volume Control - Address 04h

4.4 CHANNEL B VOLUME CONTROL - ADDRESS 04H

4.4.1 Mute (Bit 7)

Function:

The Digital-to-Analog converter output will mute when enabled. The common mode voltage on the

output will be retained. The muting function is effected, similiar to attenuation changes, by the Soft

and Zero Cross bits in the Volume and Mixing Control register. The MUTEC pin for that channel will

go active during the mute period if the Mute function is enabled. Both the AMUTEC and BMUTEC

will go active if either MUTE register is enabled and the MUTEC A = B bit (register 5) is enabled.

4.4.2 Volume Control (Bits 6:0)

Function:

The digital volume control allows the user to attenuate the signal in 1 dB increments from 0 to -127 dB.

Volume settings are decoded as shown in Table 7. The volume changes are implemented as dictated by

the Soft and Zero Cross bits in the Volume and Mixing Control register (see section 4.2.2).

4.5 Mode Control 2 - Address 05h

4.5.1 Invert Signal Polarity (Bits 7:6)

Function:

When set to 1, this bit inverts the signal polarity for the appropriate channel. This is useful if a board

layout error has occurred, or an other situations where a 180 degree phase shift is desirable. Default

is 0.

76543210

MUTE VOL6 VOL5 VOL4 VOL3 VOL2 VOL1 VOL0

Binary Code Decimal Value Volume Setting

0000000 0 0 dB

0010100 20 -20 dB

0101000 40 -40 dB

0111100 60 -60 dB

1011010 90 -90 dB

Table 7. Digital Volume Control Example Settings

76543210

INVERT_A INVERT_B CPEN PDN MUTEC A = B FREEZE MCLK Divide Reserved

Table of contents