Dini Group DN9002K10PCI User manual

LOGIC Emulation Source

User Guide

DN9002K10PCI

Table of Contents

CHAPTER 1: INTRODUCTION................................................................................................................................................1

1MANUAL CONTENTS........................................................................................................................................................1

INTRODUCTION ............................................................................................................................................................................1

QUICK START GUIDE...................................................................................................................................................................1

CONTROLLER SOFTWARE............................................................................................................................................................2

HARDWARE..................................................................................................................................................................................2

THE REFERENCE DESIGN.............................................................................................................................................................2

ORDERING INFORMATION............................................................................................................................................................2

2CONVENTIONS...................................................................................................................................................................2

2.1TYPOGRAPHICAL .............................................................................................................................................................2

2.2MANUAL CONTENT .........................................................................................................................................................2

2.2.1File names...............................................................................................................................................................2

2.2.2Physical Dimensions...............................................................................................................................................2

2.2.3Part Pin Names.......................................................................................................................................................3

2.2.4Schematic Clippings................................................................................................................................................3

2.3TERMINOLOGY.................................................................................................................................................................3

3RESOURCES ........................................................................................................................................................................4

3.1USER CD..........................................................................................................................................................................4

3.2DINIGROUP.COM..............................................................................................................................................................5

3.3ERRATA AND CUSTOMER NOTIFICATIONS ......................................................................................................................5

3.4SCHEMATICS AND NETLIST .............................................................................................................................................5

3.4.1Netlist ......................................................................................................................................................................5

3.4.2Net name conventions .............................................................................................................................................5

3.5DATASHEET LIBRARY......................................................................................................................................................6

3.6XILINX .............................................................................................................................................................................6

3.7DINI GROUP REFERENCE DESIGNS..................................................................................................................................6

3.8BOARD MODELS ..............................................................................................................................................................6

4EMAIL AND PHONE SUPPORT ......................................................................................................................................6

CHAPTER 2: QUICK START GUIDE......................................................................................................................................7

1PROVIDED MATERIALS..................................................................................................................................................7

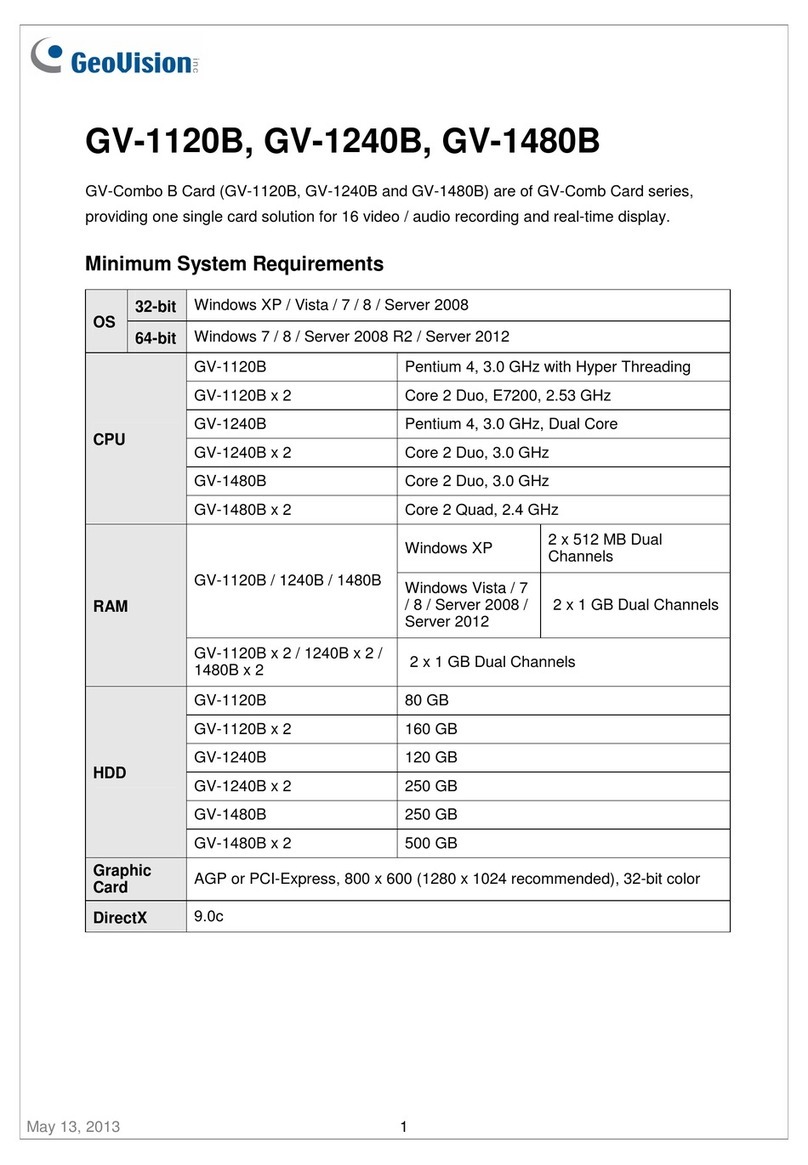

1.1SYSTEM REQUIREMENTS .................................................................................................................................................7

2WARNINGS ..........................................................................................................................................................................8

2.1ESD .................................................................................................................................................................................8

2.2OTHER..............................................................................................................................................................................8

2.3OTHER,SPECULATIVE......................................................................................................................................................8

3PRE-POWER ON INSTRUCTIONS..................................................................................................................................9

3.1INSTALL MEMORY.........................................................................................................................................................10

3.2PREPARE CONFIGURATION FILES...................................................................................................................................10

3.3INSTALL DN9002K10PCI IN COMPUTER ......................................................................................................................11

3.4CABLES..........................................................................................................................................................................11

3.4.1Connect RS232 Cable...........................................................................................................................................11

3.4.2Connect USB Cable ..............................................................................................................................................12

3.4.3Connect Power cable............................................................................................................................................12

4POWER ON.........................................................................................................................................................................12

4.1VIEW CONFIGURATION FEEDBACK OVER RS232 ..........................................................................................................12

4.2CHECK LED STATUS LIGHTS .........................................................................................................................................14

5RUN USB CONTROLLER................................................................................................................................................15

DN9002K10PCI User Guide www.dinigroup.com

INTRODUCTION

5.1DRIVER INSTALLATION .................................................................................................................................................15

5.2OPERATING THE USB CONTROLLER PROGRAM............................................................................................................15

5.2.1Configure an FPGA..............................................................................................................................................16

5.2.2Set Clock Frequencies...........................................................................................................................................17

5.2.3Run Hardware Test (DDR2).................................................................................................................................17

5.3GETTING DATA TO AND FROM THE FPGA.....................................................................................................................18

6COMMUNICATING OVER THE SERIAL PORT .......................................................................................................18

7RUN AETEST_WDM.........................................................................................................................................................19

7.1.1Use AETest............................................................................................................................................................19

8SCAN THE JTAG CHAIN ................................................................................................................................................22

8.1MOVING ON...................................................................................................................................................................23

CHAPTER 3: CONTROLLER SOFTWARE.........................................................................................................................25

1USB CONTROLLER..........................................................................................................................................................26

1.1MAIN WINDOW..............................................................................................................................................................26

1.1.1Refresh Button.......................................................................................................................................................27

1.1.2Disable/Enable USB .............................................................................................................................................28

1.1.3Log Window ..........................................................................................................................................................28

1.1.4Board Graphic ......................................................................................................................................................28

1.2MENU OPTIONS..............................................................................................................................................................29

1.2.1File Menu ..............................................................................................................................................................29

1.2.2Edit Menu..............................................................................................................................................................30

1.2.3FPGA Configuration Menu...................................................................................................................................30

1.2.4FPGA Reference Design.......................................................................................................................................31

1.2.5Main Bus ...............................................................................................................................................................31

1.2.6Settings/Info Menu ................................................................................................................................................32

1.2.7Production Tests....................................................................................................................................................33

1.2.8Service Menu.........................................................................................................................................................33

1.3INI FILE .........................................................................................................................................................................33

2AETEST USB ......................................................................................................................................................................34

2.1COMPILING AETEST_USB .............................................................................................................................................34

2.2COMPILING THE DRIVER................................................................................................................................................34

3PCI AETEST APPLICATION..........................................................................................................................................34

3.1FUNCTIONALITY ............................................................................................................................................................35

3.2RUNNING AETEST........................................................................................................................................................35

3.3COMPILING AETEST (PCI)...........................................................................................................................................37

3.3.1Compiling AETest for DOS...................................................................................................................................37

3.3.2Compiling AETest for Windows XP......................................................................................................................38

4ROLLING YOUR OWN SOFTWARE............................................................................................................................38

4.1USB ...............................................................................................................................................................................38

4.2PCI.................................................................................................................................................................................38

5UPDATING THE FIRMWARE........................................................................................................................................38

5.1OBTAINING THE UPDATES..............................................................................................................................................39

5.2UPDATING THE SPARTAN (PROM) FIRMWARE.............................................................................................................39

5.2.1Using JTAG cable (Xinlinx products)...................................................................................................................39

5.2.2Using USBController............................................................................................................................................42

5.2.3Using AEtest_USB ................................................................................................................................................42

5.3UPDATING EEPROM FIRMWARE (NOT RECOMMEND)..................................................................................................43

5.3.1Using USBController............................................................................................................................................44

5.3.2Using AETest_USB...............................................................................................................................................44

5.4UPDATING THE MCU (FLASH)FIRMWARE....................................................................................................................45

5.4.1Using USBController............................................................................................................................................45

5.4.2Using AETest_USB...............................................................................................................................................45

CHAPTER 4: HARDWARE......................................................................................................................................................47

1GENERAL OVERVIEW ...................................................................................................................................................47

INTRODUCTION

1.1MARKETING CRAP.........................................................................................................................................................48

1.1.1Features.................................................................................................................................................................48

1.1.2Description............................................................................................................................................................49

2VIRTEX 5 ............................................................................................................................................................................50

3CONFIGURATION SECTION.........................................................................................................................................50

3.1CONFIGURATION SECTION FEEDBACK..........................................................................................................................51

3.2FPGA CONFIGURATION ................................................................................................................................................52

3.3USB AND PCI INTERFACES ...........................................................................................................................................53

3.4COMPACTFLASH INTERFACE.........................................................................................................................................53

3.4.1Main.txt .................................................................................................................................................................54

3.4.2Hardware ..............................................................................................................................................................57

3.5CONFIGURATION REGISTERS.........................................................................................................................................57

3.5.1Undocumented controls ........................................................................................................................................58

3.6FIRMWARE.....................................................................................................................................................................58

4CLOCK NETWORK..........................................................................................................................................................59

4.1.1GC Pins.................................................................................................................................................................59

4.2GLOBAL CLOCKS...........................................................................................................................................................59

4.3G0, G1, G2 CLOCKS ......................................................................................................................................................60

4.3.1Clock Synthesizers.................................................................................................................................................61

4.3.2Possible Outputs....................................................................................................................................................61

4.3.3Duty Cycle.............................................................................................................................................................62

4.3.4Jitter ......................................................................................................................................................................62

4.4EXT CLOCKS..................................................................................................................................................................62

4.4.1EXT0......................................................................................................................................................................62

4.4.2EXT1......................................................................................................................................................................63

4.4.3Daughtercard zero-delay mode ............................................................................................................................63

4.4.4SMA input..............................................................................................................................................................63

4.5PCI CLOCK ....................................................................................................................................................................64

4.6NON-GLOBAL CLOCKS..................................................................................................................................................64

4.6.1Clock TP................................................................................................................................................................64

4.6.2Ethernet Clock.......................................................................................................................................................65

4.6.3DDR2 Clocks.........................................................................................................................................................65

4.6.4SMA Clock A .........................................................................................................................................................66

5TEST POINTS.....................................................................................................................................................................66

5.1POWER THRU-HOLE.......................................................................................................................................................67

5.2POWER TP......................................................................................................................................................................68

5.3DIMM POWER...............................................................................................................................................................68

5.4“GC” TEST POINTS ........................................................................................................................................................69

5.5CLOCK TEST POINTS......................................................................................................................................................70

5.6DIMM SIGNALS.............................................................................................................................................................71

6USB INTERFACE ..............................................................................................................................................................71

6.1CONNECTING TO THE DN9002K10PCI.........................................................................................................................72

6.1.1Windows XP ..........................................................................................................................................................72

6.1.2Windows Vista.......................................................................................................................................................72

6.1.3Linux......................................................................................................................................................................72

6.1.4Communication.....................................................................................................................................................72

6.2VENDOR REQUESTS.......................................................................................................................................................72

6.2.1VR_CLEAR_FPGA ...............................................................................................................................................73

6.2.2VR_SETUP_CONFIG...........................................................................................................................................74

6.2.3VR_END_CONFIG...............................................................................................................................................74

6.2.4VR_SET_EP6TC (Read buffer size)......................................................................................................................74

6.2.5VR_MEM_MAPPED (Configuration Registers)..................................................................................................74

6.2.6Other Vendor Requests.........................................................................................................................................74

6.3MAIN BUS ACCESSES.....................................................................................................................................................74

6.3.1Important Note About Endpoints..........................................................................................................................75

6.3.2Performance..........................................................................................................................................................75

6.4FPGA CONFIGURATION ................................................................................................................................................76

6.4.1Readback...............................................................................................................................................................76

6.5USB HARDWARE...........................................................................................................................................................77

6.5.1Cypress CY7C68013A...........................................................................................................................................77

INTRODUCTION

6.5.2Activity LED..........................................................................................................................................................78

6.5.3Configuration FPGA.............................................................................................................................................78

6.5.4Power ....................................................................................................................................................................78

6.6TROUBLESHOOTING.......................................................................................................................................................78

6.6.1USB Controller Freezes........................................................................................................................................78

6.6.2Main Bus always returns 0x______ (Error Codes)..............................................................................................78

7PCI INTERFACE ...............................................................................................................................................................79

7.1FPGA INTERFACE..........................................................................................................................................................80

7.1.1FPGA-initiated DMA............................................................................................................................................82

7.2HOST INTERFACE,SOFTWARE.......................................................................................................................................83

7.2.1Driver ....................................................................................................................................................................83

7.2.2Board Settings.......................................................................................................................................................83

7.2.3Main Bus ...............................................................................................................................................................84

7.2.4FPGA Configuration.............................................................................................................................................85

7.2.5Direct PCI to FPGA, DMA...................................................................................................................................86

7.2.6Direct PCI to FPGA A, Target access..................................................................................................................86

7.2.7Performance..........................................................................................................................................................86

7.2.864-bit addressing...................................................................................................................................................87

7.3HOST INTERFACE,ELECTRICAL ....................................................................................................................................87

7.3.1Power ....................................................................................................................................................................87

7.3.2PCI-X.....................................................................................................................................................................87

7.3.3PCI Frequency......................................................................................................................................................88

7.4HOST INTERFACE,MECHANICAL ..................................................................................................................................88

7.5HARDWARE DESIGN NOTES ..........................................................................................................................................88

7.6TROUBLESHOOTING.......................................................................................................................................................89

8UNUSABLE PINS...............................................................................................................................................................89

8.1.1Configuration........................................................................................................................................................89

9SYSTEM MONITOR/ADC ...............................................................................................................................................90

10RESET..............................................................................................................................................................................90

10.1POWER RESET............................................................................................................................................................90

10.2USER RESET...............................................................................................................................................................91

11JTAG ................................................................................................................................................................................92

11.1FPGA JTAG..............................................................................................................................................................92

11.1.1Compatible Configuration Devices ......................................................................................................................93

11.1.2Identify...................................................................................................................................................................93

11.1.3ChipScope .............................................................................................................................................................93

11.2FIRMWARE UPDATE HEADER....................................................................................................................................93

11.3TROUBLESHOOTING...................................................................................................................................................93

12RS232 INTERFACE.......................................................................................................................................................93

12.1.1Configuration RS232.............................................................................................................................................94

13TEMPERATURE SENSORS. .......................................................................................................................................95

14ENCRYPTION BATTERY ...........................................................................................................................................95

15LED INTERFACE..........................................................................................................................................................96

15.1CONFIGURATION SECTION LEDS..............................................................................................................................96

15.2USER LEDS................................................................................................................................................................97

15.3ETHERNET LEDS.......................................................................................................................................................97

15.4POWER LEDS.............................................................................................................................................................98

15.5UNUSED LEDS...........................................................................................................................................................99

16DDR2 ................................................................................................................................................................................99

16.1POWER .......................................................................................................................................................................99

16.1.1Interface Voltages .................................................................................................................................................99

16.1.2Changing the DIMM voltage..............................................................................................................................100

16.2CLOCKING................................................................................................................................................................100

16.3SIGNALING...............................................................................................................................................................102

16.3.1Standards.............................................................................................................................................................102

INTRODUCTION

16.3.2Serial Interface....................................................................................................................................................102

16.3.3Timing..................................................................................................................................................................103

16.4COMPATIBLE MODULES ..........................................................................................................................................103

16.5TEST POINTS ............................................................................................................................................................104

17FPGA INTERCONNECT............................................................................................................................................105

18MAIN BUS.....................................................................................................................................................................107

18.1MB SIGNALS............................................................................................................................................................107

18.1.1Disambiguation...................................................................................................................................................107

18.1.2Electrical.............................................................................................................................................................108

18.1.3Timing..................................................................................................................................................................108

18.2ERROR CODES..........................................................................................................................................................108

18.3FPGA INTERFACE....................................................................................................................................................109

18.3.1Conventional Memory map.................................................................................................................................110

19ETHERNET...................................................................................................................................................................111

19.1MII...........................................................................................................................................................................111

19.1.1Electrical.............................................................................................................................................................111

19.1.2Timing..................................................................................................................................................................111

19.2JTAG.......................................................................................................................................................................114

20EPROM..........................................................................................................................................................................115

21MICTOR CONNECTORS...........................................................................................................................................116

21.1FPGA BMICTOR.....................................................................................................................................................116

21.2MAINBUS MICTOR ..................................................................................................................................................117

22POWER..........................................................................................................................................................................118

22.15.0V.........................................................................................................................................................................119

22.23.3V.........................................................................................................................................................................119

22.32.5V.........................................................................................................................................................................119

22.4GROUND ..................................................................................................................................................................119

22.5VOLTAGE REGULATION ..........................................................................................................................................120

22.6POWER CONNECTIONS.............................................................................................................................................120

22.7POWER MONITORS ..................................................................................................................................................121

22.8HEAT........................................................................................................................................................................122

22.8.1Fans.....................................................................................................................................................................122

22.8.2Removing Heatsinks............................................................................................................................................122

22.8.3Fan Tachometers.................................................................................................................................................122

23CONNECTORS.............................................................................................................................................................123

23.1FPGA USER INTERFACE CONNECTORS...................................................................................................................123

23.1.1Comments............................................................................................................................................................124

23.2NON-FPGA USER INTERFACE CONNECTORS..........................................................................................................124

23.2.1Comments............................................................................................................................................................125

23.3NOT-FOR-USE CONNECTORS ..................................................................................................................................125

23.3.1Comments............................................................................................................................................................125

24MECHANICAL.............................................................................................................................................................126

25DAUGHTERCARD HEADERS..................................................................................................................................127

25.1DAUGHTER CARD PHYSICAL...................................................................................................................................128

25.1.1Daughter Card Locations and Mounting ...........................................................................................................128

25.1.2Type 2 Short (400pin Short)................................................................................................................................130

25.1.3Insertion and removal.........................................................................................................................................131

25.2DAUGHTER CARD ELECTRICAL...............................................................................................................................133

25.2.1Pin assignments...................................................................................................................................................133

25.2.2CC, VREF, DCI...................................................................................................................................................134

25.2.3Global clocks.......................................................................................................................................................134

25.2.4Timing and Clocking...........................................................................................................................................135

25.2.5Power and Reset..................................................................................................................................................136

25.2.6VCCO Voltage.....................................................................................................................................................136

25.2.7VCCO bias generation........................................................................................................................................136

25.3ROLLING YOUR OWN DAUGHTERCARD ...................................................................................................................137

INTRODUCTION

26TROUBLESHOOTING ...............................................................................................................................................137

26.1THE BOARD IS DEAD ................................................................................................................................................137

26.2THE FPGAS WON’T PROGRAM ................................................................................................................................138

26.3MY DESIGN DOESN’T DO ANYTHING .......................................................................................................................138

26.4THE DCMS WON’T LOCK.........................................................................................................................................139

26.5THE BOARD RESETS,RIGHT AFTER IDIDN’THIT THE RESET BUTTON.....................................................................139

26.6THE ______ SIGNAL ON MY BOARD IS GOING CRAZY ON MY OSCILLOSCOPE.........................................................139

CHAPTER 5: THE REFERENCE DESIGN.........................................................................................................................141

1WHAT THE REFERENCE DESIGN DOES ................................................................................................................141

1.1EXAMPLE USAGE OF ALL INTERFACES ........................................................................................................................141

1.2REFERENCE DESIGN TYPES .........................................................................................................................................142

1.3USING THE REFERENCE DESIGN...................................................................................................................................142

2REFERENCE DESIGN MEMORY MAP.....................................................................................................................143

3INTERCONNECT (DC)...................................................................................................................................................145

3.1USING THE DESIGN......................................................................................................................................................145

3.2RUNNING THE TEST .....................................................................................................................................................146

4DDR2 INTERFACE..........................................................................................................................................................146

4.1PROVIDED FILES ..........................................................................................................................................................146

4.2USING THE DESIGN......................................................................................................................................................146

4.3RUNNING THE TEST .....................................................................................................................................................146

5CLOCK COUNTERS.......................................................................................................................................................147

6LEDS...................................................................................................................................................................................147

7SIMULATING THE REFERENCE DESIGN...............................................................................................................147

8COMPILING THE REFERENCE DESIGN.................................................................................................................147

8.1.1The Xilinx Embedded Development Kit (EDK)..................................................................................................148

8.1.2Xilinx XST............................................................................................................................................................148

8.1.3Xilinx ISE.............................................................................................................................................................148

8.1.4The Build Utility: Make.bat ................................................................................................................................148

8.2BITGEN OPTIONS .........................................................................................................................................................148

8.3VHDL..........................................................................................................................................................................148

9LVDS REFERENCE DESIGN........................................................................................................................................149

9.1PROVIDED FILES ..........................................................................................................................................................149

9.2USING THE DESIGN......................................................................................................................................................149

9.3RUNNING THE TEST .....................................................................................................................................................149

10PCI INTERFACE REFERENCE DESIGN...............................................................................................................149

10.1PROVIDED FILES......................................................................................................................................................150

10.2USING THE DESIGN..................................................................................................................................................150

10.3RUNNING THE TEST.................................................................................................................................................150

CHAPTER 6: ORDERING INFORMATION.......................................................................................................................151

1SECTION TITLE..............................................................................................................................................................151

2FPGA OPTIONS...............................................................................................................................................................151

2.1FPGA AAND B: ..........................................................................................................................................................151

2.2CES PARTS ..................................................................................................................................................................151

2.2.1Hardware Errata Details....................................................................................................................................151

2.3“SMALL”FPGAS.........................................................................................................................................................152

2.4SPEED GRADES ............................................................................................................................................................154

2.5UPGRADE POLICY........................................................................................................................................................155

3OPTIONAL EQUIPMENT..............................................................................................................................................155

3.1COMPATIBLE DINI GROUP PRODUCTS.........................................................................................................................155

3.1.1Memories.............................................................................................................................................................155

INTRODUCTION

3.1.2Extenders.............................................................................................................................................................156

3.1.3Daughtercards.....................................................................................................................................................156

3.2COMPATIBLE THIRD-PARTY PRODUCTS.......................................................................................................................157

4COMPLIANCE DATA.....................................................................................................................................................158

4.1COMPLIANCE ...............................................................................................................................................................158

4.1.1EMI......................................................................................................................................................................158

4.1.2PCI-SIG...............................................................................................................................................................158

4.2ENVIRONMENTAL ........................................................................................................................................................158

4.2.1Temperature........................................................................................................................................................158

4.3EXPORT CONTROL.......................................................................................................................................................158

4.3.1Lead-Free............................................................................................................................................................158

4.3.2The USA Schedule B number based on the HTS ................................................................................................158

4.3.3Export control classification number ECCN......................................................................................................159

4.4MISSION CRITICAL ......................................................................................................................................................159

Chapter

1

Chapter1:Introduction

Congratulations on your purchase of the DN9002K10PCI logic emulation board. If you are

unfamiliar with Dini Group products, you should read Chapter 2, Quick Start Guide to

familiarize yourself with the user interfaces the DN9002K10PCI provides.

Figure 1 DN9002K10PCI – shown with optional memory modules installed; User LEDs, power fail LEDs, and Gigabit activity LEDs all glowing

inexplicably. Heatsinks negligently left uninstalled.

1Manual Contents

This manual contains the following chapters:

Introduction

Reader’s Guide to this manual; List of available documentation and resources available.

Quick Start Guide

Step-by-step instructions for powering on the DN9002K10PCI, loading and communicating

with a simple, provided FPGA design, and using the board’s common control features.

DN9002K10PCI User Guide www.dinigroup.com 1

INTRODUCTION

Controller Software

A summary of the functionality of the provided software. Implementation details for the remote

USB board control functions and instructions for developing your own USB host software.

Hardware

Detailed description and operating instructions of each individual circuit on the

DN9002K10PCI, a description of each user-accessible interface and user features.

The Reference Design

Detailed description of the provided DN9002K10PCI reference design. Implementation details

of the reference design interaction with DN9002K10PCI hardware features.

Ordering Information

Contains a list of the available options and available optional equipment. Some suggested parts

and equipment available from third party vendors. Compatibility lists.

2Conventions

This document uses the following conventions. An example illustrates each convention.

2.1 Typographical

The following typographical conventions are used in this document:

Convention Meaning or Use Example

Prefix “0x” Indicates hexadecimal notation Read from address

0x00110373, returned

Letter “#”, “N” Signal is active low INT# is active low

RSTn is active low

2.2 Manual Content

2.2.1 File names

Paths to documents included on the User CD are prefixed with “D:\”. This refers to your CD

drive’s root directory when the User CD is inserted in your Windows computer.

Alternately, copy the entire contents of the User CD to your hard drive, and allow D:\ to refer

to this path. Due to limitations of the Xilinx ISE software, we recommend a path without space

characters in it. (Bad places include C:/Documents and Settings/username/Desktop/)

2.2.2 Physical Dimensions

By convention, the board is oriented as shown in the above board photo, with the “top” of the

board being the edge near the DDR2 SODIMMs. The “right” edge is near FPGA B. The “left”

side is the side with the PCI bezel. “Top” side refers to the side of the PWB with FPGAs and

fans; the “back” side is the side with the two daughtercard connectors. The reference origin of

DN9002K10PCI User Guide www.dinigroup.com 2

INTRODUCTION

the board is the center of the lower PCI bezel mounting hole. Physical dimensions are given in

millimeters.

2.2.3 Part Pin Names

References to individual part’s pin are given in the form <X><Y>.<Z>; The <X> is one of: U

for ICs, R for resistors, C for capacitors, P or J for connectors, FB or L for inductors, TP for

test points, MH for mounting structures, FD for fiducials, BT for sockets, DS for displays (light-

emitting diodes), F for fuses, PSU for power supply modules, Q for discreet semiconductors,

RN for resistor networks, G for oscillators, X for sockets, Y for crystals and the PCI bezel.

<Y> is a number uniquely identifying each part from other parts of the same class. <Z> is the

pin or terminal number or name, as defined in the datasheet of the part. Datasheets for all

standard and optional parts used on the DN9002K10PCI are included in the Document library

on the user CD.

2.2.4 Schematic Clippings

Partial schematic drawings are included in this document to aid quick understanding of the

features of the DN9002K10PCI. These clippings have been modified for clarity and brevity, and

may be missing signals, parts, net names and connections. Unmodified Schematics are included

in the User CD as a PDF. Please refer to this document when designing an interface in the FPGA. Use the

PDF search feature to search for nets and parts.

2.3 Terminology

Abbreviations and pronouns are used for some commonly used phrases. The user is assumed to

know the meaning of the following:

Spartan

Spartan refers to the Spartan-3 FPGA device used by the DN9002K10PCI to perform

configuration circuit functions. It is used interchangeably with “configuration circuit”

DCM, DLL, PLL

“Digital Clock Manager” or “Digitally-locked-loop”. This is a clock synthesis module in a

Virtex-5 FPGA. PLL is “Phase-locked-loop”. See Xilinx documentation.

LVDS

“Low-Voltage differential signaling”. A signaling standard with a 1.2V DC, and 300mV AC

level. In this manual and in advertisements, LVDS is often used where “Differential Signal”

should be used instead.

Net, Signal, Plane, rail

A net is an electrically continuous piece of conductor on the PCB before assembly. Signal can

refer to an electrically continuous conductor on the PCB, or to the logical meaning of that net.

Plane is a net for voltage sources. Rail is also used to mean a power net.

GND, ground, grounded

GND is a net on the DN9002K10PCI, to which all voltages are referenced. “Ground” is

DN9002K10PCI User Guide www.dinigroup.com 3

INTRODUCTION

equivalent”. Grounded means “connected to GND”. There is a single ground net on the

DN9002K10PCI

3Resources

The following electronic resources will help you during development with your board.

3.1 User CD

The User CD contains all the electronic documents required for you to operate the

DN9002K10PCI. These include schematics, the user manual, FPGA reference designs, and

datasheets. The directory structure of the CD is as follows

3rdPartySoftware\Acrobat Reader 7.0\ Required to read .pdf documents (Windows)

Config_Section_Code\ The DN9002K10PCI firmware source code.

ConfigFPGA\ These sources are not intended to be used for

MCU\ development.

Datasheets\ A datasheet for every part used on the board.

You will need these to interface successfully

with resources on the DN9002K10PCI.

Documentation\Manual\ Contains this document

FPGA_Reference_Designs\ Contains the source and compiled program-

common\ ming files for the Dini group’s DN9002K10-

DN9002K10PCI\ PCI reference design. Also, board

description

Programming_Files\ files and simulation models.

certify\

PCI_Software_Applications\Aetest\ Source and binaries for the provided PCI-

hosted controller software.

Schematics\Rev_01\ Contains a PDF version of the board

schematic. Search the PDF using control-F.

Also contains an ASCII netlist of the board.

USB_Software_Applications\ Contains source and binaries for the provided

driver\ USB-hosted controller applications.

USB_CMD_Line_AETEST_USB\

USBController\

DN9002K10PCI User Guide www.dinigroup.com 4

INTRODUCTION

3.2 Dinigroup.com

The most recent versions of the following documents are found on the product web page

http://dinigroup.com/index.php?product=DN9002K10PCI

User’s Manual (this document)

Certify Board Description File

Errata

USB Controller executable

3.3 Errata and Customer Notifications

The Errata sheet (available at www.dinigroup.com) lists all cases where the DN9002K10PCI is

found to have failed to meet advertised specifications, or where an error in schematics or

documentation is likely to cause a difficult-to-debug error by the user.

The customer is notified when there is an update to the Errata list after the board is shipped.

Customers are not notified when changes are made to other documents including the reference

design, USB Controller and User Manual. These documents change or a weekly basis or faster.

You may always request a duplicate User CD. We will also be happy to provide the latest

version of documents via email to customers.

3.4 Schematics and Netlist

Unmodified Schematics are included in the User CD as a PDF. Use the PDF search feature to

search for nets and parts.

3.4.1 Netlist

In lieu of providing a machine-readable version of the schematic, the Dini Group provides a

text netlist of the board. This netlist contains all nets on the board that connect to user IO on

any FPGA. When interfacing with any device or connector on the DN9002K10PCI you should

use either the provided ucf, or the netlist to generate the pinout. The netlist is located on the

user CD at

D:\Schematics\Rev_01\DN9002K10PCI_customer_netlist.net

3.4.2 Net name conventions

All “power” nets begin with a +, - symbol, or GND

All clock signals begin with “CLK”

Two sides of a differential signal differ by one character “p” or “n”. This character is near the

end of the net name.

Active low signals end in #. In the provided UCF files, the # is replaced by an “N”.

DN9002K10PCI User Guide www.dinigroup.com 5

INTRODUCTION

DN9002K10PCI User Guide www.dinigroup.com 6

3.5 Datasheet Library

Datasheets for all parts used, or interfaced to, on the DN9002K10PCI are provided on the user

CD. In order to successfully use the DN9002K10PCI, you will have to reference these

datasheets. The interface descriptions given in this user manual typically end with electrical

connectivity.

Especially read the Virtex-5 user guide. The copy provided on the user CD is only recent as of

the DN9002K10PCI product announcement.

3.6 Xilinx

Virtex-5 is a brand-new device, and technical questions about getting the FPGA and ISE

software to behave like you expect should be directed to a Xilinx FAE. Also use

WebCase http://www.xilinx.com/support/clearexpress/websupport.htm

AnswerBrowser http://www.xilinx.com/xlnx/xil_ans_browser.jsp

ISE Manual http://www.xilinx.com/support/sw_manuals/xilinx82/index.htm

Virtex 5 Manual(s) http://www.xilinx.com/xlnx/xweb/xil_publications_display.jsp?

3.7 Dini Group Reference Designs

The source code to the reference designs are on the User CD. Please copy and use any code you

would like. The reference designs themselves are not deliverables, and as such receive limited

support.

3.8 Board Models

Certify board models and other simulation models for the DN9002K10PCI are provided on the

user CD.

D:\FPGA_Reference_Designs\DN9002K10PCI\certify

4Email and Phone Support

Dini Group technical support for products can be reached via email at support@dinigroup.com.

Our phone number is (USA) 858-454-3419. Please do not send .exe files, .vb files, or .zip files

containing other .zip files as attachments, as we will not receive these emails. Please include the

board’s serial number in your email. This will allow us to reference our records regarding your

board.

Before contacting support you should complete the following:

1) Follow the debugging steps in the troubleshooting sections at the end of the hardware

chapter, and in any applicable interface sections.

2) Test the applicable interface(s) using the provided software and .bit files, to help rule out

hardware failures.

Chapter

2

Chapter2:Quick Start Guide

The Dini Group DN9002K10PCI can be used and controlled using many interfaces. In order

to learn the use of the most fundamental interfaces of the board (FPGA Configuration, USB

data movement, etc.) please follow the instructions in this quick start guide. The guide will also

show you how to run the board’s hardware test to verify board functionality. (The board has

already been tested at the factory).

1Provided Materials

Examine the contents of your DN9002K10PCI kit. It should contain:

•DN9002K10PCI board

•CompactFlash card containing the FPGA configuration “.bit” files required to run the

hardware test.

•USB CompactFlash card reader

•RS232 IDC header cable to female DB9

•USB cable, black.

•CD ROM containing:

- Virtex 5 Reference Designs

- User manual PDF

- Board Schematic PDF

- USB program (usbcontroller.exe)

- PCI program (Aetest.exe)

- Source code for USB program, PCI program and DN9002K10PCI firmware

- Board netlist, certify model, and QL5064 simulation model

1.1 System Requirements

To compile Verilog designs for Virtex 5, ISE 9.1 may be required. For LX330 designs, you may

need a Linux machine with a 64-bit processor and 6GB of RAM or greater. (Windows XP limits

memory to 3GB)

To use the provided controller software, you need any Windows XP computer with USB 2.0.

To receive firmware updates to the DN9002K10PCI, you need a JTAG programming cable

from Xilinx. Having this cable is basically mandatory, otherwise you would need to ship the

board back to us to enable features or correct firmware bugs. You probably need a JTAG cable

DN9002K10PCI User Guide www.dinigroup.com 7

QUICK START GUIDE

anyway for using embedded debugging software. We recommend the Xilinx Platform USB

cable over their Parallel IV, because it sucks less.

2Warnings

2.1 ESD

The DN9002K10PCI is sensitive to static electricity, so treat the PCB accordingly. The target

markets for this product are engineers that are familiar with FPGAs and circuit boards.

However, if needed, the following web page has an excellent tutorial on the “Fundamentals of

ESD” for those of you who are new to ESD sensitive products:

http://www.esda.org/esd_fundamentals.html

Figure 2 - Bzzzzzzt!!

There are two large grounded metal rails on the DN9002K10PCI. The user should handle the

board using these rails, as they are much less ESD sensitive than any other point on the board.

The 400-pin connectors are not 5V tolerant. No exposed surfaces on the board, except for the

PCI edge connector are tolerant of voltages greater than 4V. According to the Virtex 5

datasheets, the maximum applied voltage to any IO signals on the FPGA is VCCO. This means

you should not try to over-drive IOs in an FPGA interface above the interface voltage specified

in this manual.

2.2 Other

Some parts of the board are physically fragile. Take extra care when handling the board to avoid

touching the daughtercard connectors. Leave the covers on the daughtercard connectors

whenever they are not in use. Use mounting hardware to secure daughtercards.

2.3 Other, speculative

Do not touch high-voltages.

DN9002K10PCI User Guide www.dinigroup.com 8

QUICK START GUIDE

Do not shatter the user CD.

Do no insert clovers into PC.

Do not pour orange soda onto electronics.

Do not children play with packaging.

Do not let children taste wires.

Do not start smoking. It’s bad for your health.

3Pre-Power on Instructions

The image below represents your DN9002K10PCI. You will need to know the location of the

following parts referenced in this chapter.

DN9002K10PCI User Guide www.dinigroup.com 9

QUICK START GUIDE

Figure 3 DN9002K10PCI configuration controls

The FPGAs on the board are names “FPGA A” through “FPGA F” FPGA A is in the lower

left hand corner as shown in the above photo. FPGA B and C are to its right. The top row of

FPGAs from left to right be named, “FPGA D”, “FPGA E”, and “FPGA F”

To begin working with the DN9002K10PCI, follow the steps below.

3.1 Install Memory

The DN9002K10PCI comes packaged without memory installed. If you want the Dini Group

reference design to test your memory interfaces, you must install memory modules in the

SODIMM slot on the board. The reference design supports DDR2 SODIMM modules in

densities 256MB, 512MB, and 1GB with a CAS latency of 3. (Almost any modern off-the-shelf

laptop memory)

The socket DIMMB is connected to FPGA B. The socket can accept any capacity DDR2

SODIMM module. Note that DDR1 modules will not work in these slots since they are a

completely different pin-out and voltage level.

3.2 Prepare configuration files

The DN9002K10PCI reads FPGA configuration data from a CompactFlash card. To program

the FPGAs on the DN9002K10PCI, FPGA design files (with a .bit file extension) put on the

root directory of the CompactFlash card file using the provided USB card reader.

The DN9002K10PCI ships with a 256MB CompactFlash card preloaded with the Dini Group

reference design. These “bit” files can also be found on the User CD. You can also compile the

reference design source (provided on the CD) and place the generated .bit files on the Compact

Flash card.

DN9002K10PCI User Guide www.dinigroup.com 10

Table of contents