Dynamic Engineering cPCIRepeat32 User manual

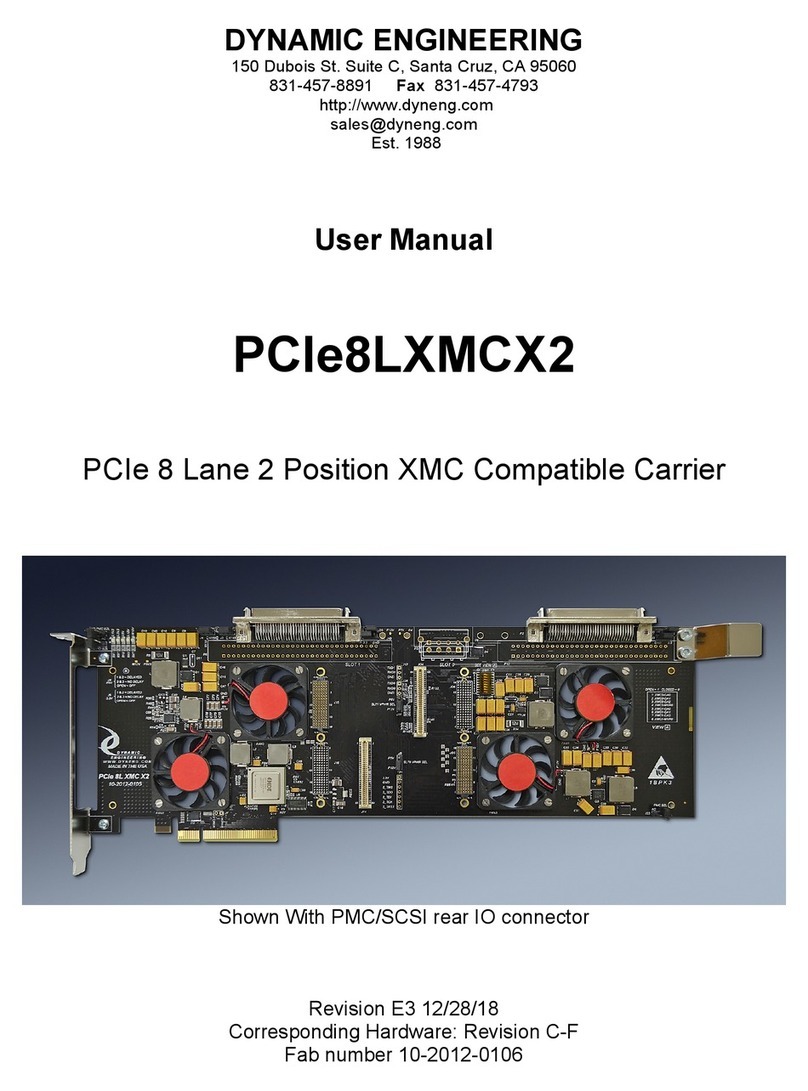

DYNAMIC ENGINEERING

150 DuBois St. Suite C Santa Cruz CA 95060

831-457-8891 Fax 831-457-4793

http://www.dyneng.com

Est. 1988

User Manual

cPCIRepeat32

cPCI 6U 4HP PMC Carrier With PCI Bus Expansion

Extended Temperature

Revision A

Corresponding Hardware: Revision A

Fab number 10-2013-0501

Embedded Solutions Page 2

cPCIRepeat32

cPCI and PMC Compatible Carrier

Dynamic Engineering

150 DuBois St Suite C

Santa Cruz, CA 95060

831-457-8891

831-457-4793 FAX

This document contains information of

proprietary interest to Dynamic Engineering. It

has been supplied in confidence and the

recipient, by accepting this material, agrees that

the subject matter will not be copied or

reproduced, in whole or in part, nor its contents

revealed in any manner or to any person except

to meet the purpose for which it was delivered.

Dynamic Engineering has made every effort to

ensure that this manual is accurate and

complete. Still, the company reserves the right to

make improvements or changes in the product

described in this document at any time and

without notice. Furthermore, Dynamic

Engineering assumes no liability arising out of

the application or use of the device described

herein.

The electronic equipment described herein

generates, uses, and can radiate radio

frequency energy. Operation of this equipment

in a residential area is likely to cause radio

interference, in which case the user, at his own

expense, will be required to take whatever

measures may be required to correct the

interference.

Dynamic Engineering’s products are not

authorized for use as critical components in life

support devices or systems without the express

written approval of the president of Dynamic

Engineering.

Connection of incompatible hardware is likely to

cause serious damage.

©2013-2014 by Dynamic Engineering.

Other trademarks and registered trademarks are owned by their

respective manufactures.

Manual Revision A. Revised 2/19/2014

Embedded Solutions Page 3

Table of Contents

PRODUCT DESCRIPTION 5

Special features: 5

Interrupts and Arbitration 6

Other Signals 6

BUS EXPANSION J2 PIN ASSIGNMENT 7

APPLICATIONS GUIDE 10

Interfacing 10

Construction and Reliability 11

Thermal Considerations 11

WARRANTY AND REPAIR 12

Service Policy 12

Out of Warranty Repairs 12

For Service Contact: 12

SPECIFICATIONS 13

ORDER INFORMATION 13

Embedded Solutions Page 4

List of Figures

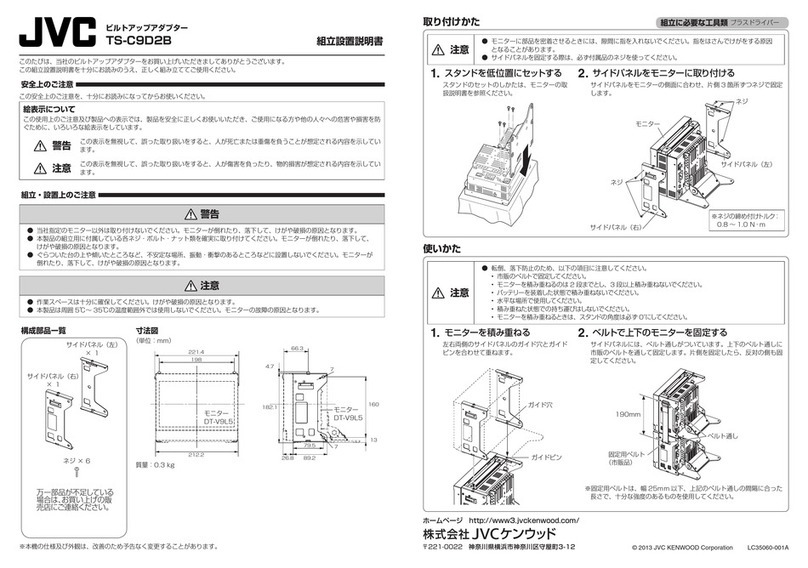

FIGURE 1 CPCIREPEAT32 J2 PIN ASSIGNMENT 9

Embedded Solutions Page 5

Product Description

cPCIRepeat32 is part of the Dynamic Engineering cPCI and PMC compatible family of

modular I/O components.

The cPCIRepeat32 is a 6U 4HP design with one PMC position. The design is rated for

industrial temperature operation “ET” –40C +85C.

The bridge isolates the cPCI PCI bus [J1] from the local PMC PCI bus. Connector J2

has a “Repeated” copy of the PCI bus to be used for bus expansion purposes. Please

note: J2 is not pinned out in the standard manner. Do not use in a backplane not

designed for cPCIRepeat32. The arbitration and clock references from the secondary

side of the bridge are also available on J2.

Easy to use as a plug and play device. In transparent mode no special software is

required for the carrier. A special hidden address range is available to allow high-speed

local bus operations without interfering with the cPCI bus.

Special features:

• Universal cPCI 6U 4HP.

• Extended temperature range [-40 +85C]

LED names within quotes: LED’s for power rails are illuminated when corresponding

voltage is within tolerance.

• LED on PMC Busmode “PMC-0”

• LED on plus 12V “P12V”

• LED on minus 12V “M12V”

• LED on plus 5V “P5V”

• LED on plus 3.3V “P3.3V”

• Secondary VIO set to 3.3V

• 32 bit operation on both PCI buses

• 66 or 33 MHz operation. With 66 MHz. primary bus speed the secondary bus can be

66 or 33 MHz.

• Front panel connector access through cPCI bracket

• JTAG programming support option

• GPIO bus option

cPCIRepeat32 is ready to use with the default settings. Just install the PMC onto the

cPCIRepeat32 and then into the system.

Embedded Solutions Page 6

Interrupts and Arbitration

Request and Grants for 0-6 are tied to J2. The Rqst/Gnt pair 7 is tied to the PMC.

The corresponding IDSEL of AD26 is tied to the PMC. Interrupts from the PMC and

secondary bus are connected to the primary PCI bus. INTA through INTD are mapped

directly to the primary bus segment for J2 and are rotated to connect [PMC] CDAB to

match the IDSEL, Request and Grant. Essentially the PMC is set to be the last item

discovered in the chain.

Other Signals

JTAG support is available for the PMC. The JTAG header positions are clearly marked

in the silk screen. The headers are frequently not used and are not installed unless

requested. Please contact Dynamic Engineering for this option.

The Bridge supports a GPIO function. A header position is available with the positions

clearly marked in the silk-screen. The header is installed by request. Please contact

Dynamic Engineering for this option. The 4 bits are terminated with 4.7KΩto 3.3V.

Embedded Solutions Page 7

Bus Expansion J2 Pin Assignment

J2 Nam e

J 2.E22 CLK0

J 2.D22 G ND

J 2.C22 CLK2

J 2.B22 CLK1

J 2.A22 G ND

J 2.E21 G ND

J 2.D21 AD0

J 2.C21 G ND

J 2.B21 G ND

J 2.A21 AD1

J 2.E20 AD2

J 2.D20 REQ 2

J 2.C20 AD3

J 2.B20 AD4

J 2.A20 G NT 4

J 2.E19 AD5

J 2.D19 AD6

J 2.C19 G NT 1

J 2.B19 G ND

J 2.A19 AD7

J 2.E18 CBE0

J 2.D18 REQ 1

J 2.C18 AD8

J 2.B18 AD9

J 2.A18 G NT 2

J 2.E17 AD10

J 2.D17 AD11

J 2.C17

J 2.B17 G ND

J 2.A17 AD12

J 2.E16 AD13

J 2.D16 G ND

J 2.C16 AD14

J 2.B16 AD15

J 2.A16

J 2.E15 CBE1

J 2.D15 PAR

J 2.C15

J 2.B15 G ND

J 2.A15 SERR

J 2.E14 PERR

J 2.D14 G ND

J 2.C14 REQ 3

J 2.B14 G NT 3

Embedded Solutions Page 8

J 2.A14

J 2.E13 LO CK#

J 2.D13 ST O P

J 2.C13

J 2.B13 G ND

J 2.A13 DEVSEL

J 2.E12 TRDY

J 2.D12 G ND

J 2.C12 IRDY

J 2.B12 FRAME

J 2.A12 G NT 0

J 2.E11 CBE2

J 2.D11 G ND

J 2.C11 AD16

J 2.B11 AD17

J 2.A11 AD18

J 2.E10 AD19

J 2.D10 AD20

J 2.C10

J 2.B10 G ND

J 2.A10 AD21

J 2.E9 AD22

J 2.D9 G ND

J 2.C9 AD23

J 2.B9

J 2.A9 CBE3

J 2.E8 AD24

J 2.D8 AD25

J 2.C8 REQ 0

J 2.B8 G ND

J 2.A8 AD26

J 2.E7 AD27

J 2.D7 G ND

J 2.C7 AD28

J 2.B7 AD29

J 2.A7 AD30

J 2.E6 AD31

J 2.D6

J 2.C6

J 2.B6

J 2.A6

J 2.E5

J 2.D5 G ND

J 2.C5 RST

J 2.B5

J 2.A5 G NT 5

J 2.E4 G ND

Embedded Solutions Page 9

J 2.D4 REQ 4

J 2.C4 REQ 6

J 2.B4 G ND

J 2.A4 G NT 6

J 2.E3 INT D

J 2.D3 REQ 5

J 2.C3 INT C

J 2.B3 INT B

J 2.A3 INT A

J 2.E2 G ND

J 2.D2 G ND

J 2.C2 CLK3

J 2.B2 G ND

J 2.A2 G ND

J 2.E1 CLK6

J 2.D1 CLK7

J 2.C1 G ND

J 2.B1 CLK4

J 2.A1 CLK5

FIGURE 1 CPCIREPEAT32 J2 PIN ASSIGNMENT

Please note: 1) all signals are per PCI specifications even if name is a bit different – no

_N etc. 2) F1-21 odd are also tied to ground.

Embedded Solutions Page 10

Applications Guide

Interfacing

Some general interfacing guidelines are presented below. Do not hesitate to contact the

factory if you need more assistance.

Installation

The PMC is mounted to the cPCIRepeat32 prior to installation within the chassis. For

best results: with the cPCI bracket installed, install the PMC at an angle so that the

PMC front panel bezel penetrates the cPCI bracket then rotate down to mate with the

PMC [PnX] connectors.

There are four mounting locations per PMC. Two into the PMC mounting bezel, and

two for the standoffs near the PMC bus connectors.

Start-up

A third party PCI device cataloging tool will be helpful to check that the VendorID and

CardID are “seen” by the OS.

Watch the system grounds. All electrically connected equipment should have a fail-

safe common ground that is large enough to handle all current loads without affecting

noise immunity. Power supplies and power consuming loads should all have their own

ground wires back to a common point.

Power all system power supplies from one switch. Connecting external voltage to

the cPCIRepeat32 when it is not powered can damage it, as well as the rest of the host

system. This problem may be avoided by turning all power supplies on and off at the

same time. This applies more to the PMC installed into the cPCIRepeat32 than the

cPCIRepeat32 itself, and it is smart system design when it can be achieved.

Table of contents

Other Dynamic Engineering Adapter manuals