UNOPROLOGIC

USB CPLD DEVELOPMENT SYSTEM

Data Sheet

The UnoProLogic is a part of the EPT USB/PLD development system. It provides an innovative

method of developing and debugging the users microcontroller code. It can also provide a high

speed data transfer mechanism between microcontroller and Host PC.

The UnoProLogic board is equipped with an Altera 5M570 PLD; which is programmed using the

Altera Quartus II software. The PLD has 570 Logic Elements which is equivalent to 440

Macrocells. An on board 66 MHz oscillator is used by the EPT-Active-Transfer-Library to

provide data transfer rates of 0.1 Mega Bytes per second. The EPT-Active-Transfer-Library

provides control communication between the objective device and the PLD. Data transfer during

the objective device checkout between the PC and the PLD program is available via the Hyper

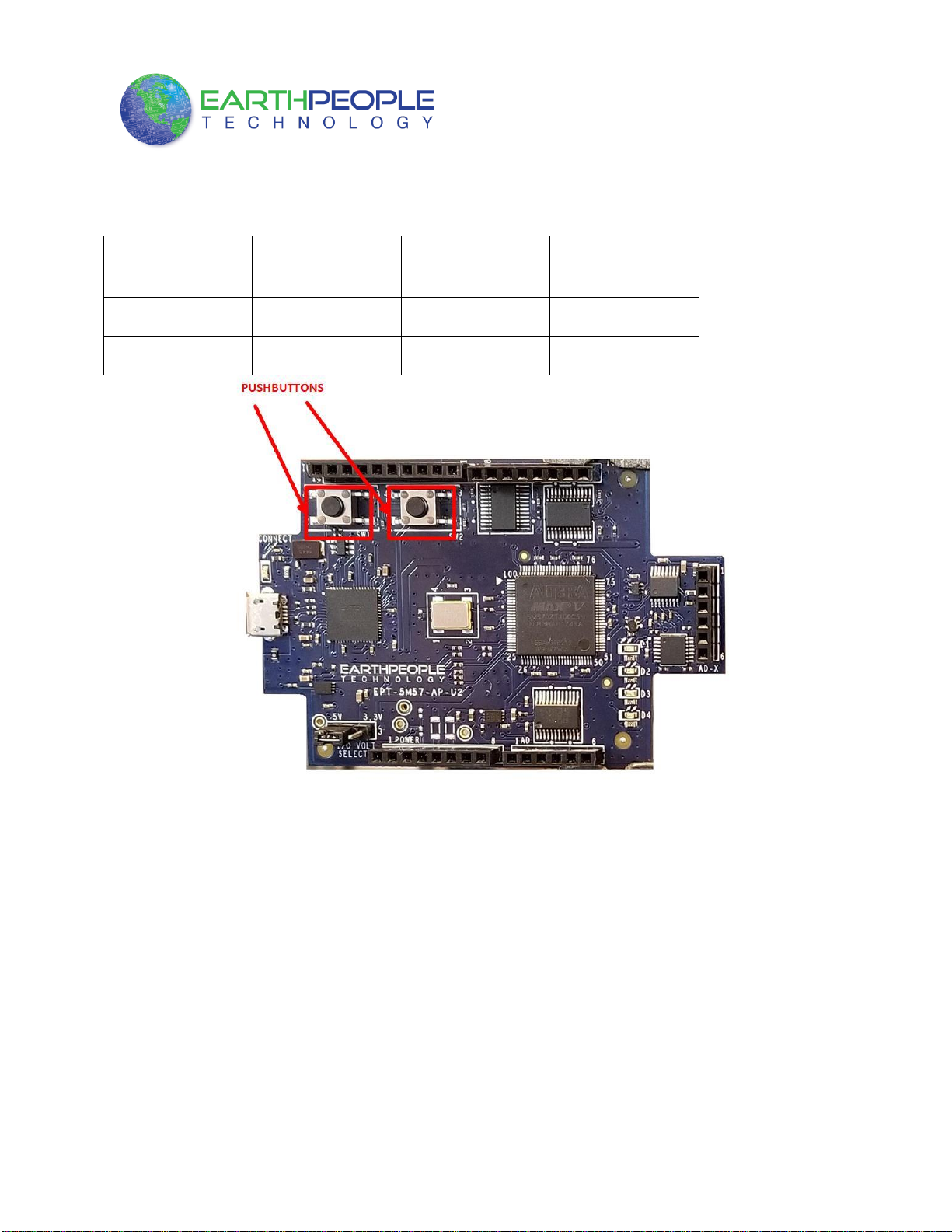

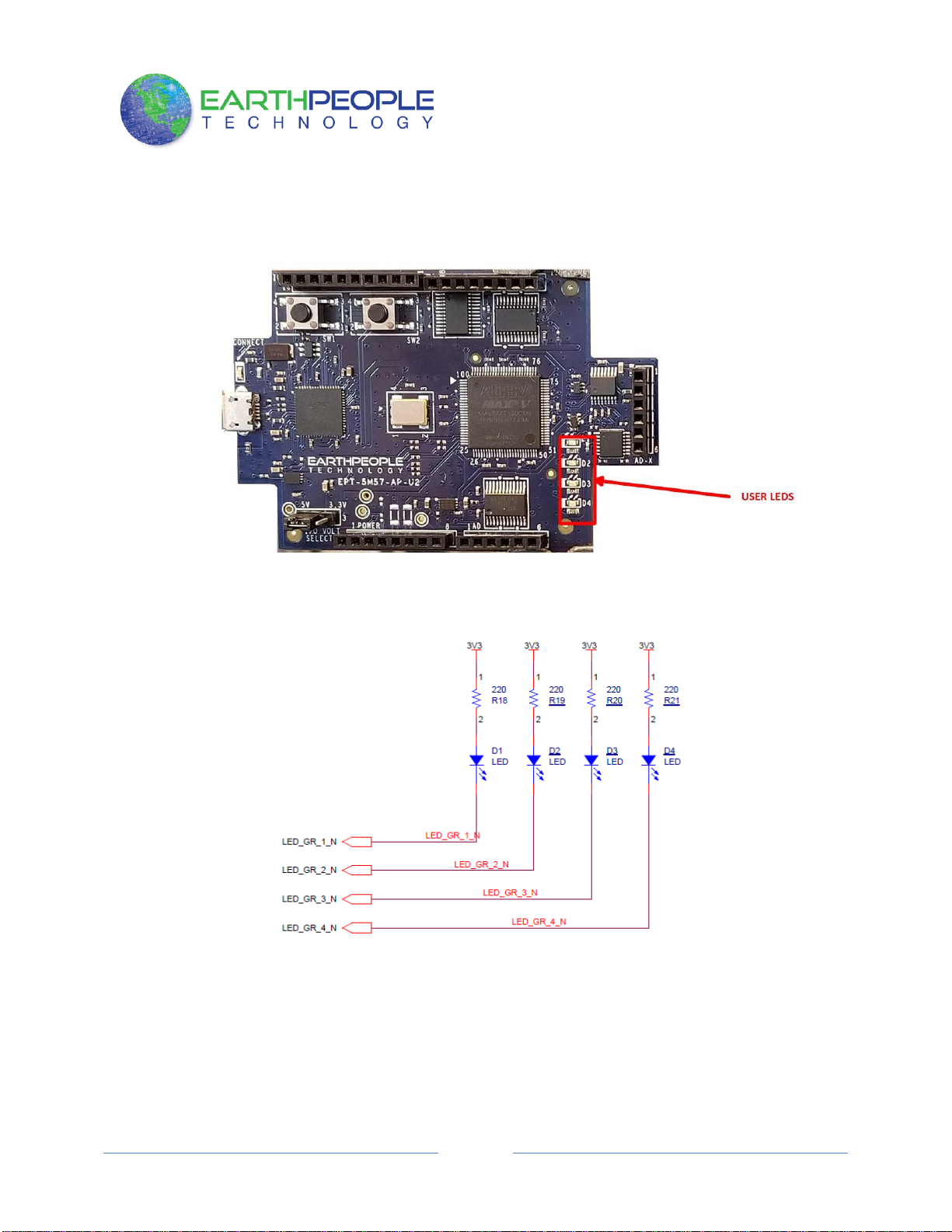

Serial Port. The board also includes the following parts.