Assume the incoming line rate equals

32/31 times 2.488 Gbit/s. Thus, the VCO

frequency should equal 2.568 GHz. The

reference clock input (CKREF, CKREFN)

is defined as 2.488 GHz/62 equal to

40.134 MHz. Now the VCO frequency is

divided by 64 and compared on the PFD.

This will cause the VCO to tune onto a

frequency of 64/62 that is 32/31 times

2.488 GHz due to the PLL feedback.

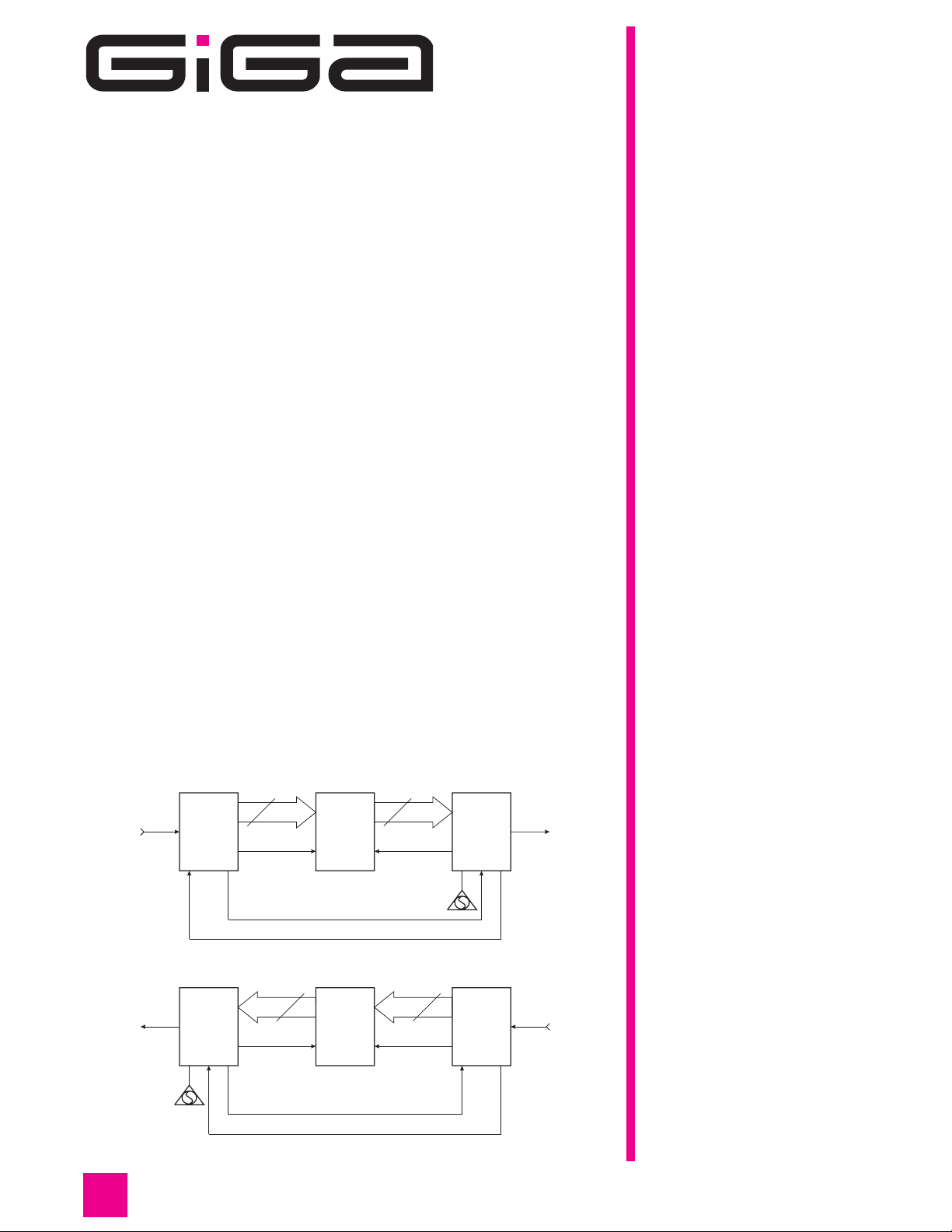

The topology of the circuit splits the line

rate generation from the fraction select

allowing any combination of the two.

For simplicity a third divider that gener-

ates clocks to the de-multiplexer is not

shown on the block diagram.

Lock Detect Circuit

The Lock Detect Circuit continuously

monitors the frequency difference be-

tween the reference clock and the di-

vided VCO clock. If the reference clock

and the divided VCO frequency differ by

more than 500 ppm it switches the PFD

into the PLL in order to pull the VCO

back inside the lock-in range. This mode

is called the acquisition mode.

The PFD is used to ensure predictable

lock up conditions for the GD16556 by

locking the VCO to an external reference

clock source. It is only used during acqui-

sition and pulls the VCO into the lock

range where the Bang-Bang Phase De-

tector is capable of acquiring lock to in-

coming data. The PFD is digital with true

Phase/Frequency detectability.

Once the VCO is inside the lock-range

the lock-detection circuit switches the

Bang-Bang phase detector into the PLL

in order to lock to the data signal. This

mode is called CDR mode.

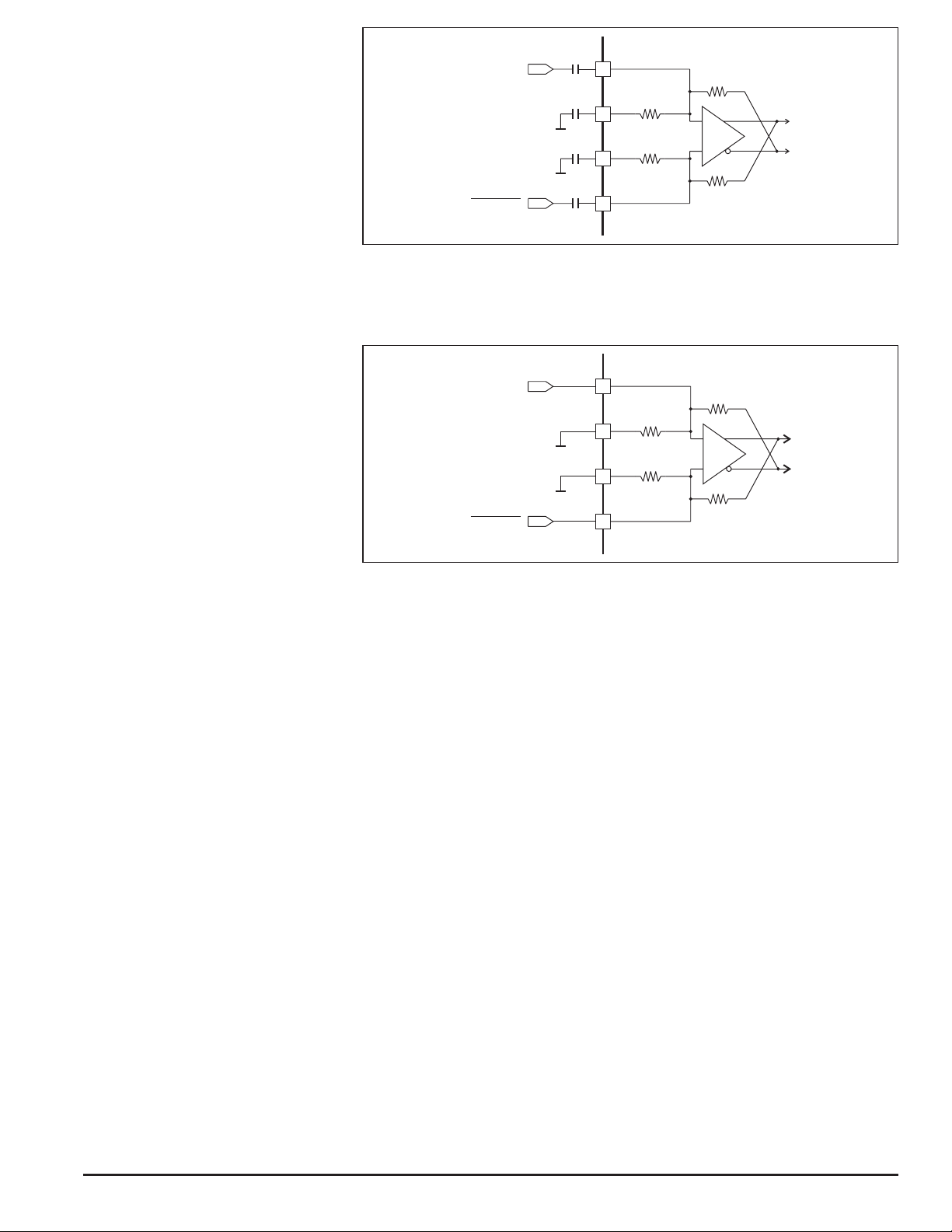

Bang-Bang Phase Detector

The Bang-Bang Phase Detector is used

in CDR mode as a true digital type detec-

tor, producing a binary output. It samples

the incoming data twice each bit period:

once in the transition of the (previous) bit

period and once in the middle of the bit

period. When a transition occurs be-

tween 2 consecutive bits - the value of

the sample in the transition between the

bits will show whether the VCO clock

leads or lags the data. Hence the bit tran-

sition point controls the PLL, thereby en-

suring that data is sampled in the middle

of the eye, once the system is in CDR

mode. The external loop filter compo-

nents control the characteristics of the

PLL.

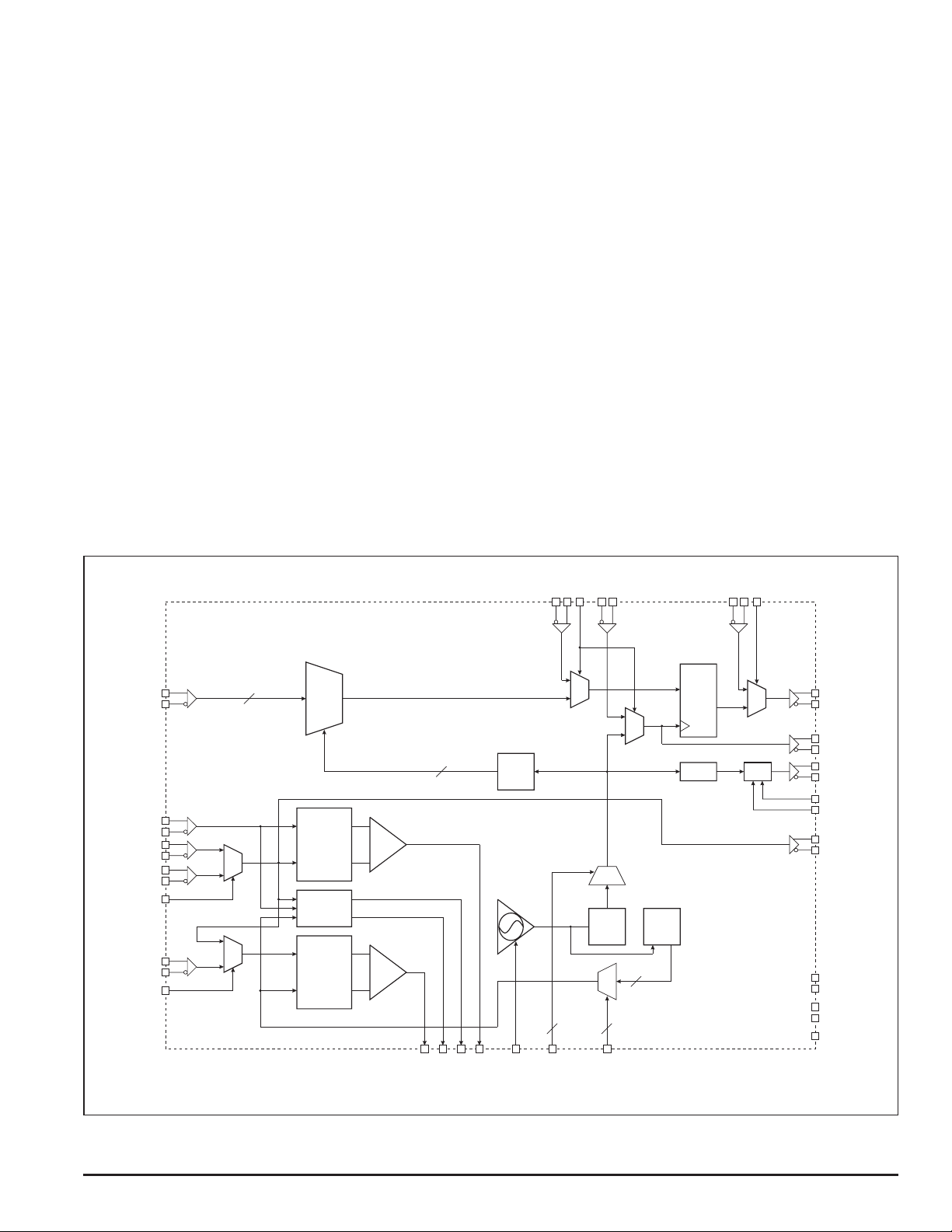

The binary output of either the PFD or

the Bang-Bang Phase Detector (depend-

ing of the mode of the lock-detection cir-

cuit) is fed to a Charge Pump capable to

sink/source current or tristate. The output

of the Charge Pump is filtered through

the Loop Filter and controls the tuning-

voltage of the VCO.

Figure 11.GD16556 - Loop filter

As a result of the continuous monitoring

Lock Detect Circuit the VCO frequency

never deviates more than 500 ppm from

the reference clock before the PLL is

considered to be ’Out of Lock’. Hence the

acquisition time is predictable and short

and the output clock (CKOUT) is always

kept within the 500 ppm limit, ensuring

safe clocking of down stream circuitry.

The LOCK Signal

The status of the lock-detection circuit is

given by the LOCK signal. In CDR mode

LOCK is steady high. In acquisition mode

LOCK is alternating indicating the contin-

uous shifts between the Bang-Bang De-

tector (high) and the PFD (low).

The BC_DET Signal

An internal circuit monitors input data

transitions and gives a BC_DET output

signal which is asserted if more than 256

consecutive identical bits, 0s or 1s, are

detected.

BC_DET will be de-asserted only after

approximately 16 bit transitions are de-

tected within a time period proportional to

the selected data rate (50 ns at STM 16 /

OC-48).

The LOCK_DET Signal

The LOCK_DET signal is a status output,

which monitors the status of the internal

lock detect circuit of the GD16556 CDR

logic and the output of the BC_DET cir-

cuit.

LOCK_DET is asserted (set HIGH) if the

VCO frequency differs from the reference

frequency by ±500 ppm. This ‘out of

lock’condition is detected by the internal

Lock Detect circuit described previously.

LOCK_DET is also asserted in the case

of the absence of data, which is detected

by the BC_DET circuit within the reaction

time of the internal PLL lock detect

system.

If data is absent, the divided VCO fre-

quency will drift away from the reference

frequency until they differ by ±500 ppm.

The internal Lock Detect logic will alter-

nate between CDR and acquisition mode

until data returns, enabling the GD16556

to acquire lock and function in CDR

mode.

The LOCK_DET signal, however, will re-

main asserted until BC_DET is de- as-

serted and the internal lock detect circuit

is operating in CDR mode.

The CDR circuitry of the GD16556 has

been fine-tuned to provide an accurate

stable clock output from the VCO when

data is present. Due to the precise nature

of the internal VCO, when data is absent

the clock output frequency will drift slowly

from the recovered clock frequency until

an out of lock condition is detected. The

time taken for the GD16556 to go ‘out of

lock’in the absence of data will typically

be at least 3 ms, unless an external cir-

cuit is used to pull the VCO frequency

away from the reference frequency.

When loss of data is detected, i.e.

BC_DET is asserted, or the divided VCO

frequency differs from the reference fre-

quency by ±500 ppm, LOCK_DET is as-

serted and the internal lock detect circuit

switches to acquisition mode. This will

give a stable output clock during a loss of

data condition.

When BC_DET is de-asserted and the

divided VCO frequency is within 500 ppm

of the reference frequency, LOCK_DET

will be de-asserted within 500 ms, inde-

pendent of selected data rate.

LOS_DET

The Loss Of Signal DETection

(LOS_DET) alarm output is low during

normal operation.

The LOS_DET signal is the output from a

digital Bit Error Flag (BEF) circuit which

monitors the number of false bit transi-

tions in the data signal. An internal flag is

raised if the number of false transitions is

above a predefined level, i.e. if the Bit

Error Rate (BER) is above the corre-

sponding BER level.

Data Sheet Rev.: 23 GD16556/GD16557* Page 6 of 28

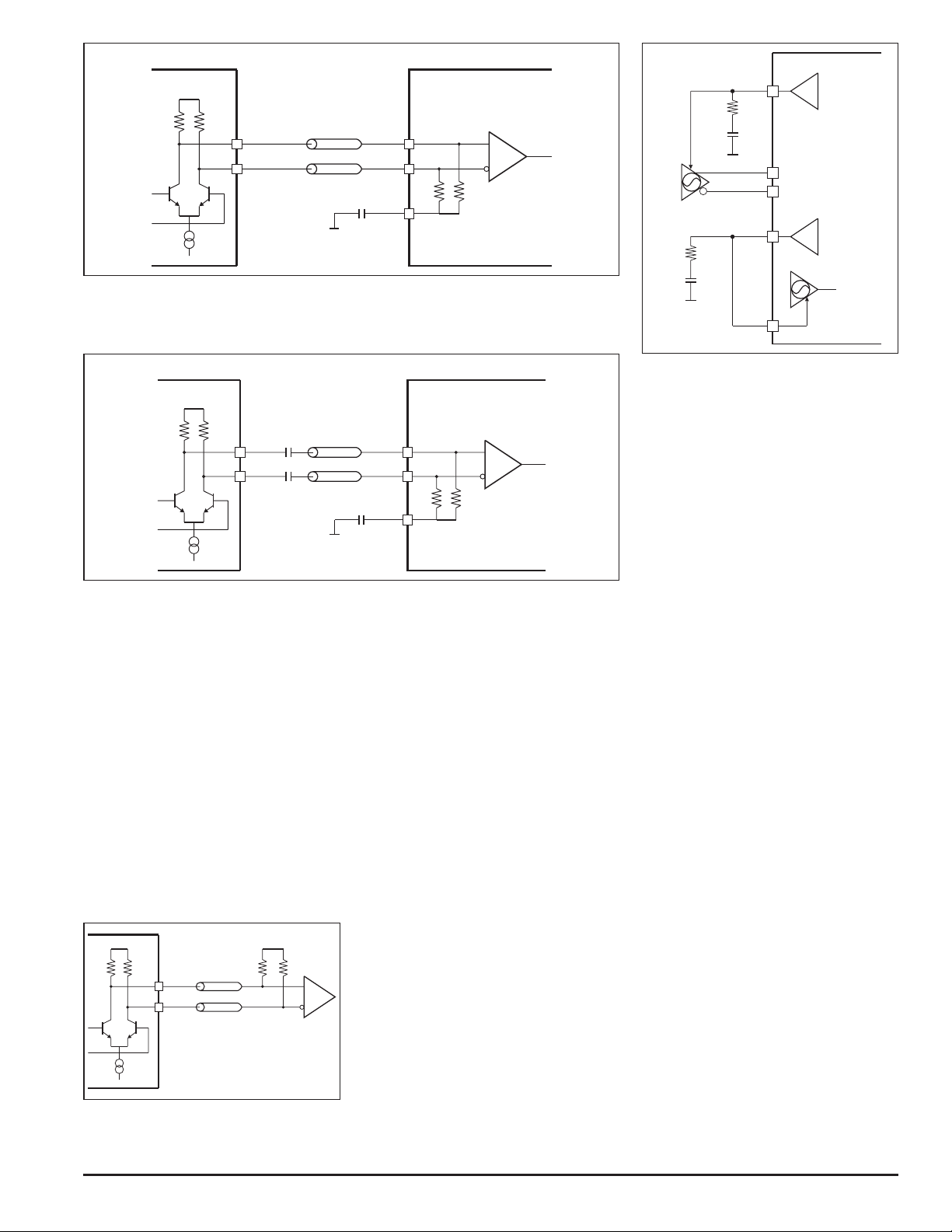

CHAP

OUCHP

1Fm

24 W

VCTL

VDDV