CONTENTS

(continued)

APPENDIX

C

iSBC 303

PARITY

GENERATOR

MULTIMODULE

BOARD

Contents

••.•••..••••.•..•.••.••.••..••••••.•••••••.••••.••.•••

C-l.

Chapter

1.

General

Information

••••••••••••••••••••••••••••••••

1-1.

1-2.

Introduction

.•......•.........•........•..•..•.••.•.•.•..•.•

Description

.••.....•...•.............••....•.••...••••.•••..

1-3.

Equipment

Supplied

••••••••••••••••••••••••••••••••••••••••••

1-4.

Specifications

••••••••••••••••••••••••••••••••••••••••••••••

C-2.

Chapter

2.

Preparation

For

Use

••••••••••••••••••••••••••••••••

2-1.

2-2.

2-3.

Introduction

...•.............•......••...•••..•..•.•..•.•..•

Unpacking &

Inspection

••••••••••••••••••••••••••••••••••••••

Installation

Considerations

•••••••••••••••••••••••••••••••••

2-4.

2-5.

2-6.

2-7.

2-8.

2-9.

2-10.

2-11.

Power

Requirements

••••••••••••••••••••••••••••••••••••••••

Cooling

Requirements

••••••••••••••••••••••••••••••••••••••

Physical

Dimensions

•••••••••••••••••••••••••••••••••••••••

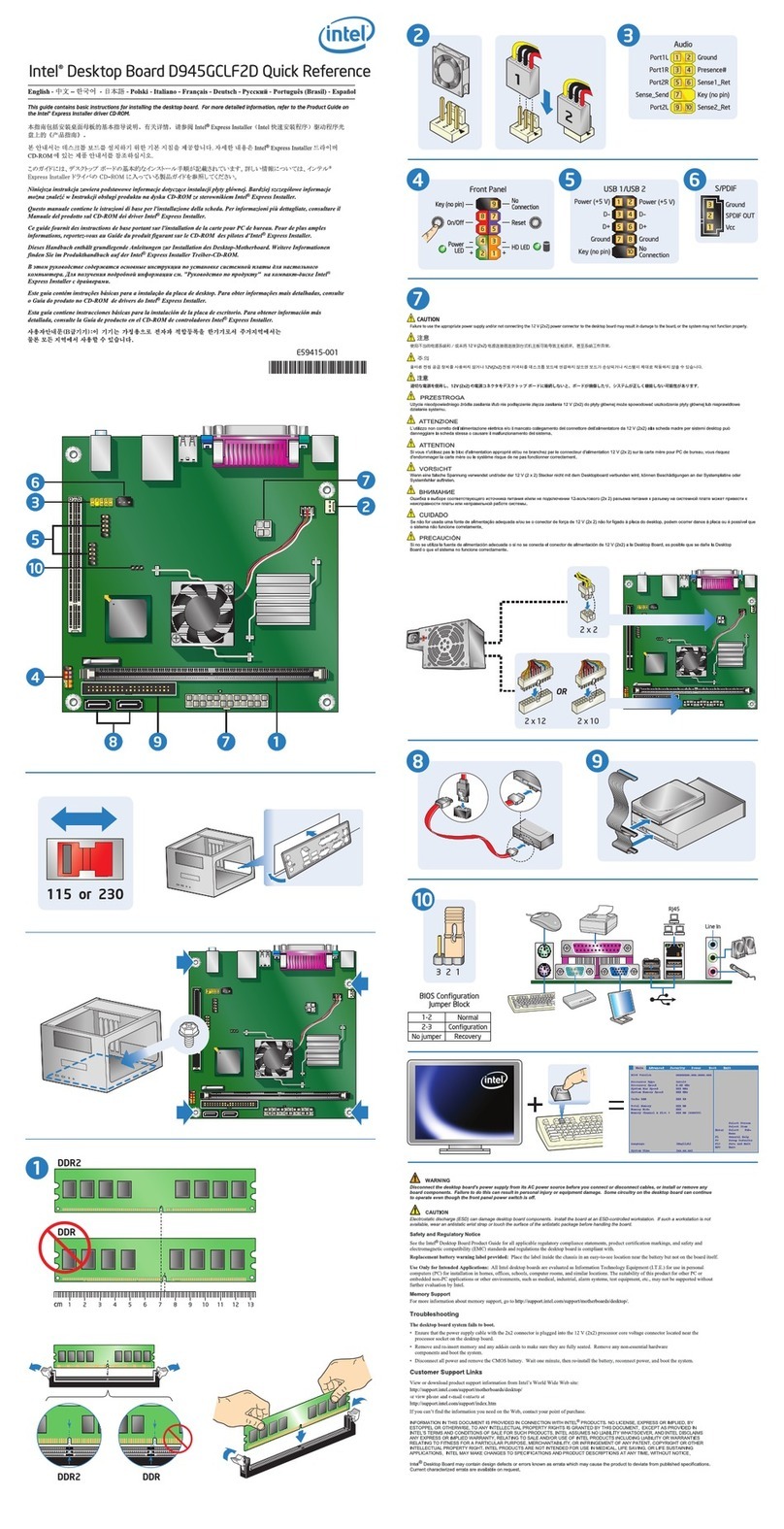

Connector

Configuration

•••••••••••••••••••••••••••••••••••

Jumper

Configuration

••••••••••••••••••••••••••••••••••••••

Installation

Procedure

••••••••••••••••••••••••••••••••••••

Installation

Onto

Base

Board

•••••••••••••••••••••••••••••

Installation

303

Board

•••••••••••••••••••••••••

C-3.

Chapter

3.

Onto iSBC

Programming

Information

••••••••••••••••••••••••••••

3-1.

In

traduction

••••••••••••••••••••••••••••••••••••••••••••••••

3-2.

Programming

Considerations

••••••••••••••••••••••••••••••••••

C-4.

Chapter

4.

Principles

of

Operation

••••••••••••••••••••••••••••

4-1.

Introduction

••••••••••••••••••••••••••••••••••••••••••••••••

4-2.

Functional

Description

••••••••••••••••••••••••••••••••••••••

4-3.

4-4.

4-5.

4-6.

4-7.

4-8.

4-9.

4-10.

Parity

Parity

Parity

Parity

Memory

Generator/Checker

••••••••••••••••••••••••••••••••••

Memory

•••••••••••••••••••••••••••••••••••••••••••••

Generation

•••••••••.•••••••••••••••••••••••••••••••

Checker

••••••.••.•••••.••••.•..•••.••••.•••••••••••

Refresh

Control

••••••••••••••••

Da

ta

Bus La

tches

•••••••.•••••••••••••.•••••••••••••••••••.

Command

Decode

•••••••••••••••••••••••••••••••••••••••.••••

Error

Interrupts

•••.•••.•••.•••.••••••••••••••••••••.••••

4-11.

4-12.

INTR

•••••••••••••••••••••••••••••••••••••••••••••••••••

NMI

••••••••••••••••••••••••••••••••••••••••••••••••••••

4-13.

Visual

Error

Indicators

••••••••••••••••••••..••••••••••••

4-14.

Error

Indicator

Signals

••••••••••••••••••••••••••••••••••

4-15.

Circuit

Arla

lys

is

•••••••••••••••.•••••••••••••••••••••••••••

Memory

••..•••••••••.•••••••.....••••••••••••••••••

4-16.

4-17.

4-18.

4-19.

4-20.

4-21.

4-22.

4-23.

Generation

•.•.••••.•.••••.•..••..•••.•••••••...••.

Parity

Parity

Parity

Data

Bus

INTR

Checker

•.•••••••.••••••••••••••.•••••.••••••••••••

I.a.tches

•••••••••••••••••••••••••••••••••••••••••

.

In

terrupt

•••••••••••••••••••••••••••••••.•••••••••••

NMI

Interrupt

••••••••••••••.•••••••••••••••••••••••••••••

HI/LO

Indicators

•••••••••••••••••••••••••••••••••••••••••

Address

and

Command

Decode

•••••••••••••••••••••••••••••••

viii

Page

C-l

C-2

C-2

C-2

C-3

C-3

C-5

C-5

C-5

C-5

C-5

C-5

C-6

C-6

C-6

C-8

C-8

C-ll

C-14

C-14

C-14

C-15

C-15

C-15

C-16

C-16

C-16

C-16

C-16

C-16

C-17

C-17

C-17

C-17

C-17

C-18

C-18

C-18

C-18

C-19

C-19

C-19

C-19

C-19

C-20