iSYSTEM, October 2003 3/8

Getting started

Setting up the board

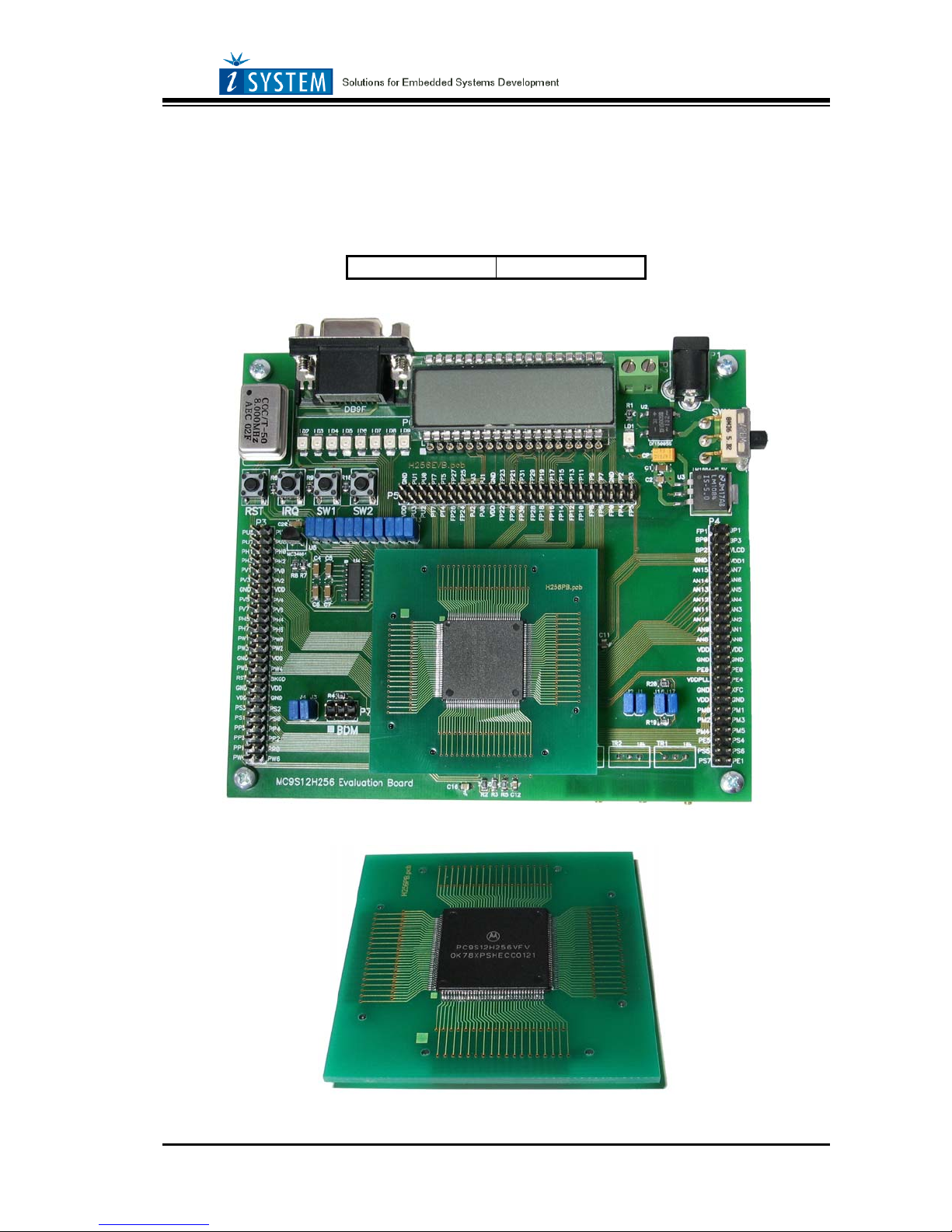

The MC9S12H256 Evaluation board has been tested and programmed with the demo application.

Please examine the board and check that:

• The LCD module and the crystal oscillator are installed.

• All jumpers (J1-J17) are set.

Standalone operation

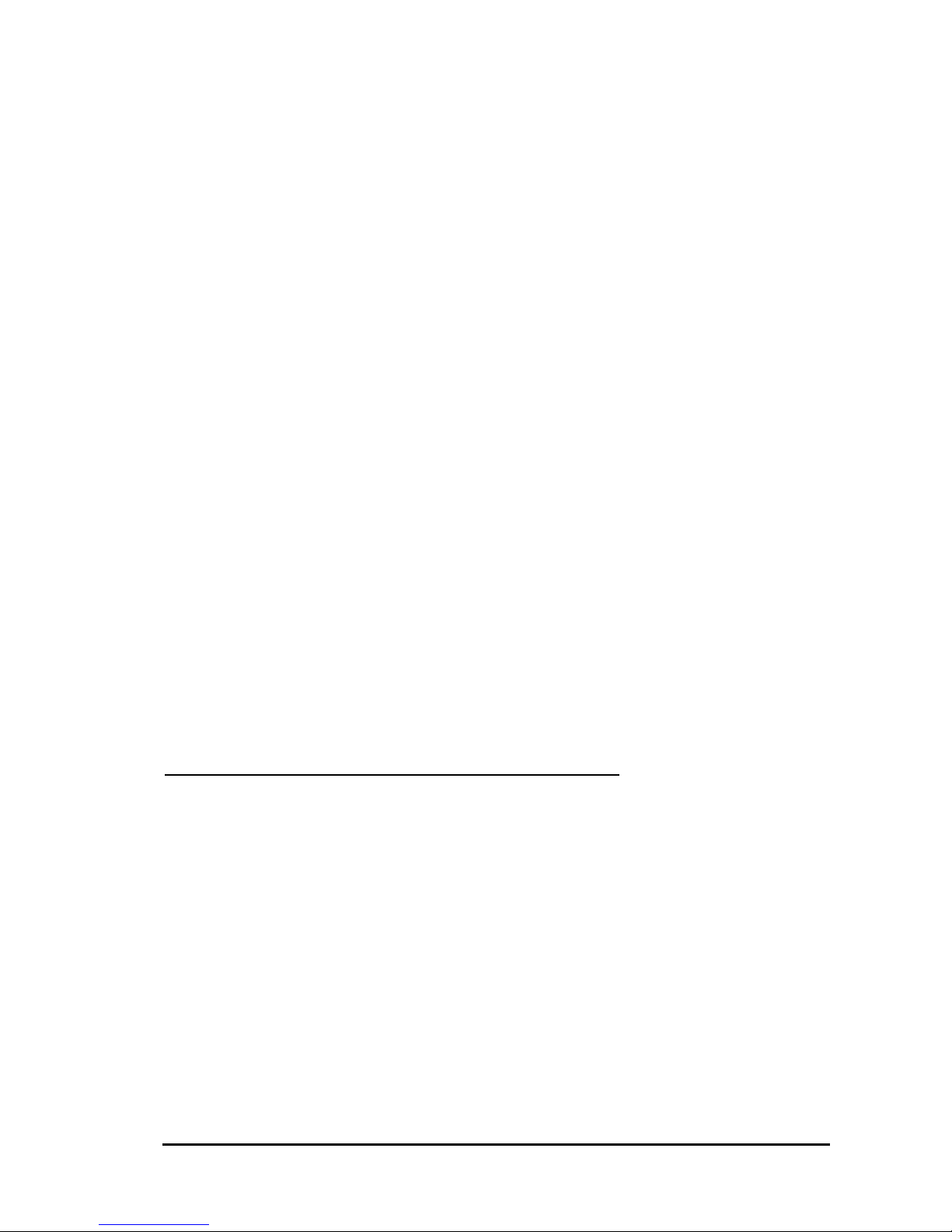

• Make sure that the CPU piggyback is installed.

• Plug the DC source (e.g. AC wall adapter) to the P1 connector or apply DC source to the

connector P2.

• Turn on the power switch SW1 and check the green power LED LD1.

• The board should execute a sample application.

Use with MC9S12H256 ActivePOD

• Remove the CPU piggyback from the board.

• Connect the MC9S12H256 ActivePOD to the board.

• Turn the emulator on and then power the target.

• Run winIDEA, open a sample project and carry out the debug reset. The system is ready for

debugging.

Use with BDM debugger

• Make sure that the CPU piggyback is installed.

• Connect the 68HC(S)12 iCARD to a standard 6-pin BDM debug connector P7

• Turn the emulator on and then power the target.

• Run winIDEA, open a sample project and carry out the debug reset. The system is ready for

debugging.

Running winIDEA

It’s assumed that winIDEA is installed on a PC, where iSYTEM development tool is connected.

Contact your local iSYSTEM sales representative for a sample project or download it from:

ftp://www.asystelectronic.si/winidea/samples/targets/itmc9s12h256.zip

Start winIDEA application from the Start menu and open a sample project workspace. If you are using

ActivePOD, open sampleICE.jrf workspace and if you are using BDM debugger, open sampleBDM.jrf

workspace. Next, check if proper emulator hardware is selected and the communication between the

PC and the emulator.

Carry out the debug reset and run the application (debug run) in case of BDM debugger and carry out

the debug download and run the application (debug run) in case of MC9S12H256 ActivePOD.

Blinking red LEDs (LD2-LD9) and a “Welcome” title on the LCD display indicate a working system.

Additionally, a test string is sent to the host RS232 terminal.

There are four push buttons on the board designated SW1, SW2, RST and IRQ. RST resets the

complete system. Make sure that ‘Reset from target’ option is checked in winIDEA when using RST

button and the development system is connected to the board. IRQ turns on all LEDs. SW1 turns on

one LED and shift its position to the left for each consecutive push. SW2 does the same except that it

shifts in the opposite direction.

Trimmer TR1 controls the LCD brightness. Use a mini-screwdriver to adjust it.

Trimmers TR2 and TR3 are connected to the CPU A/D converter. TR2 is connected to the channel 0

and TR3 to the channel 1. Refer to the board schematic for more details.