INTEGRATED CIRCUITS DIVISION

LITELINK III Evaluation Board Users Guide

6www.ixysic.com UG-CPC5622-EVAL-600R - Rev A

polarity. This functionality is provided by the compact

CPC5712U Voltage Monitor that uses high value

resistors to bridge the barrier and only five small

resistors to set the voltage detectors switching point

thresholds and hystereses.

Three voltage detector outputs provide the information

necessary to determine the loop’s status. They are: 1)

LOOP; 2) LIU*; and 3) POLARITY. The loop status

can be determined by examining the state of the

detectors.

For example, equipment such as satellite set top

boxes and security systems that automatically dial out

need to know if the line is attached to the network

(loop battery present), and if the line is available for

use (no off-hook by another device or a phone). To

make this determination, the logical levels of the

LOOP and LIU* signals need to be considered.

Because LOOP = 0 indicates there is no battery feed

from the network, the line is not available for service

and the LIU* output has no meaning. With LOOP = 1,

battery feed from the network is present and the LIU*

output is used to determine the availability of the line.

With LIU* = 0, another device on the line is off-hook

and again, the line is not available. Only when

LOOP = 1 AND LIU* = 1 is the line available.

3.6 PCB Capacitor and Noise Cancellation Synopsis

This evaluation board addresses a noise issue

reported by customers using ungrounded two-prong

AC switching power supplies. Ungrounded power

supplies generate a common mode voltage on the low

voltage side of the device that has frequency

components consisting of the power line fundamental,

harmonics of the power line frequency, and power

supply switching frequencies with harmonics.

A low cost solution is presented that uses the small

capacitance from copper shapes on the printed circuit

board to insert an inverted phase noise current into a

summing amplifier to resolve the transmit path noise

issue and manipulation of existing feedback loops to

solve the receive path noise issue.

Above the LITELINK symbol on the schematic shown

in Figure 3 on Page 8 is a capacitor labeled C_PCB.

This very small capacitor of approximately 60 - 85 fF is

constructed from PCB copper shapes to couple the

common mode noise from the low voltage side into

LITELINK’s transmit path at the NTS node on pin 26.

NTS is an inverting input of an amplifier whose output

is located at node NTF on pin 26. Using this amplifier’s

input as a summing node for the noise, the common

mode conversion in the transmit path is greatly

reduced. This performance improvement is easily

verified by the Longitudinal Balance measurement.

Enhancing the common mode rejection in the transmit

path greatly reduces the noise power output onto tip

and ring. This provides the mechanism to improve the

common mode noise conversion in the receive path.

In practice, normal full duplex voice transmission onto

tip and ring utilizes a cancellation circuit, commonly

referred to as a “transhybrid” circuit, to reduce the

power level of the transmit signal being returned to the

talker via the receive path. This returned signal is

ofttimes referred to as the reflected signal. Transhybrid

cancellation circuits are generally implemented using

the summing node of an amplifier to null out the

reflected signal. Perfect cancellation occurs when the

currents of the reflected signal in the receive path and

the transmit signal from the transmit path into the

summing node have equal magnitude and are 180

apart. In this type of circuit configuration when one

signal into the summing node is missing, the other

signal is passed through the amplifier and continues

through the receive path.

The noise cancellation circuit for the receive path

takes advantage of this behavior. With very little of the

transmit noise remaining in the signal output onto tip

and ring, the noise generated in the transmit path is

passed through the transhybrid cancellation circuit

and continues through the receive path. When this

noise signal combines with the common mode

conversion noise generated by the receive path, the

two noise signals effectively cancel each other out

resulting in a clean receive transmission path. This is

due to the noise signals being out of phase with each

other and the original transmit noise signal being

properly scaled to match the magnitude of the

generated receive path noise.

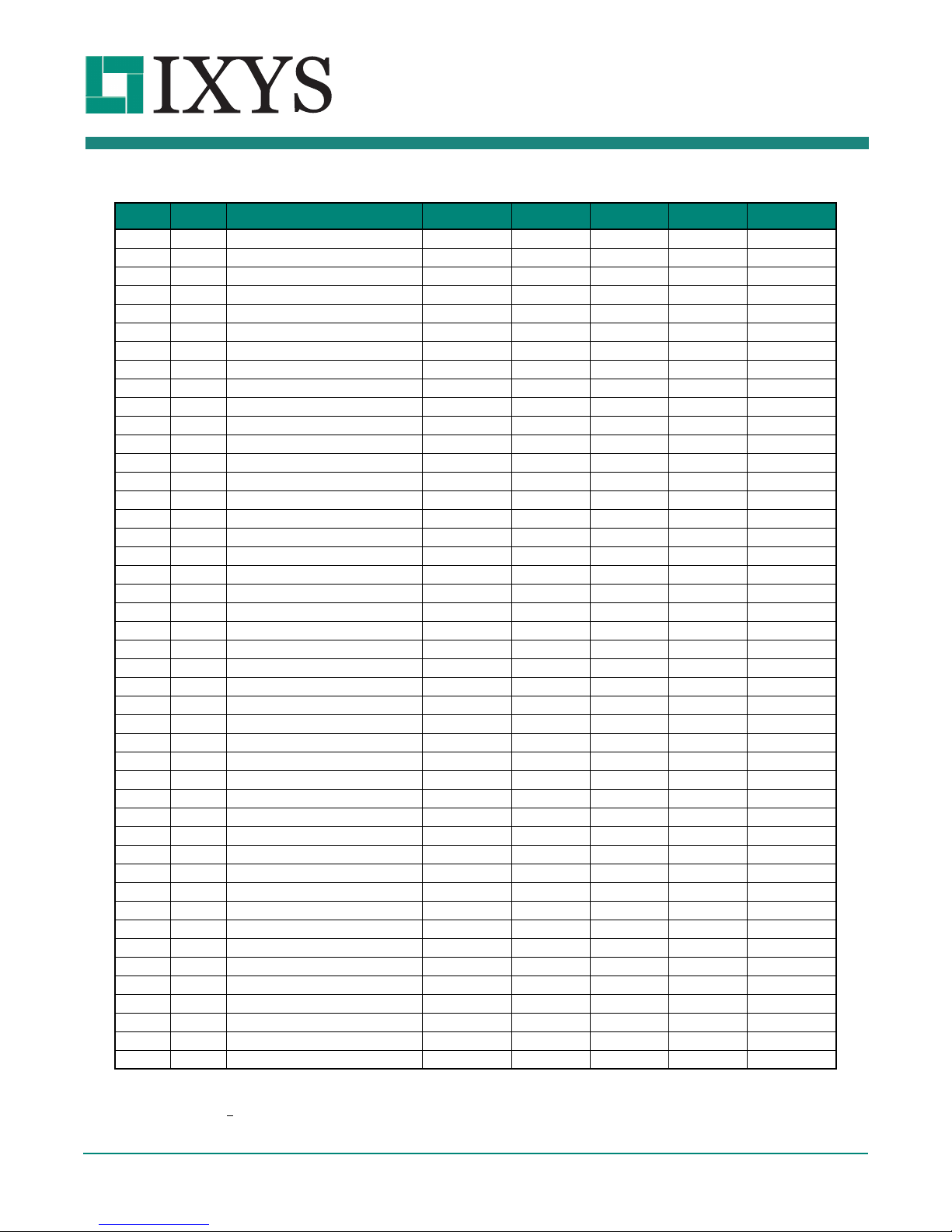

3.7 Stuffing Options

CPC5622-EVAL-600R EvaluationBoardscan beused

to evaluate LITELINK III circuits connected to virtually

any type of host equipment having an analog interface

with many types of telephone networks. This flexibility

will often require changes to the components in the

circuit.