Lauterbach XA51 User manual

XA51 Monitor 1

©1989-2019 Lauterbach GmbH

XA51 Monitor

TRACE32 Online Help

TRACE32 Directory

TRACE32 Index

TRACE32 Documents ......................................................................................................................

ICD In-Circuit Debugger ................................................................................................................

Processor Architecture Manuals ..............................................................................................

XA51 .........................................................................................................................................

XA51 Monitor ........................................................................................................................ 1

Brief Overview of Documents for New Users ................................................................. 2

WARNING ........................................................................................................................... 4

Quick Start of the 51XA ROM Monitor ............................................................................. 5

Troubleshooting ................................................................................................................ 7

FAQ 7

Basics ................................................................................................................................. 8

Monitor Features 8

Monitor Files 8

Address Layout 8

Vector Table 9

Configuration 9

General SYStem Settings and Restrictions .................................................................... 10

SYStem.CPU CPU type 10

General Restrictions 10

Memory Classes ................................................................................................................ 11

Support ............................................................................................................................... 12

Available Tools 12

Compilers 12

Realtime Operation System 12

Debuggers 12

Products ............................................................................................................................. 13

Product Information 13

Order Information 13

XA51 Monitor 2

©1989-2019 Lauterbach GmbH

XA51 Monitor

Version 16-Apr-2019

Brief Overview of Documents for New Users

Architecture-independent information:

•“Debugger Basics - Training” (training_debugger.pdf): Get familiar with the basic features of a

TRACE32 debugger.

•“T32Start” (app_t32start.pdf): T32Start assists you in starting TRACE32 PowerView instances

for different configurations of the debugger. T32Start is only available for Windows.

•“General Commands” (general_ref_<x>.pdf): Alphabetic list of debug commands.

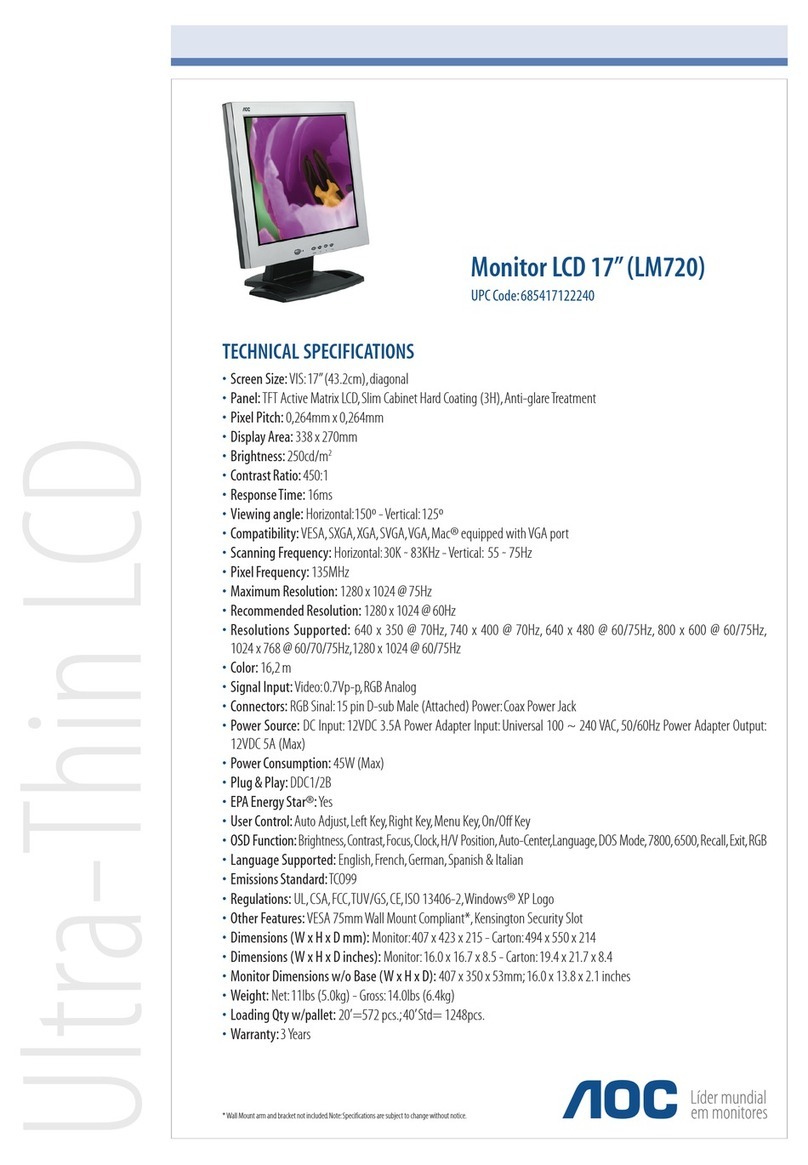

P:003076 \\IAR196\iar196\sieve+86 ........... MIX AI

E::w.d.l

addr/line code label mnemonic comment

P:00306E C318041C st 1C,4[18]

607 while ( k <= SIZE )

P:003072 A318041C ?0178: ld 1C,4[18]

P:003076 BD1220 ldbse 20,#12

P:003079 88201C cmp 1C,20

P:00307C D225 jgt 30A3 ; ?0177

{

609 flags[ k ]

P:00307E 111C ?0179: clrb 1C E::w.v.f /l

P:003080 A118C220 ld 20,#0C21 -001 main()

P:003084 C81C push 1C j = 24910

P:003086 A318061C ld 1C,6[18] p = 0x0C214

P:00308A 64201C add 1C,20 return = 18

0 1 2 3 0123 pop 20 -000 sieve()

E::w.r 00 00 C0 7F .... stb 20,[1C] i = 0

ST _ SP 0CA12 00 00 00 00 .... k += primz primz = 3

I _ PC 3076 00 00 D1 F4 .... k = 18

Cy _ PSW 10 00 00 FF FF anzahl = 0

VT V IM 0 C1 0B 00 00 E::w.v.v flags return = 18

V _ IM1 0 flags = (1, 1, 1, 0, 1, 1,

XA51 Monitor 3

©1989-2019 Lauterbach GmbH

Architecture-specific information:

•“Processor Architecture Manuals”: These manuals describe commands that are specific for the

processor architecture supported by your debug cable. To access the manual for your processor

architecture, proceed as follows:

- Choose Help menu > Processor Architecture Manual.

•“OS Awareness Manuals” (rtos_<os>.pdf): TRACE32 PowerView can be extended for operating

system-aware debugging. The appropriate OS Awareness manual informs you how to enable the

OS-aware debugging.

XA51 Monitor 4

©1989-2019 Lauterbach GmbH

WARNING

NOTE: Do not connect or remove probe from target while target power is ON.

Power up: Switch on emulator first, then target

Power down: Switch off target first, then emulator

XA51 Monitor 5

©1989-2019 Lauterbach GmbH

Quick Start of the 51XA ROM Monitor

Starting up the ROM Monitor is done as follows:

1. Select the device B: for the ROM Monitor.

2. Power the system down (optional).

This instruction is necessary when the system is restarted. When the system is active while you try to

reinitialize it, you get an error message.

3. Map the EPROM simulator. The mapping of the EPROM simulator is described in the section

“Mapping the EPROM simulator”.

4. Load the application program.

The format of the Data.LOAD command depends on the file format generated by the compiler. The

corresponding options for all available compilers are listed in the compiler list. A detailed description of the

Data.LOAD command is given in the Emulator Reference Manual.

5. Load the monitor program. Usally the monitor program runs at address 4000 in the ROM area.

NOTE: Do not connect or remove probe from target while target power is ON

Power up: Switch on emulator first, then target

Power down: Switch off target first, then emulator

b:

sys.d

d.load.ht appl.hex

d.load.b romxa.bin 0x0--0x3f /ny

d.load.b romxa.bin 0x4000 /offset 0x4000 /ny

XA51 Monitor 6

©1989-2019 Lauterbach GmbH

Set other vector locations (e.g. NMI) as required.

6. Set the polarity of the Reset and NMI signal according to your target. The NMI signal is optional,

it can be used to interrupt the program.

7. Start the ROM Monitor. If the RESET output of the ESI is not connected you must press the

RESET button on your target after entering this command.

A typical start sequence is shown below:

The start up can be automated using the programming language PRACTICE.

x.respol -

x.nmipol -

x.nmibreak on

sys.up

; the EPROM (8-bit) is in the addressrange 0x0--0x7fff

; the RAM is in the addressrange 0x8000--0x0ffff

b:

sys.d

winclear

map.res

map.bus16 0x0--0x1ffff

d.load.ht htc.hex /p

d.load.b romxa.bin 0x0--0x0ff

/ny

d.load.b romxa.bin 0x4000

/offset 0x4000 /ny

d.s p:0x80 %w 0x8f00 0x4050

x.respol -

x.nmipol -

x.nmibreak on

sys.up

d.s sfr:0x426 0x81

d.s sfr:0x4a0 0x7

r.s im 0x0

; select the Debugger device

; switch the system down

; clear all windows

; map the EPROM simulator

; load the application

; overload this with the monitor

; set the Interupt vector for manual

break

; adapt the polarity of RES and NMI

; enables the connection of the NMI

signal

; power the system up

; enable EXTINT0 as manual break

XA51 Monitor 7

©1989-2019 Lauterbach GmbH

Troubleshooting

FAQ

No information available

EPROM

Simulator Error

on Data

Modification

Ref: 0056

Why crashes ROM monitor after modification of EPROM?

Check that there is enough space left on the stack. See also "Restrictions for

Stack Requirements".

Step or

Breakpoint

Fails

Ref: 0061

Why does single step or breakpoint not work?

Check that there is enough space left on the stack before and after the execution

of the instruction. See "Restrictions for Stack Requirements". Make sure that the

single step and INT3 vector (1 + 3) are valid and point to the correct monitor

entry.

Stepping Fails

when

Executing MOV

SP,xxx

Ref: 0062

Why does stepping fail, when executing a MOV SP,xxx instruction?

Check that there is enough space left on the stack before and after the execution

of the instruction. See "Restrictions for Stack Requirements".

Check that the value for the CP is within limits for the CPU and that the register

space ist not beeing overwritten by the stack. See "Restrictions for Stack

Requirements".

XA51 Monitor 8

©1989-2019 Lauterbach GmbH

Basics

Monitor Features

The monitor requires no stack during startup and memory operations. A valid stack is only required for single

step and go commands. This allows to use the monitor even when the stack is not valid. External RAM

memory is not required during startup and for memory operations. This allows to use the monitor also on not

fully functional hardware. The NMI pin of the EPROM Simulator can be used to manually stop the target

program.

Monitor Files

The 'romxa' and 'romxaw' monitors are for Eprom Simulator solutions, while the 'romxae' monitor is used as

foreground monitor for Emulators. By using a foreground monitor the target program can be single stepped

without stopping the target processors interrupts. Both monitors have the same source file 'romxa.asm'. This

sourcefile should not be modified, it is only included for reference purposes.

Address Layout

The Rom Monitor is freely relocatable in the first 64K of the address space by reassembling the source. The

communication area for the Eprom Simulator is located at the fixed address 1000 to 1FFF for 8-bit EPROMs.

For 16-bit EPROMs the communication area is at address 2000--3FFF.

The monitor program consists of three parts:

•VectorTable

• Configuration Table

• Monitor Program Code

The '.bin' and '.asm' files contain all three parts of the monitor. The address layout of the default monitor is as

follows:

0x0000--0x003F

0x4000--0x401F

0x4020--0x7fff

Vector Table

Configuration Table

Monitor Code

XA51 Monitor 9

©1989-2019 Lauterbach GmbH

Vector Table

For the first tests of a software, the '.bin' files can be loaded with vector and configuration table. When the

vector table becomes part of the application, it is not loaded with the monitor. Instead the table is setup

according to the application (the table may also reside in RAM). Some vectors must be set up to point into

the monitor program code. The entry points are located at the beginning of the monitor.

Configuration

The configuration table of the monitor must always be located directly before the monitor code. The default

location used in the binary files is 4000 (hex).

• Max. allowed SFR address (word at offset 02H)

This allows to make reduce the memory required by the ROM Monitor. Most part of the ROM Monitor code

is required for a free access to all SFRs. The code for accessing the SFRs is placed at the end of the

monitor. If the upper SFRs are not required, the monitor can be made shorter and the new upper limit can be

entered in this configuration byte. The monitor can be made 12 bytes shorter for each SFR that is not used.

vector addr entry point usage

0000 4020+20 Reset

0004 4020+30 Breakpoint Trap

xxxx 4020+30 Manual Break (optional)

yyyy 4020+40 Any unused vector may be handled by the monitor

XA51 Monitor 1 0

©1989-2019 Lauterbach GmbH

General SYStem Settings and Restrictions

SYStem.CPU CPU type

Selects the processor type. The ROM debugger requires may also require a modification in the configuration

table for some processor types.

General Restrictions

Format: SYStem.CPU <mode>

<mode>: XAG3

Stack Memory The ROM debugger needs 16 bytes of memory on the current stack

for starting and stopping the emulation.

Floating Data Bus

(only ROM Emulator)

The data bus must have pull-up and pull-down resistors to have

the pattern 0feff on the bus when the EPROM emulator is inactive.

Watchdog Timer The watchdog timer is disabled in the ROM Monitor

XA51 Monitor 1 1

©1989-2019 Lauterbach GmbH

Memory Classes

Memory Class Description

DData

PProgram

X External access (8051 compatible access)

SFR SFR Register access

XA51 Monitor 1 2

©1989-2019 Lauterbach GmbH

Support

Available Tools

tbd

Compilers

Realtime Operation System

No RTOS supported.

Debuggers

Language Compiler Company Option Comment

C HTC-XA Microchip Technology

Inc.

HITECH

C HICROSS-XA NXP Semiconductors HICROSS

C CXA TASKING IEEE

CPU Tool Company Host

WINDOWS CE PLATF.

BUILDER

- Windows

CODE::BLOCKS - -

C++TEST - Windows

ADENEO -

X-TOOLS / X32 blue river software GmbH Windows

CODEWRIGHT Borland Software

Corporation

Windows

CODE CONFIDENCE

TOOLS

Code Confidence Ltd Windows

CODE CONFIDENCE

TOOLS

Code Confidence Ltd Linux

EASYCODE EASYCODE GmbH Windows

ECLIPSE Eclipse Foundation, Inc Windows

XA51 Monitor 1 3

©1989-2019 Lauterbach GmbH

Products

Product Information

Order Information

CHRONVIEW Inchron GmbH Windows

LDRA TOOL SUITE LDRA Technology, Inc. Windows

UML DEBUGGER LieberLieber Software

GmbH

Windows

SIMULINK The MathWorks Inc. Windows

ATTOL TOOLS MicroMax Inc. Windows

VISUAL BASIC

INTERFACE

Microsoft Corporation Windows

LABVIEW NATIONAL

INSTRUMENTS

Corporation

Windows

TPT PikeTec GmbH Windows

CANTATA QA Systems Ltd Windows

RAPITIME Rapita Systems Ltd. Windows

RHAPSODY IN MICROC IBM Corp. Windows

RHAPSODY IN C++ IBM Corp. Windows

TESSY Razorcat Development

GmbH

Windows

DA-C RistanCASE Windows

TRACEANALYZER Symtavision GmbH Windows

ECU-TEST TraceTronic GmbH Windows

UNDODB Undo Software Linux

TA INSPECTOR Vector Windows

VECTORCAST UNIT

TESTING

Vector Software Windows

VECTORCAST CODE

COVERAGE

Vector Software Windows

CPU Tool Company Host

Table of contents