4 Technical Manual

Technical Data

3. Technical Data

CONCEPT L 42

Display:

Model: PDP42V6####

Display Type: AC—PDP, V6

Screen size: 107 cm (42”)

Active screen (h x b): 920,1 mm x 518,4 mm

Aspect ratio: 16:9

Physical Resolution in Pixel: 852 x 480

Colors: 16,77 Mio.

Maximum Brightness: typ. 1000 cd / m2 (white peak @ 4% display load)

Maximum contrast ratio: typ. 3000:1 (dark room, white peak @ 4% display load)

Viewing angle (A/B, L/R): 800/800 , 800/800, typ.

Limitation power consumption: APC (Automatic Power Control)

Color temperature: 9500K (@ 20% grey) characterictics acc. to manufact. spec,

2—point adjustment not possible.

A.m. values are valid after 20 min operation at an ambient temp. of 25°C.

EMI Shielding Glass:

Type: Security Shatterproof Glass incl. Mesh

Transmission: 48% +/— 5%

Power requirement:

Mains Inlet: 115 — 230V ~ +/— 10%

Mains frequency: 50/60 Hz +/— 6%

Power consumption: 5W typ. in Standby, ca. 350W in operation

Inrush current: 40A max.

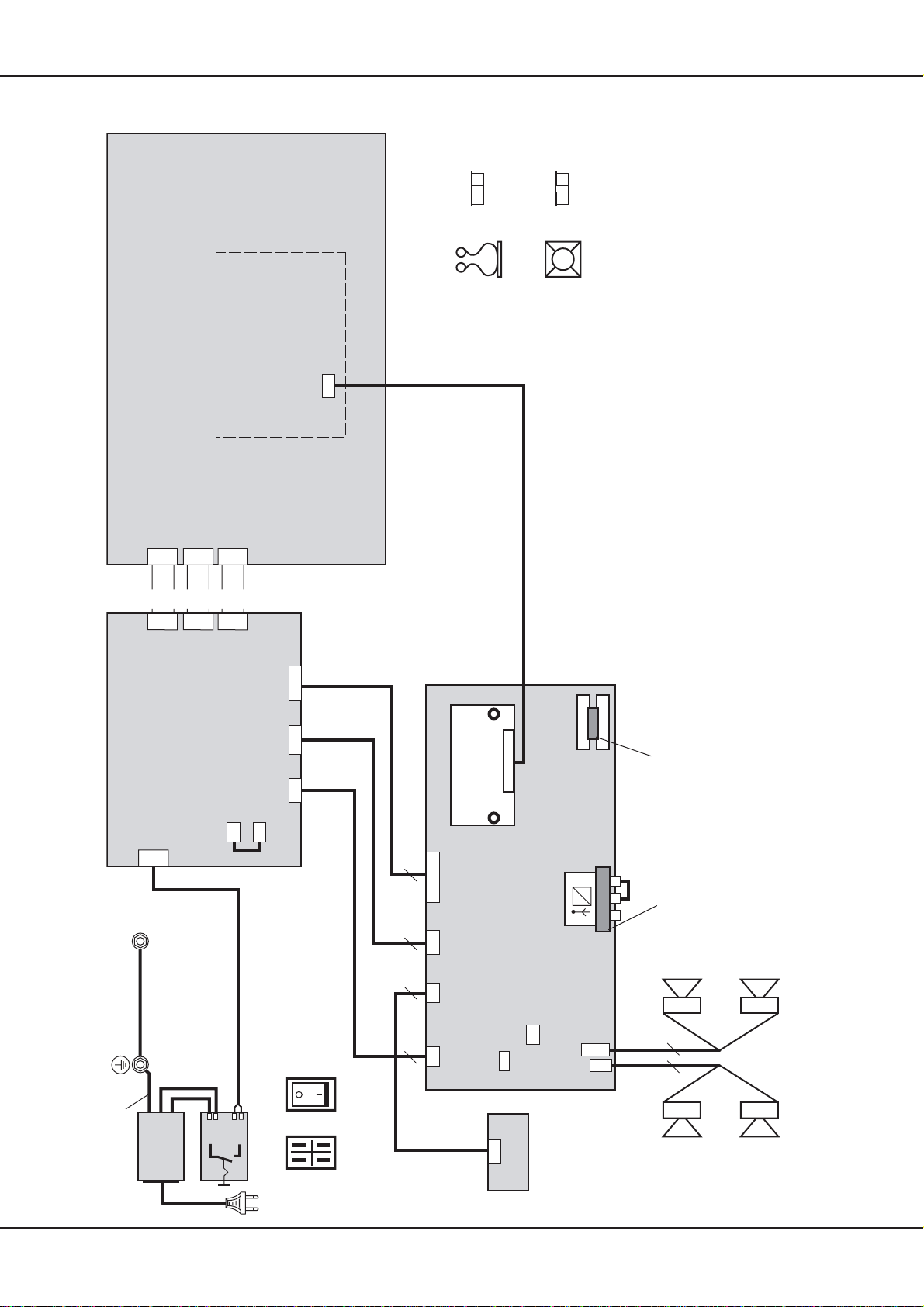

In— / Outputs:

Description Input / Output Signal

Cinch / Cinch: disabled no function

Cinch / Cinch: output Audio Subwoofer Line out / n.c.

Cinch / Cinch: output Audio Stereo Line out

Cinch / Cinch: input Audio Stereo for CVBS / YUV

Cinch / Cinch: input Audio Stereo for PC

Cinch / Cinch: input Audio Stereo for Y/C (S—Video)

DVI—I: input PC Connection to DVI—/ VGA—Signalsource

IEC: input RF antenna signal terrestrical or cable

IEC: output RF with patch cable connected to:

IEC: input RF

D—Sub 9pol: input / output PC RS232 for Softwareupdate

3x Cinch: input Video YUV, combined with CVBS

Euro AV: input Video CVBS, RGB, Audio L/R

output Video CVBS, Audio L/R

Euro AV: input Video CVBS, Audio L/R

output Video CVBS, Audio L/R

Input signals in PC Mode

Horizontal frequency range: 30kHz ... 80kHz

Vertical frequency range: 50Hz ... 90Hz

Pixel Clock frequency: max. 140MHz RGB, max. 110MHz DVI

Signal level, nominal: 0,7Vp—p +/— 3dB bei 75 Ohm

Synchronisation: SoG, Composite Sync, H— und V—Sync, separated

Sync. polarity: positiv and negativ

Sync. level: TTL, Loeding >1kOhm +/— 10%, bei SoG 0,3Vp—p +/— 0,015V,

negativ

VESA DDC Standard: 2B

Jitter: <6% @ 140MHz

Input resistance: 75 Ohm +/— 10% (0 ... 200MHz)

Threshold timing determination: +/— 2% (horizontal, vertical)

Transit time between 2 Timings: < 5sec