Northern NS-622 User manual

Table of contents

Other Northern Measuring Instrument manuals

Popular Measuring Instrument manuals by other brands

Ambient Weather

Ambient Weather WS-3000 user manual

Keysight

Keysight Streamline Series Configuration guide

LaserLiner

LaserLiner BeamControl-Master BCM operating instructions

Samoa

Samoa 415000 Technical service guide

Konica Minolta

Konica Minolta CHROMA METER CS-200 brochure

Pfeuffer

Pfeuffer 8 operating instructions

Blue-White industries

Blue-White industries Sonic-Pro S6A Series operating manual

Kobold

Kobold DAH operating instructions

Bosch

Bosch GCL 2-15 G Professional Original instructions

Tecnosystemi

Tecnosystemi Toolsplit TSC200015 user manual

Ametek

Ametek 888 user manual

Emerson

Emerson Rosemount 3410 Series Maintenance and troubleshooting manual

ROOTECH

ROOTECH ACCURA 2500 user guide

Vanguard Instruments

Vanguard Instruments Auto-Ohm 10 user manual

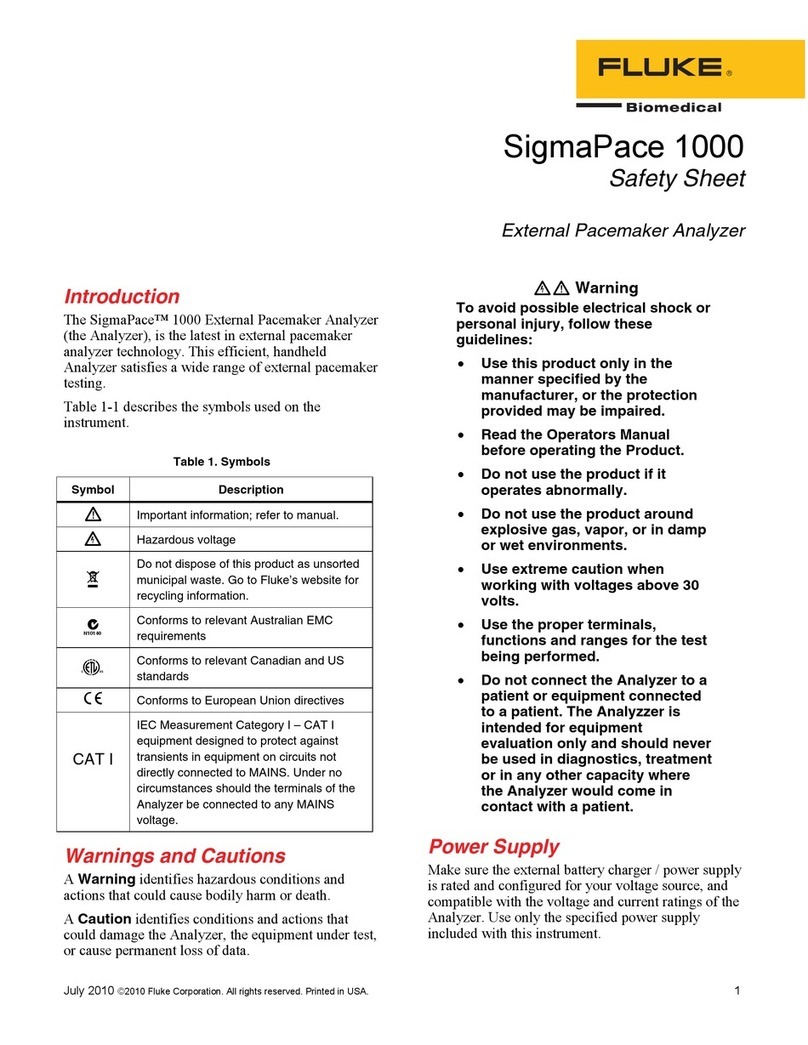

Fluke

Fluke SigmaPace 1000 Safety sheet

Regan Scientific Instruments

Regan Scientific Instruments BOT-3000E operating manual

Sper scientific

Sper scientific 850045 instruction manual

Leica Geosystems

Leica Geosystems DISTO A2 user guide