Feb 28, 2022 Page 3 of 78 Rev 2.8

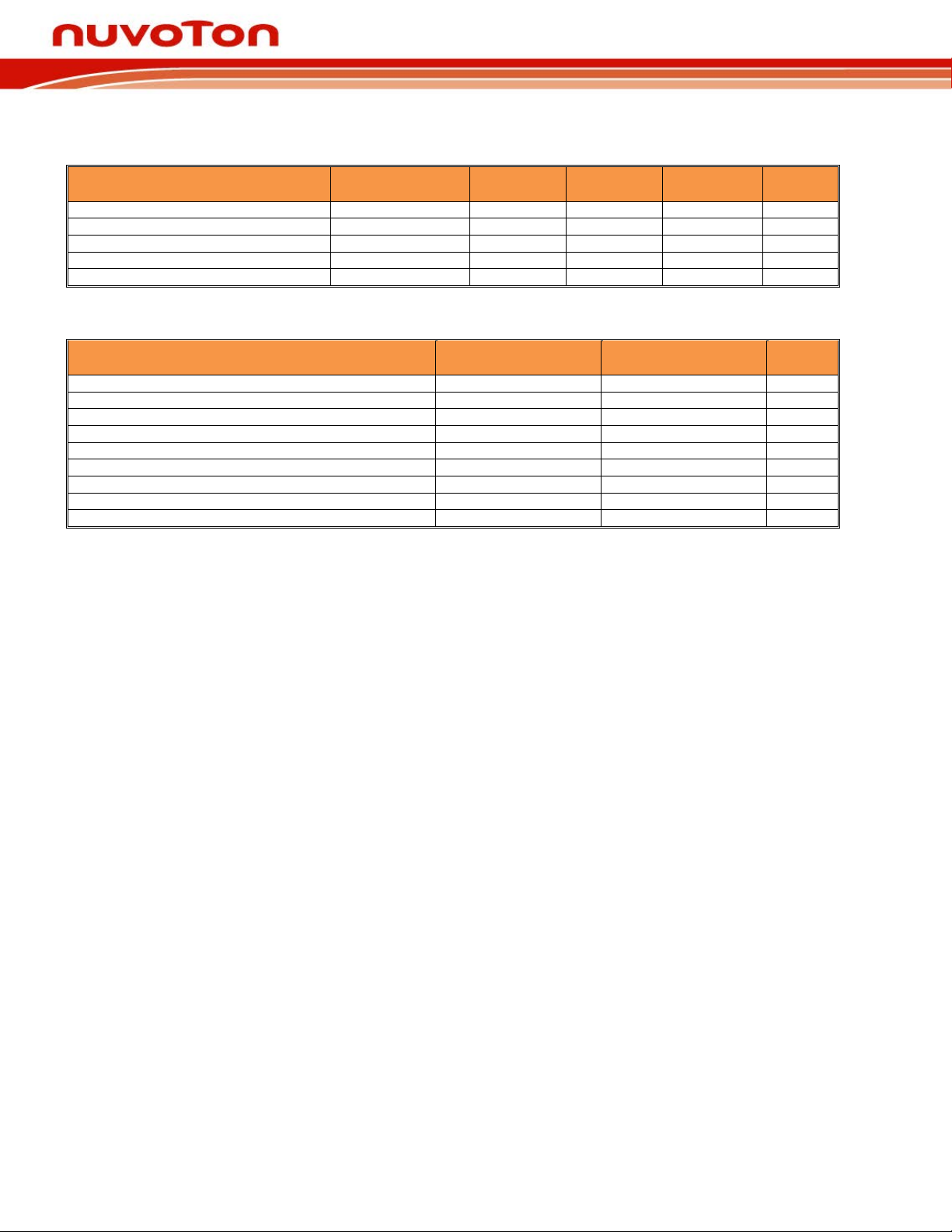

Table of Contents

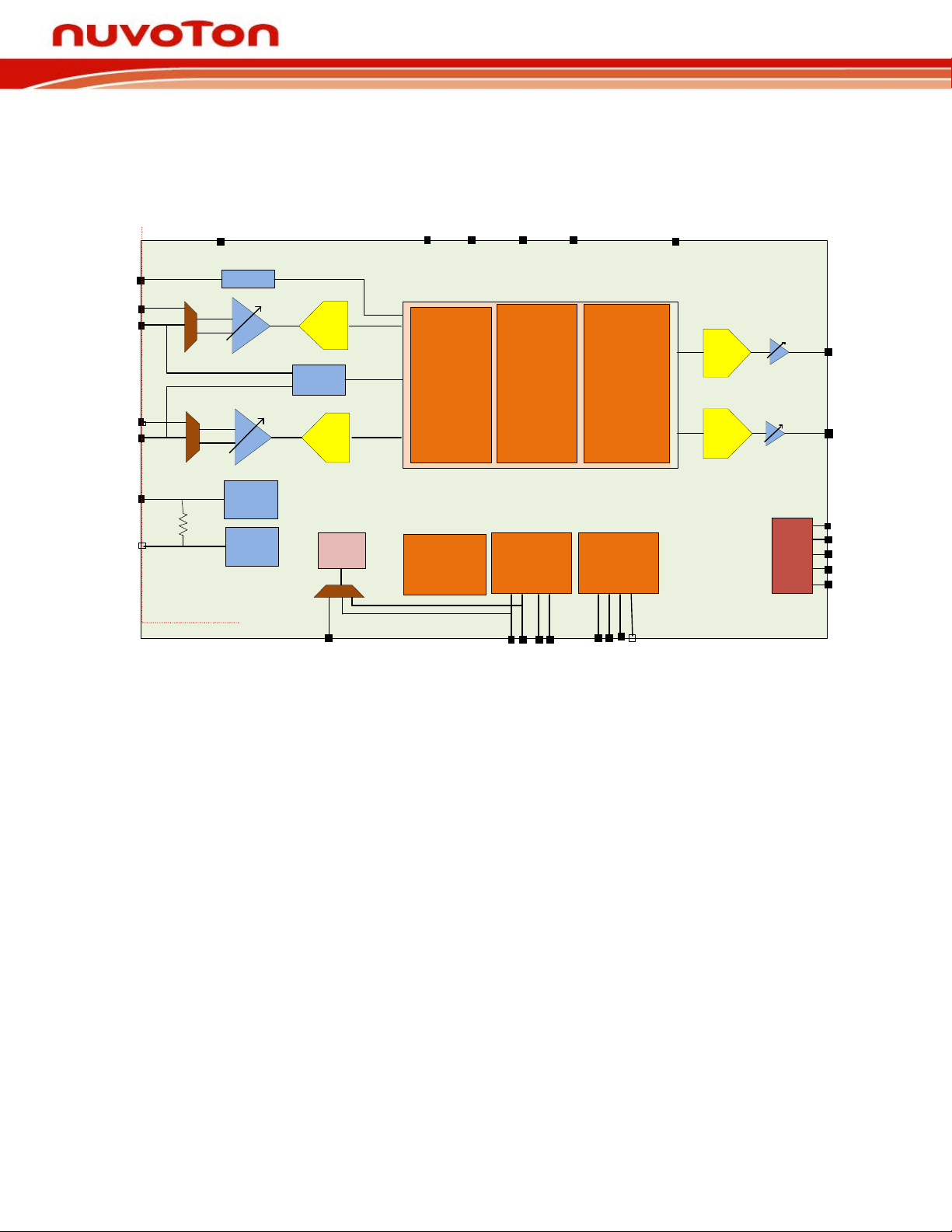

BLOCK DIAGRAM - QFN32...................................................................... 2

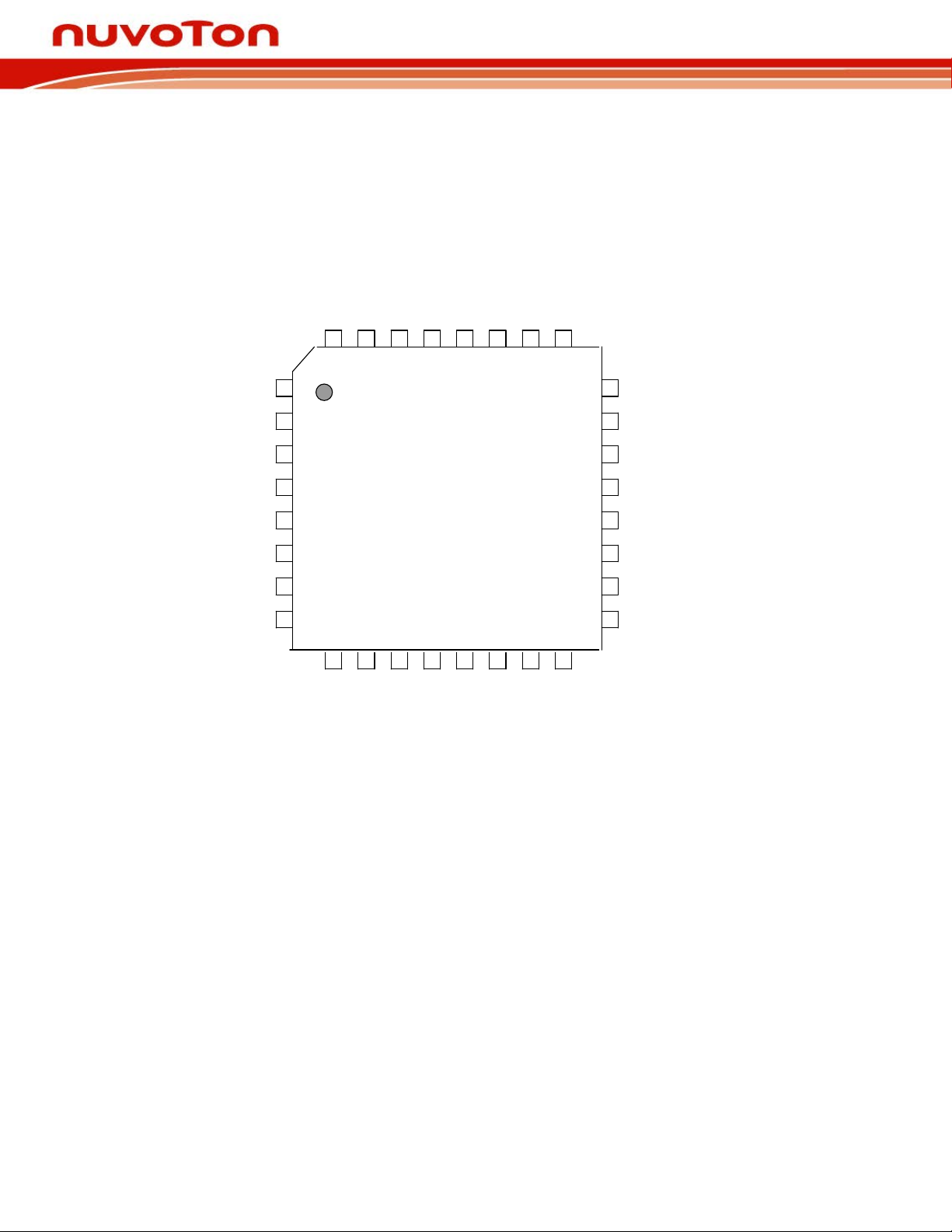

PIN DIAGRAM........................................................................................... 6

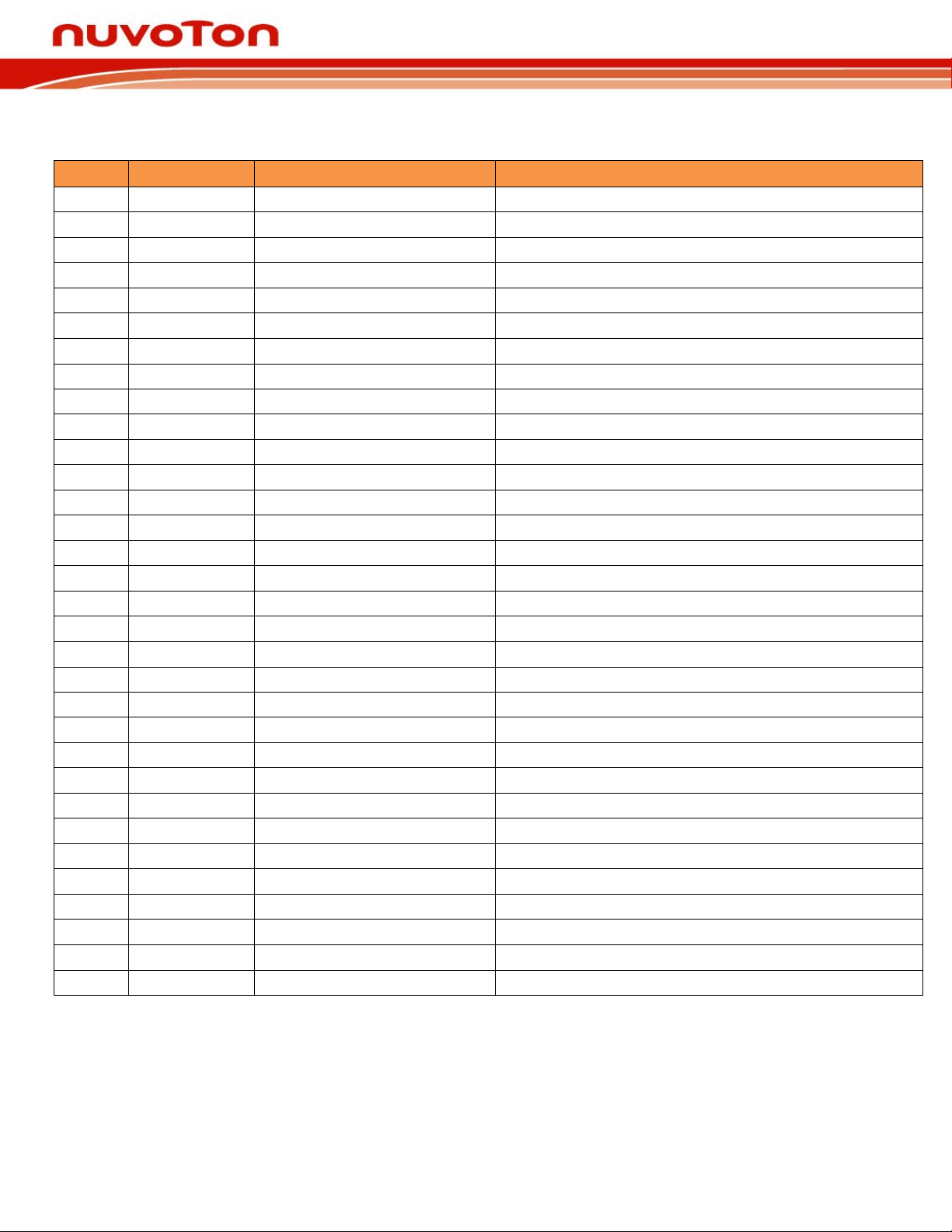

PIN DESCRIPTION.................................................................................... 7

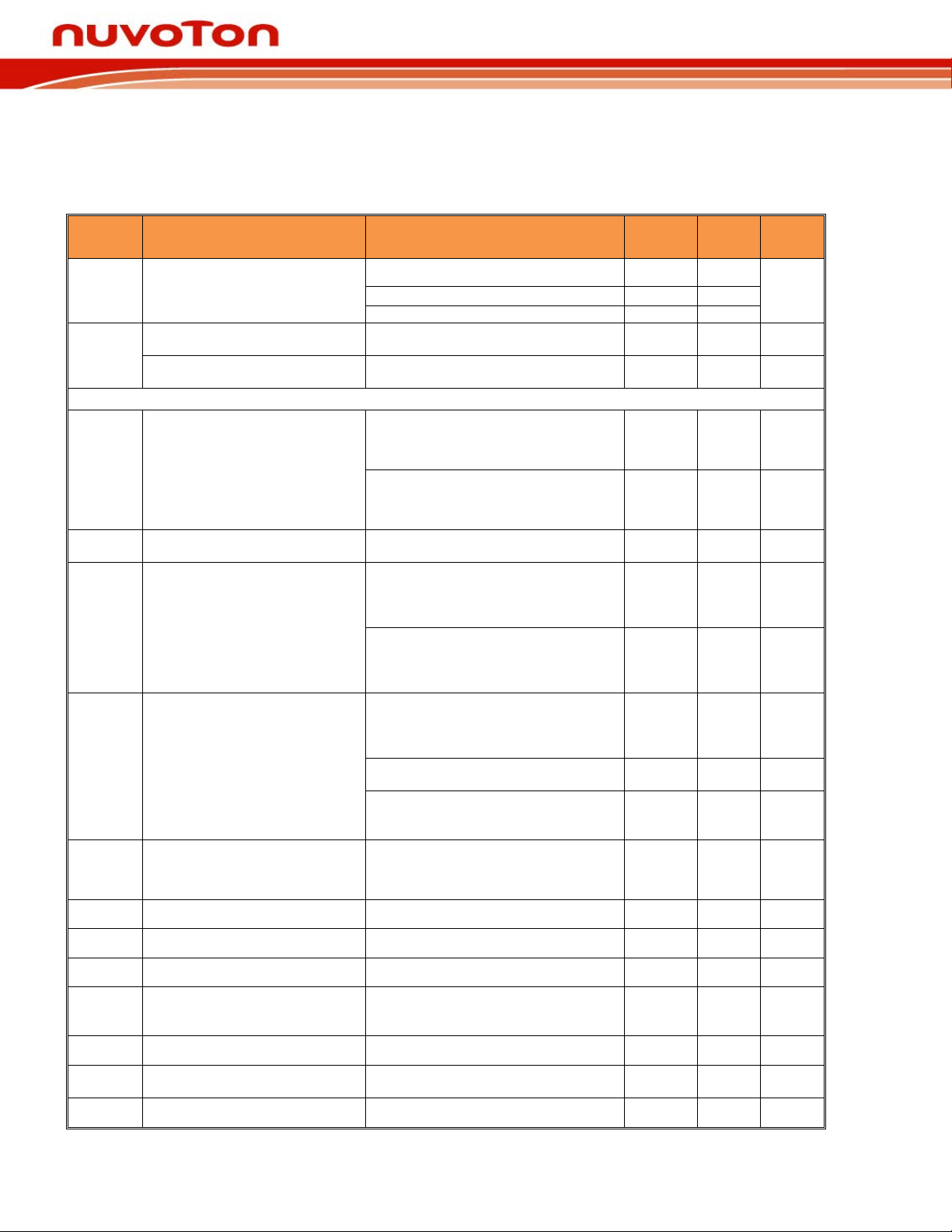

ELECTRICAL CHARACTERISTICS.......................................................... 8

1. GENERAL DESCRIPTION................................................................ 11

1.1 Inputs............................................................................................................... 11

1.2 Outputs............................................................................................................ 11

1.3 ADC, DAC and Digital Signal Processing........................................................ 11

1.4 Digital Interfaces.............................................................................................. 11

2. POWER SUPPLY ............................................................................. 12

2.1 Power on and off reset..................................................................................... 12

2.2 Power up and Start Sequence......................................................................... 12

3. INPUT PATH DETAILED DESCRIPTIONS....................................... 13

3.1 Analog Microphone Inputs............................................................................... 13

3.2 Digital Microphone Input.................................................................................. 14

3.3 VREF............................................................................................................... 14

3.4 MIC Bias.......................................................................................................... 15

3.5 MIC detect....................................................................................................... 15

3.5.1 Key Release .......................................................................................................................................17

4. ADC DIGITAL BLOCK...................................................................... 18

4.1 ADC Dynamic Range Compressors (DRC) ..................................................... 18

4.1.1 Level Estimation .................................................................................................................................18

4.1.2 Static Curve........................................................................................................................................18

4.1.3 Limitation ............................................................................................................................................20

4.2 ADC Digital Volume Control ............................................................................ 21

4.3 ADC Programmable Biquad Filter ................................................................... 21

4.4 Companding.................................................................................................... 22

4.5 Additional ADC Application Notes ................................................................... 22

5. DAC DIGITAL BLOCK...................................................................... 23

5.1 DAC Dynamic Range Control (DRC)............................................................... 23

5.1.1 Level Estimation .................................................................................................................................23

5.1.2 Static Curve........................................................................................................................................24

5.2 DAC Digital Volume Control, Mute and Channel selection.............................. 25

5.3 DAC Soft Mute................................................................................................. 25

5.4 DAC Auto Attenuate ........................................................................................ 25

5.5 DAC Path Digital Mixer with Side tone............................................................. 25