AN-39

B

7/06

6

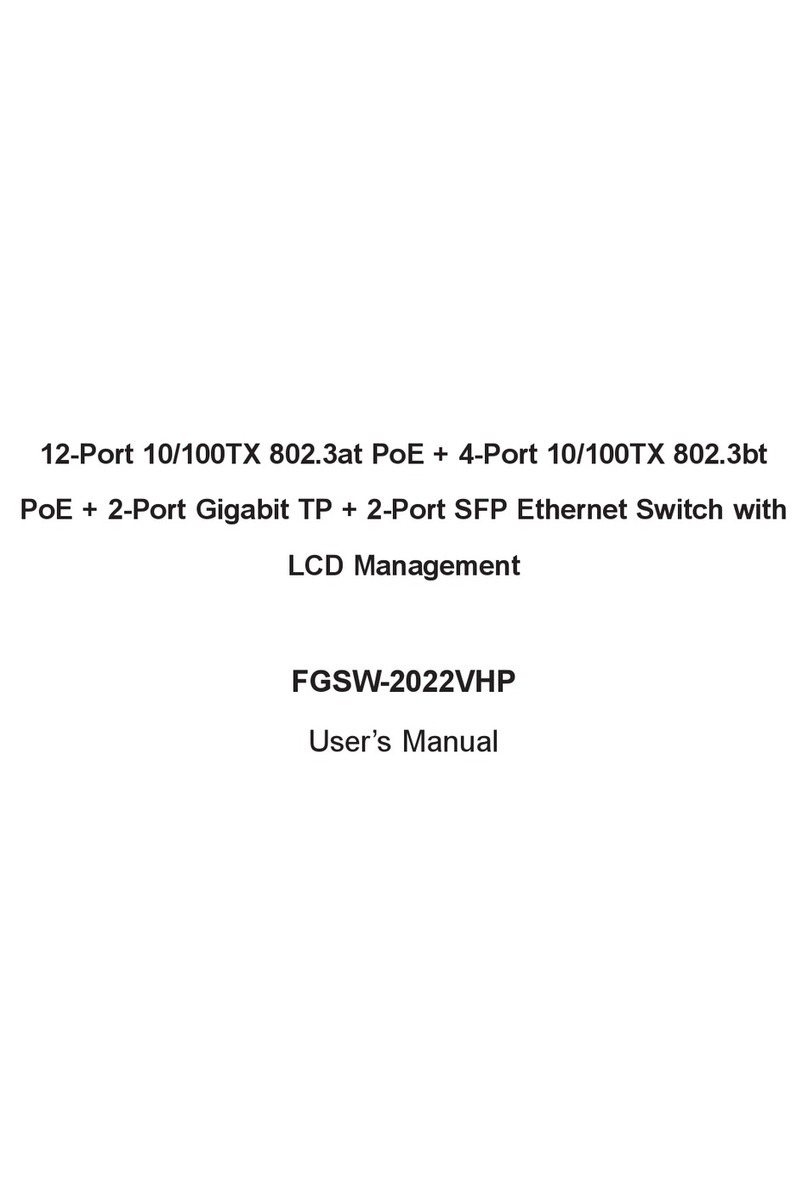

Figure 6. LinkSwitch-LP Variables Section of LinkSwitch-LP Design Spreadsheet.

performance and not the peak drain voltage that limits the use

of Clampless designs to < 2 W. However if a bias winding is

added which uses a slow diode (1N400x series) that peak in

EMI is reduced as the bias acts as a clamp, damping out the

leakage inductance ringing. This extends the power range for

Clampless designs to ≤2.5 W. In addition, the use of a small

Y-Capacitor (100 pF) can be beneficial in containing this problem

and making the EMI performance less variable.

For designs greater than 2.5 W, a Clampless solution is not

recommended.

The guidance above applies to universal input or 230 VAC only

designs. For 100/110 VAC only input designs it may be possible

to use Clampless designs above 2 - 2.5 W but only after verifying

acceptable peak drain voltage and EMI performance.

All the variables described above can be entered in the Enter

Application Variables section of the LinkSwitch-LP design

spreadsheet in the PI Xls design software (see Figure5).

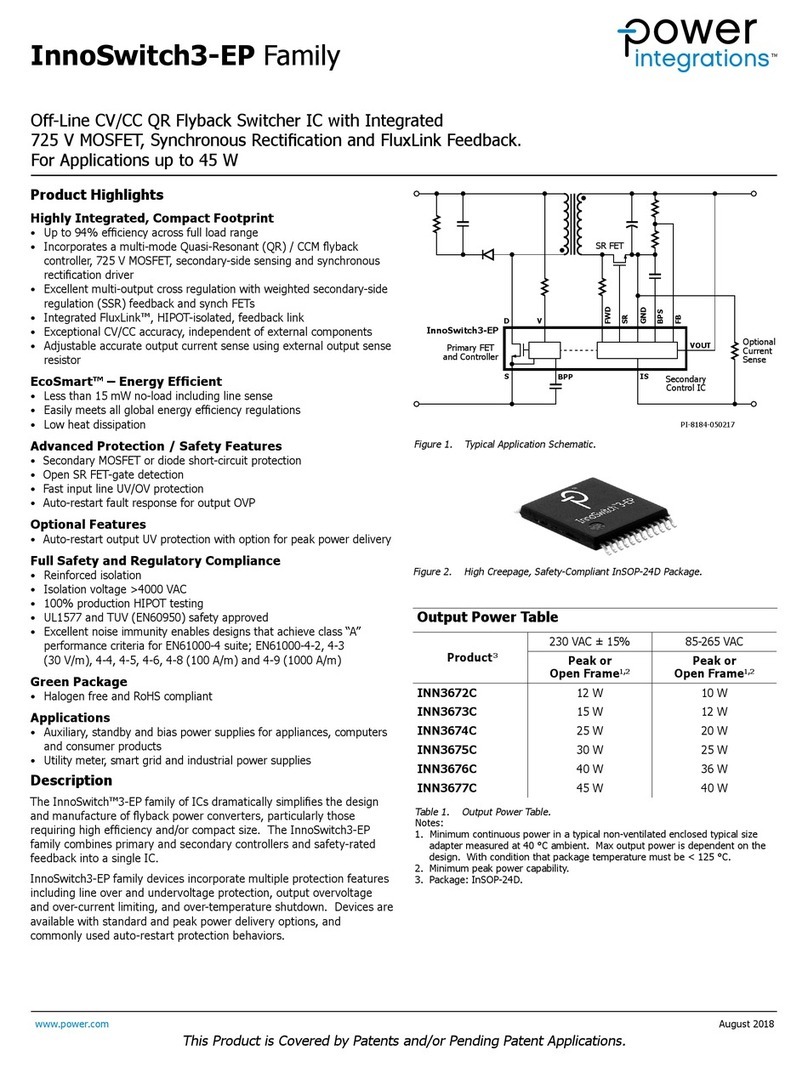

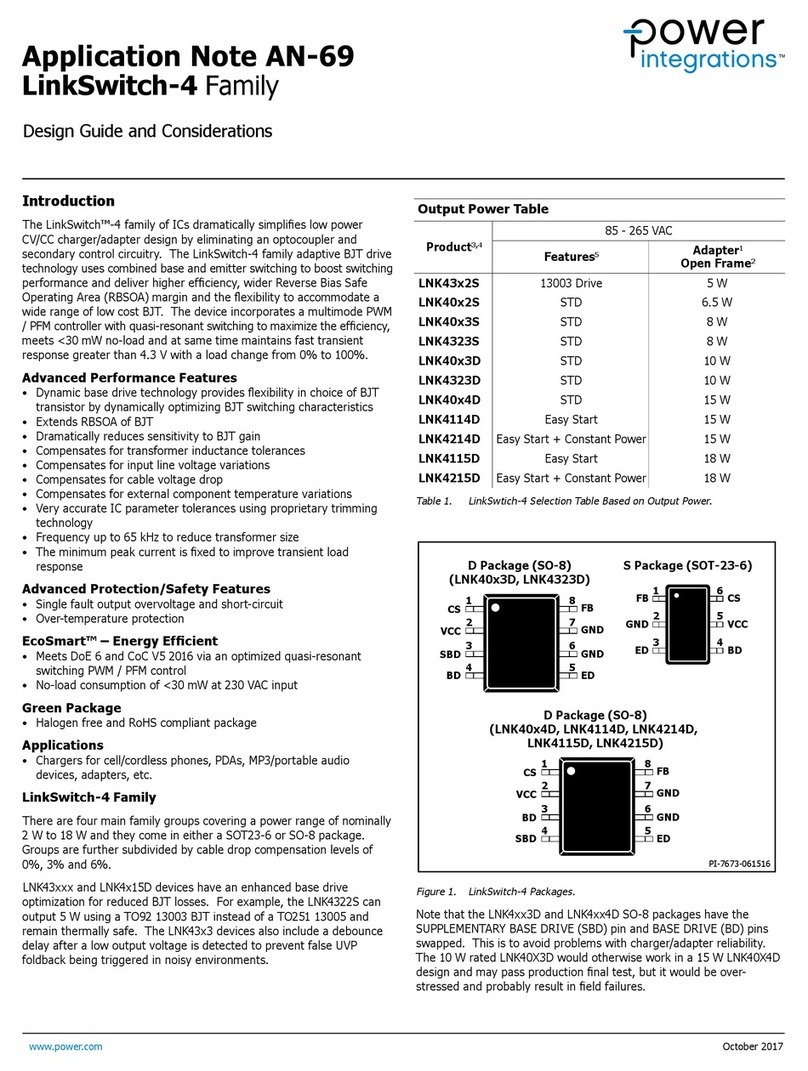

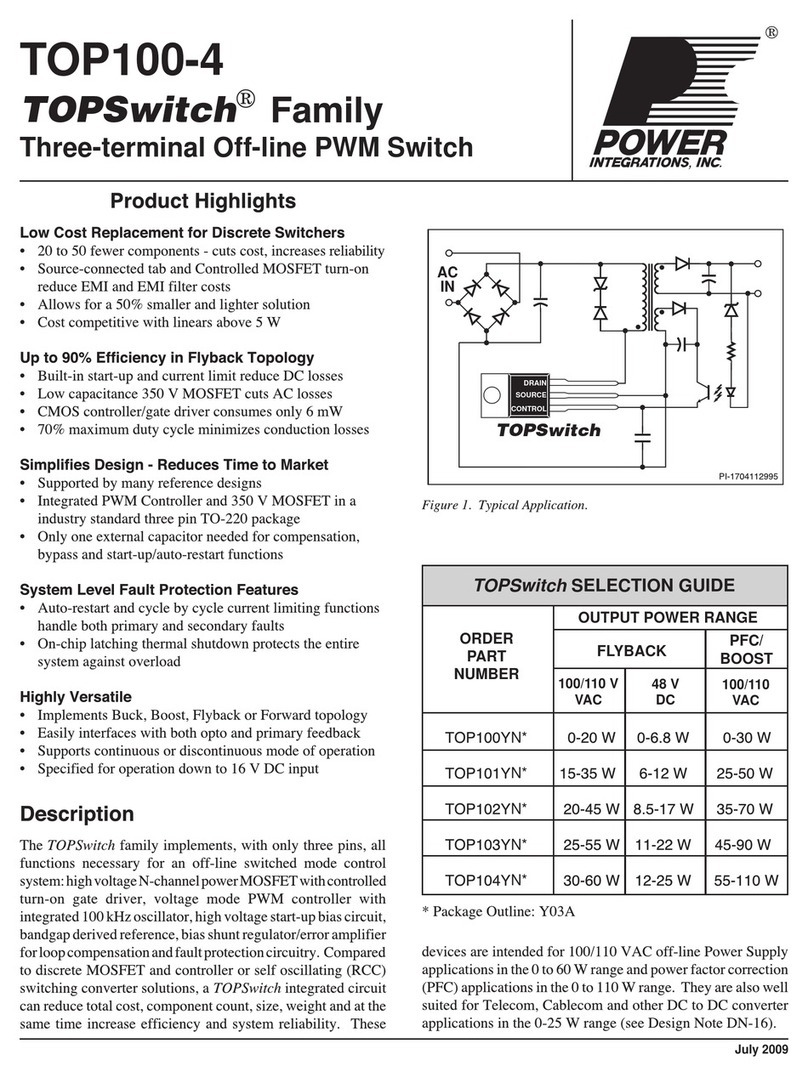

Step 2 – Enter LinkSwitch-LP, VOR, VDS, VD

Select the appropriate LinkSwitch-LP based on the input

voltage range and the corresponding maximum output power

(see Table 4 & 5).

Table 4. Maximum Output Power Capability of LinkSwitch-LP

Devices.

Power delivery from a given device also depends on the

transformer core size selected. Table 5 provides examples of

the output power possible from each device and 3 common

core sizes. These power numbers assume a flux density of

1500 Gauss, and can be increased for higher flux densities,

based on acceptable audible noise.

Reflected Output Voltage, VOR (V)

This parameter is the secondary winding voltage reflected

back to the primary through the turns ratio of the transformer

(during the off time of the LinkSwitch-LP). The default

value is 80 V, however this can be increased up to 120 V to

achieve the maximum power capability from the selected

LinkSwitch-LP device. In general, start with the default value of

80 V, increasing the value when necessary to maintain KP above

its lower limit of 0.9 at the minimum input voltage of 85 VAC.

For Clampless designs, there is less flexibility in selecting the

value of VOR. Increasing VOR directly increases the peak drain

voltage. Therefore for Clampless designs, a value of 80 V should

be used and only increased once the peak drain voltage has been

measured and adequate margin to BVDSS determined.

LinkSwitch-LP On-State DRAIN-to-SOURCE Voltage,

VDS (V)

This parameter is the average on-state voltage developed across

the DRAIN and SOURCE pins of LinkSwitch-LP. By default, if

the gray override cell is left empty, a value of 10 V is assumed.

Use the default value if no better data is available.

Output Diode Forward Voltage Drop, VD (V)

Enter the average forward voltage drop of the (main) output

diode. Use 0.5 V for a Schottky diode or 1 V for a PN diode

if no better data is available. By default, a value of 0.5 V is

assumed.

Calculated Ripple to Peak Current Ratio, KP

KP is a measure of the operating mode and primary current

waveshape of the design. KP < 1 indicates a continuous design

(the lower the KP

, the more continuous the design) and a

KP > 1 indicates a discontinuous design (the higher the KP

, the

more discontinuous the design).

Below a value of 1, indicating continuous conduction mode,

KP is the ratio of ripple to peak primary current (KRP). Above

a value of 1, indicating discontinuous conduction mode, KP is

the ratio of primary MOSFET off time to the secondary diode

conduction time (KDP). The value of KP should be in the range

of 0.9 < KP < 6 and guidance is given in the comments cell if

the value is outside this range.

Maximum Power (W)

Device Universal Input 230 VAC

LNK562 1.9 1.9

LNK563 2.5 2.5

LNK564 3 3

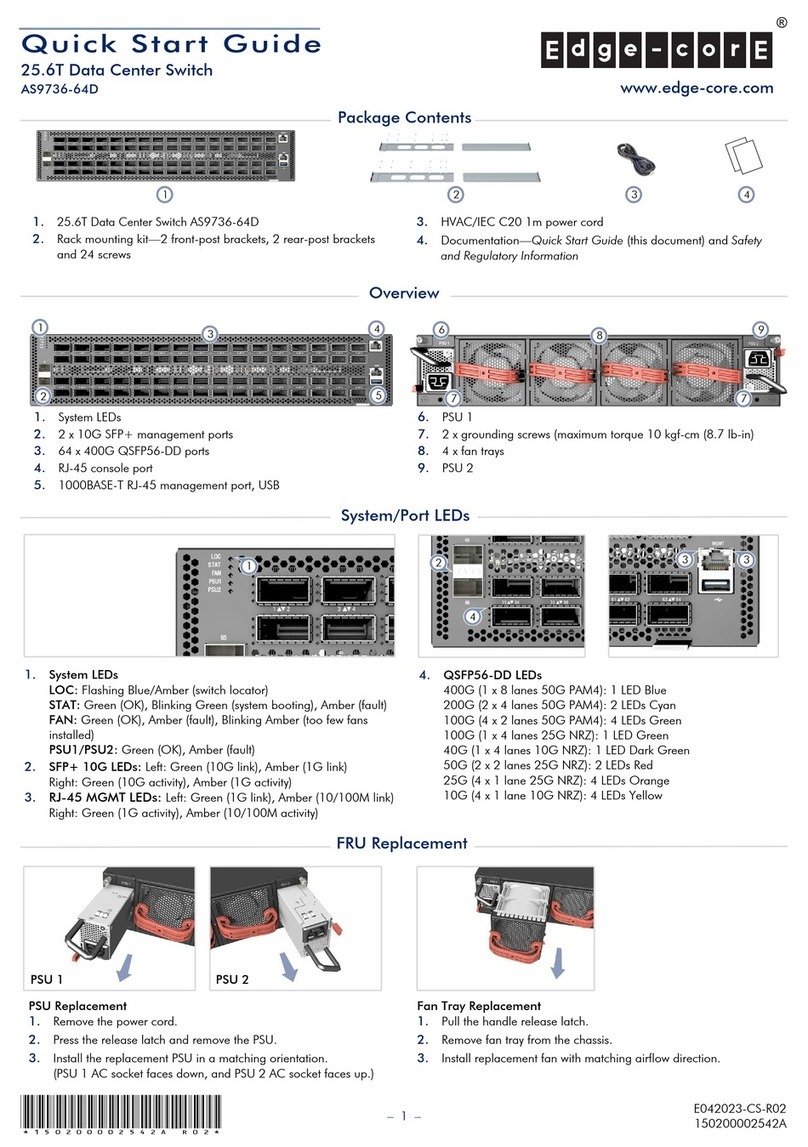

ENTER LinkSwitch-LP VARIABLES

LinkSwitch-LP LNK564 LinkSwitch-LP device

Chosen Device LNK564

ILIMITMIN 0.124 Amps

ILIMITMAX 0.146 Amps Maximum Current Limit

fSmin93000 Hertz Minimum Device Switching Frequency

I^2fMIN 1665 A^2Hz I^2f Minimum value (product of current limit squared and frequency is trimmed for tighter tolerance)

I^2fTYP 1850 A^2Hz I^2f typical value (product of current limit squared and frequency is trimmed for tighter tolerance)

VOR 80 Volts Reflected Output Voltage

VDS 10 Volts LinkSwitch-LP on-state Drain to Source Voltage

VD 0.5 Volts Output Winding Diode Forward Voltage Drop

KP 1.53 Ripple to Peak Current Ratio (0.9<KRP<1.0 : 1.0<KDP<6.0)