Rev. B 10/17

3

Application NoteAN-69

www.power.com

Quick Start

To start immediately, use the following information to quickly design

the transformer and select the components for a rst prototype.

Only the information described below needs to be entered into the

PIXls spreadsheet gray cells in column [B]. Some gray cells have

entries in bold font, these contain drop down selections. If an invalid

selection is made, then Info or Warning text will appear in column [C]

and [D], a description of the error is displayed in column [H]. Other

parameters and component values will be automatically calculated.

References to spreadsheet cell locations are provided in square

brackets [cell reference].

The default design presented in a blank spreadsheet is for a 5 V, 2 A

adapter with 6% cable compensation and standard universal AC input

voltage range. All gray cells are blank except for those with bold text

drop down selections, which are set to the appropriate selections for

the default adapter. The default values are displayed in column [E]

and [F]. When an entry is made in a column [B] gray cell, its value is

transferred into the corresponding cell in columns [E] and [F] and

from there, used in the calculations.

It is only necessary to enter values into column [B] if they are

different to the default values in column [E].

• If a non-standard AC input voltage range is required, enter the

values for VACMIN, VACMAX and fL into cells [B3, B4, B5] as required.

• Enter the nominal output voltage (at the end of the cable if

applicable), VO[B6].

• Entre the output diode forward volt drop if different to the

standard Schottky value, VD[B8].

• Enter the minimum required output current value, IO[B9]. Notice

that cell [E10] is updated with a suggested minimum CC value for

ICC. See Figure 4.

• Enter the required CC limit, ICC [B10], if it is higher than the

suggested minimum I [E10]. See Figure 4.

• Enter an efciency estimate, η [B12]. Use the target gure from

the applicable efciency standard.

• Use the drop down selection menu in [B19] to select the desired

cable compensation. Output voltage at the PCB, VO_PCB, is now

given in [E7].

• The minimum recommended bulk capacitance value (CIN1 + CIN2) is

given in [E13]. If a larger value, or standard values are to be used,

enter their total value into [B13].

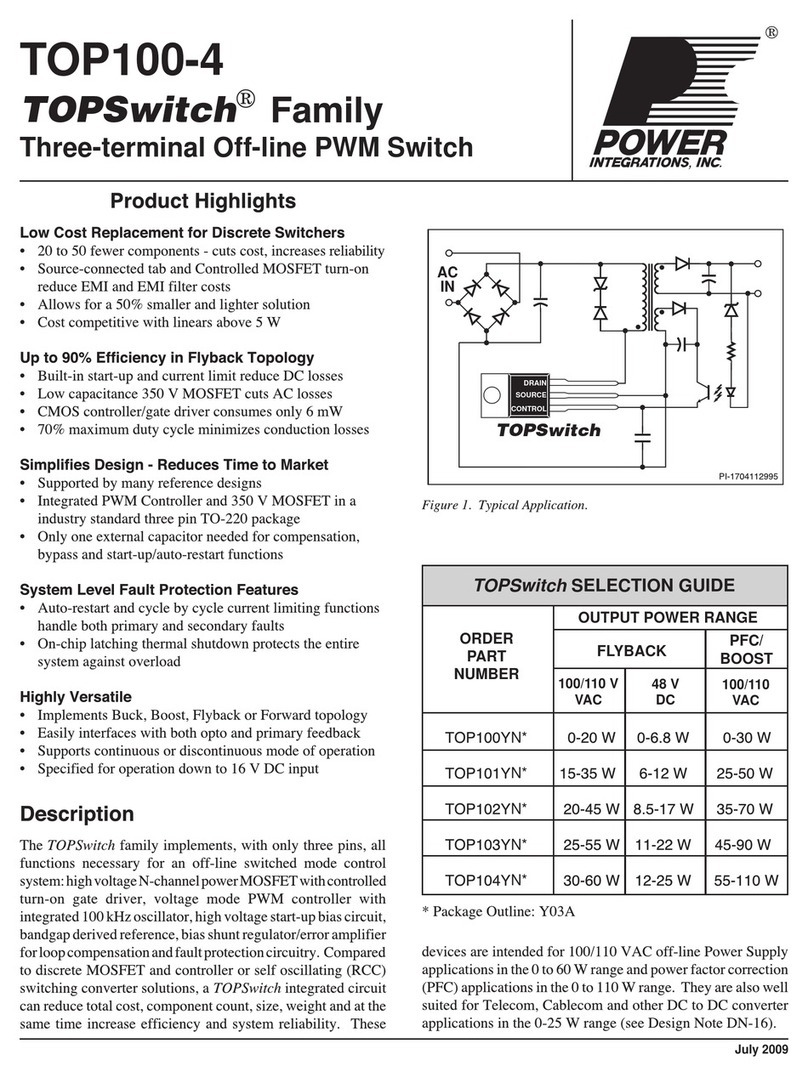

• Using the value for ‘rated output power’ in cell [E11], use table 1

on page 1, to choose the correct LinkSwitch-4 device. Use the

drop down selection menu in [B18] to select that device.

• BJT types TS13003 and TS13005 are auto selected based on

output power. To use a different BJT, enter PART_NUMBER, HFE_

STARTUP (low current gain), HFE (high current gain) and VSWMAX

(VCBO) into [B24,B25,B26,B27].

• Use the drop down selection menu in [B35] to select ‘AUTO’. A

suitable core, bobbin and parameters will automatically be entered

into cells [E35 – E43].

• To optimize for efciency enter an alternative value for the

reected output voltage, VOR in [B49], the default is 100 V. While

trying different values, observe the changes in KCRMV [E65] and

aim to get between 0.95 and 0.98. At the same time ensure

VCRMV-VMIN [E56-E57] is less than 15 V, but the higher VCRMV

the better. The spreadsheet will produce a reasonable solution if

VOR is left at the default 100 V.

• Fixing the number of secondary turns in [B50] while sweeping the

VOR value [B49] offers further optimization possibilities.

• The default primary inductance tolerance is 10%, an alternative

value can be entered in [B88]. Tighter tolerance allows better

average efciency across production.

• The default number of primary winding layers is 3 [E98], if the

primary current density [E103] is less than 3.8 Amps / mm2it can

be reduced to 2 by an entry into [B98]. If greater than 10 Amps /

mm2, increase to 4 etc. The fewer layers the better for leakage

inductance and hence efciency.

• The default calculated number of turns for the bias winding, NB

[E105] is based on providing a no-load bias voltage, VB_NOLOAD

[E107] that achieves the lowest no-load power. However, start-up

may be compromised so enter a value between 8 and 9 into

VB_NOLOAD [B107]. NB will be recalculated; check the value of

VB_NOLOAD_MEASURED [E109] is between 8 and 9 V. If not,

adjust the value in [B107] and recheck.

• One secondary layer is optimal for efciency, but if the output

voltage is high resulting in the secondary wire being impractically

thin, DIAS [E120], then it can be increased by entering a value in

LS [B116]. The spreadsheet calculates for a triple insulated wire

size that will ll the bobbin width in an integer number of layers

given in [E116].

• For low voltage designs, particularly at higher powers and larger

cores, the wire thickness becomes impracticably thick to wind. By

winding the secondary with a number of parallel conductors, the

wire thickness is reduced to a practical value, also leakage

inductance is decreased which improves efciency. To use more

than one conductor, enter a value into Filars [B117] and recheck

the new calculated wire size, DIAS [E120].

• Enter a BJT voltage derating factor into SWITCH_DERATING

[B126] if other than 0.10 (10%) is required.

• Use the drop down selection menu in VCS_MIN [B135] to set the

minimum value of peak primary current at no-load. It is repre-

sented by the peak mV across RCS. For the LNK40X2S devices, only

88 mV should be selected and a 1 kW value be used for RCS2 for

ltering. For other devices select the lowest value (56 mV) for the

rst iteration.

• If the application requires no-load to partial or full load transient

capability, where the output voltage must not fall below a minimum

value as in USB charger applications, check the value of CBIAS

[E138] if it is more than 2 mF, enter the value ‘2’ into [B138].

Check DELTA_BIAS [E139] is less than 1.6 V.

• Output capacitor calculation for starting up into a resistive load:

Use the drop down selection menu in LOAD_TYPE [B141] to select

‘Resistive Load’. The spreadsheet calculates the maximum value of

output capacitance the circuit will start up into i.e. before CBIAS

runs out of charge.

• For a CC load at start-up, use [B141] to select ‘CCLoad’. The

default start-up CC load current is 75% of IO, the rated output

current (not the CC limited value) if another value is specied,

enter it into ICC_STARTUP [B142].

• If the suggested output capacitance value needs to be rounded up

to a preferred value, enter this into COUT_FINAL [B145].