8

J-Link / J-Trace User Guide © 2004 - 2007 SEGGER Microcontroller GmbH & Co. KG

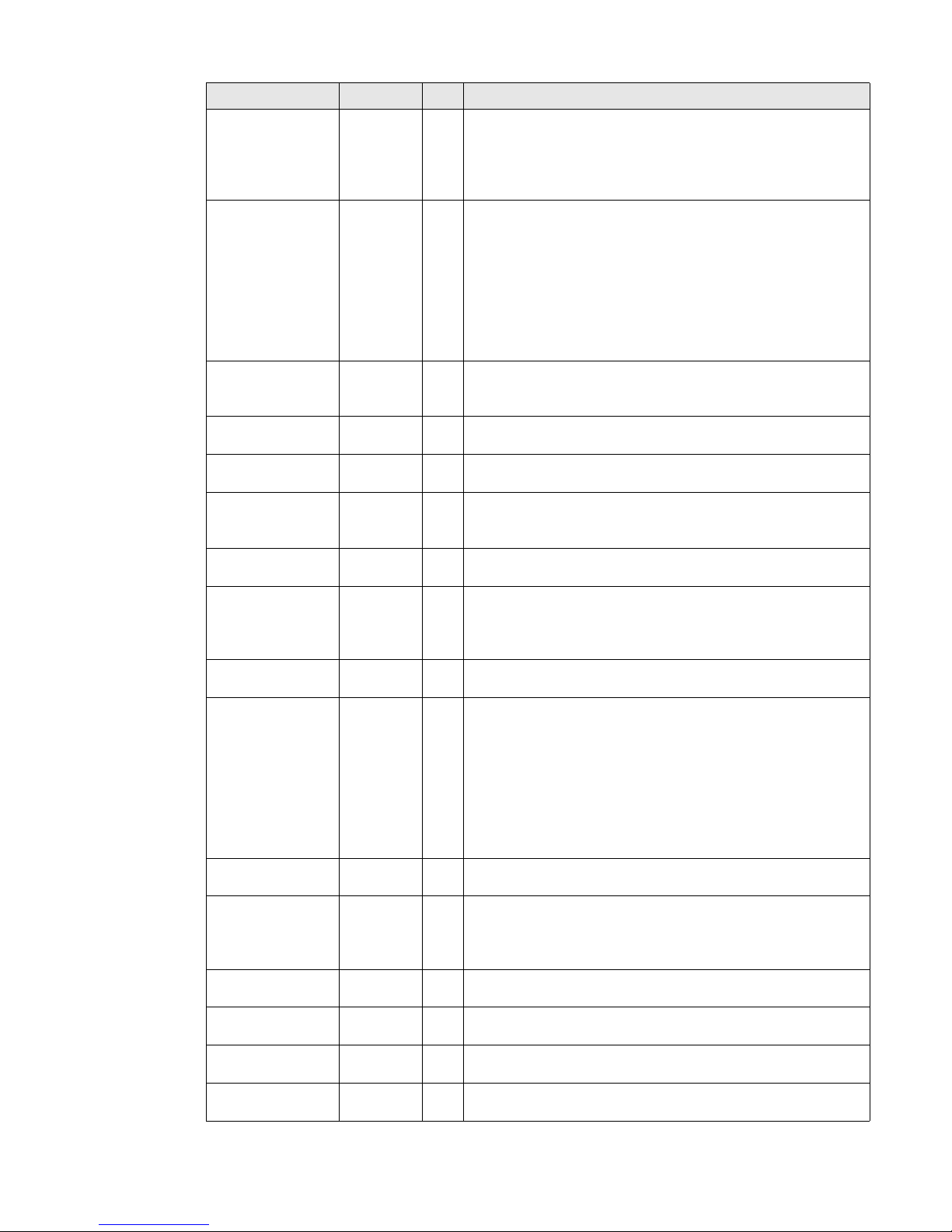

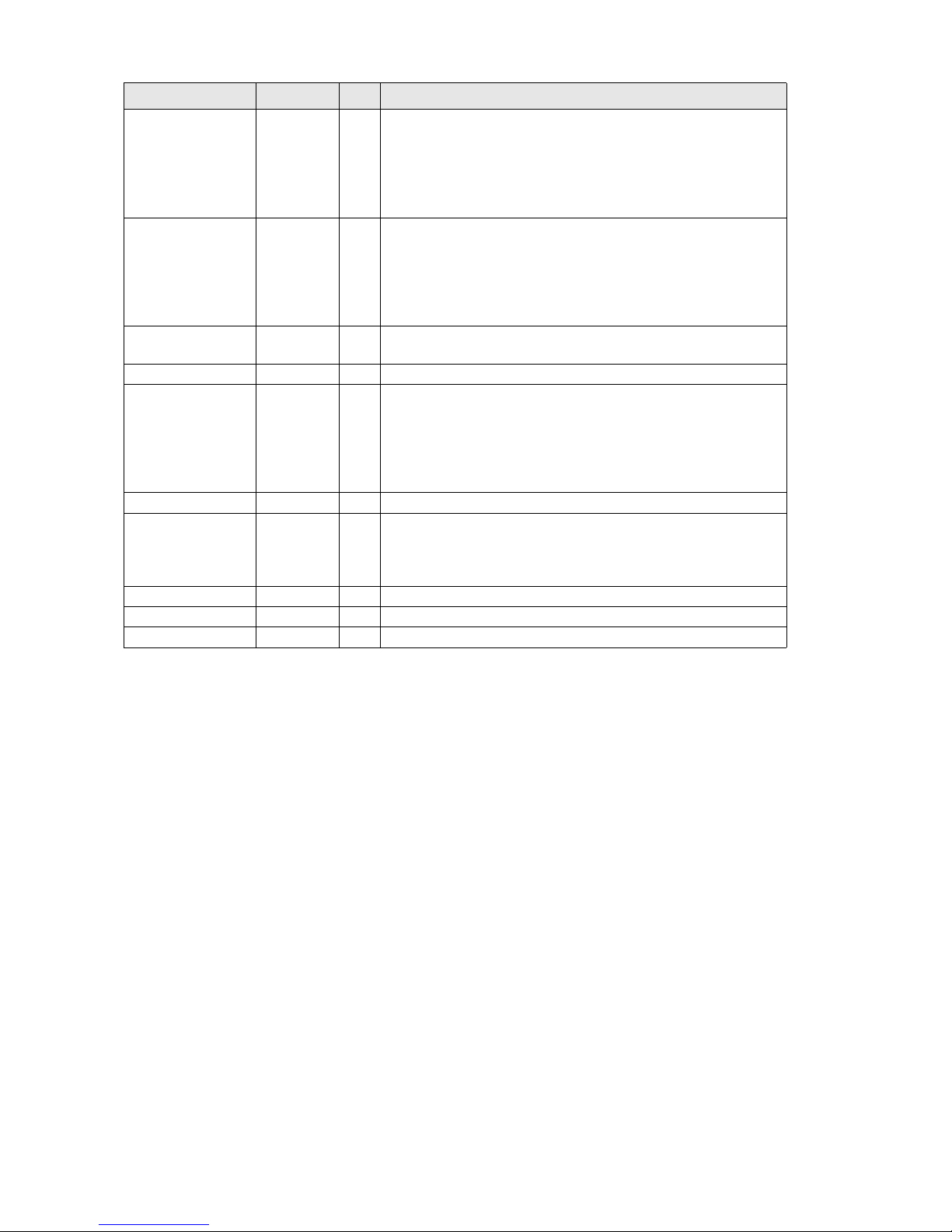

3.4.4 Determining which DLL is used by a program.............................................. 43

4 Working with J-Link and J-Trace....................................................................................45

4.1 Supported ARM Cores .............................................................................. 46

4.2 Reset strategies ...................................................................................... 47

4.2.1 Reset strategies in detail .......................................................................... 47

4.3 Cache handling ....................................................................................... 49

4.3.1 Cache coherency..................................................................................... 49

4.3.2 Cache clean area..................................................................................... 49

4.3.3 Cache handling of ARM7 cores .................................................................. 49

4.3.4 Cache handling of ARM9 cores .................................................................. 49

4.4 Connecting multiple J-Links / J-Traces to your PC ........................................ 50

4.4.1 How does it work? ................................................................................... 50

4.4.2 Configuring multiple J-Links / J-Traces ....................................................... 51

4.4.3 Connecting to a J-Link / J-Trace with non default USB-Address...................... 52

4.5 Multi-core debugging ............................................................................... 53

4.5.1 How multi-core debugging works............................................................... 53

4.5.2 Using multi-core debugging in detail .......................................................... 54

4.5.3 Things you should be aware of .................................................................. 56

4.6 Multiple devices in the scan chain.............................................................. 57

4.6.1 Configuration.......................................................................................... 57

4.7 Using DCC for memory access .................................................................. 58

4.7.1 What is required ? ................................................................................... 58

4.7.2 Target DCC handler ................................................................................. 58

4.7.3 Target DCC abort handler......................................................................... 58

4.7.4 Testing DCC memory access ..................................................................... 59

4.8 Command strings .................................................................................... 60

4.8.1 List of available commands....................................................................... 60

4.8.2 Using command strings............................................................................ 64

4.9 Switching off CPU clock during debug......................................................... 66

5 Device specifics.............................................................................................................67

5.1 Analog Devices ....................................................................................... 68

5.1.1 ADuC7xxx .............................................................................................. 68

5.2 ATMEL ................................................................................................... 69

5.2.1 AT91SAM7 ............................................................................................. 69

5.2.2 AT91SAM9 ............................................................................................. 69

5.3 NXP....................................................................................................... 70

5.3.1 LPC ....................................................................................................... 70

5.4 ST Microelectronics.................................................................................. 71

5.4.1 STR 71x................................................................................................. 71

5.4.2 STR 73x................................................................................................. 71

5.4.3 STR 75x................................................................................................. 71

5.4.4 STR91x.................................................................................................. 71

5.4.5 STM32 ................................................................................................... 71

5.5 Texas Instruments .................................................................................. 71

5.5.1 TMS470 ................................................................................................. 71

6 Hardware .......................................................................................................................73

6.1 JTAG Connector ...................................................................................... 74

6.1.1 Pinout.................................................................................................... 74

6.1.2 Target board design for JTAG.................................................................... 75

6.2 Using the JTAG connector with SWD .......................................................... 76

6.2.1 Pin Out .................................................................................................. 76

6.3 JTAG+Trace connector ............................................................................. 77

6.3.1 Connecting the target board ..................................................................... 77

6.3.2 Pinout.................................................................................................... 78

6.3.3 Assignment of trace information pins between ETM architecture versions ........ 79

6.3.4 Trace signals .......................................................................................... 79

6.4 RESET, nTRST ........................................................................................ 81