INTRODUCTION TO CPU INSTRUCTIONS

INSTRUCTION FORMAT

1·1

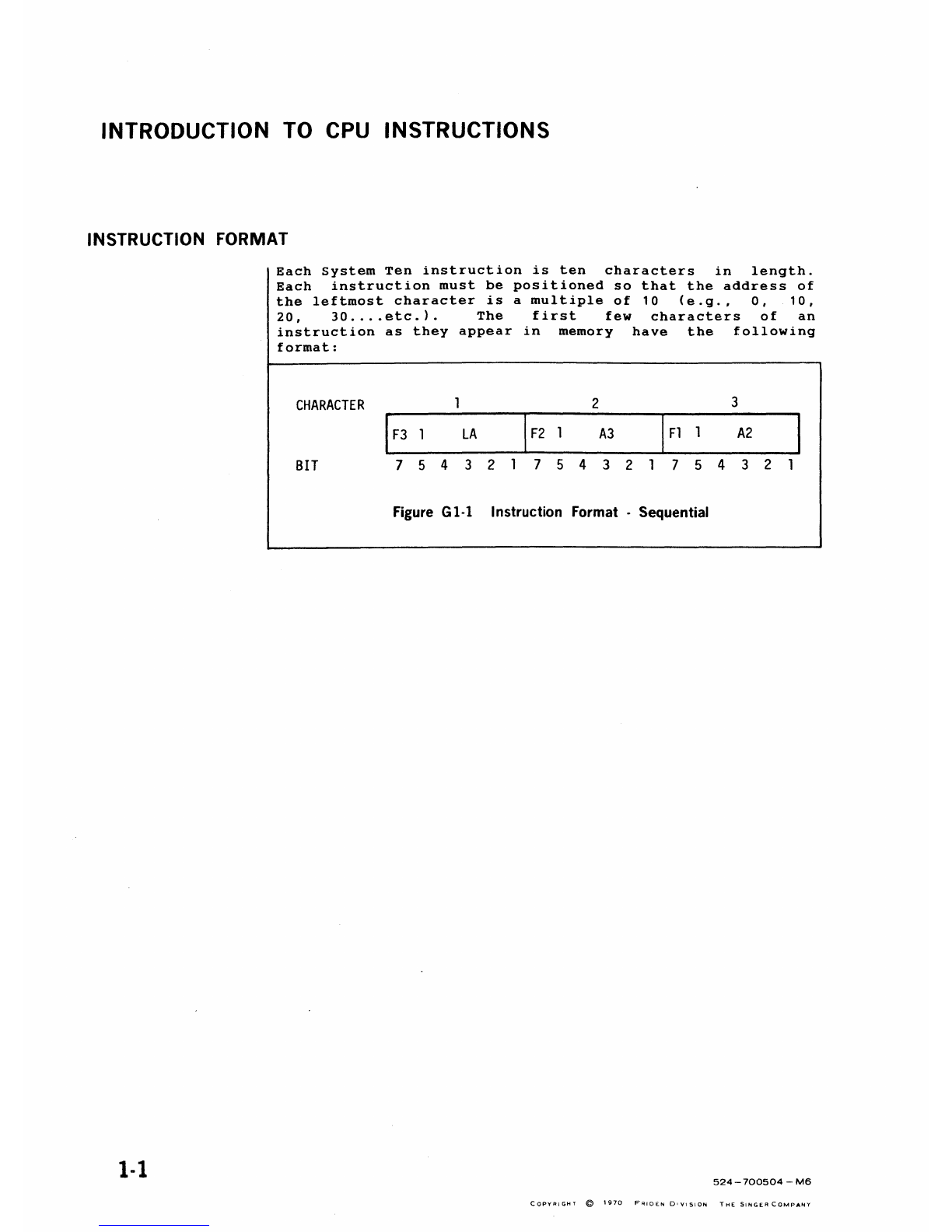

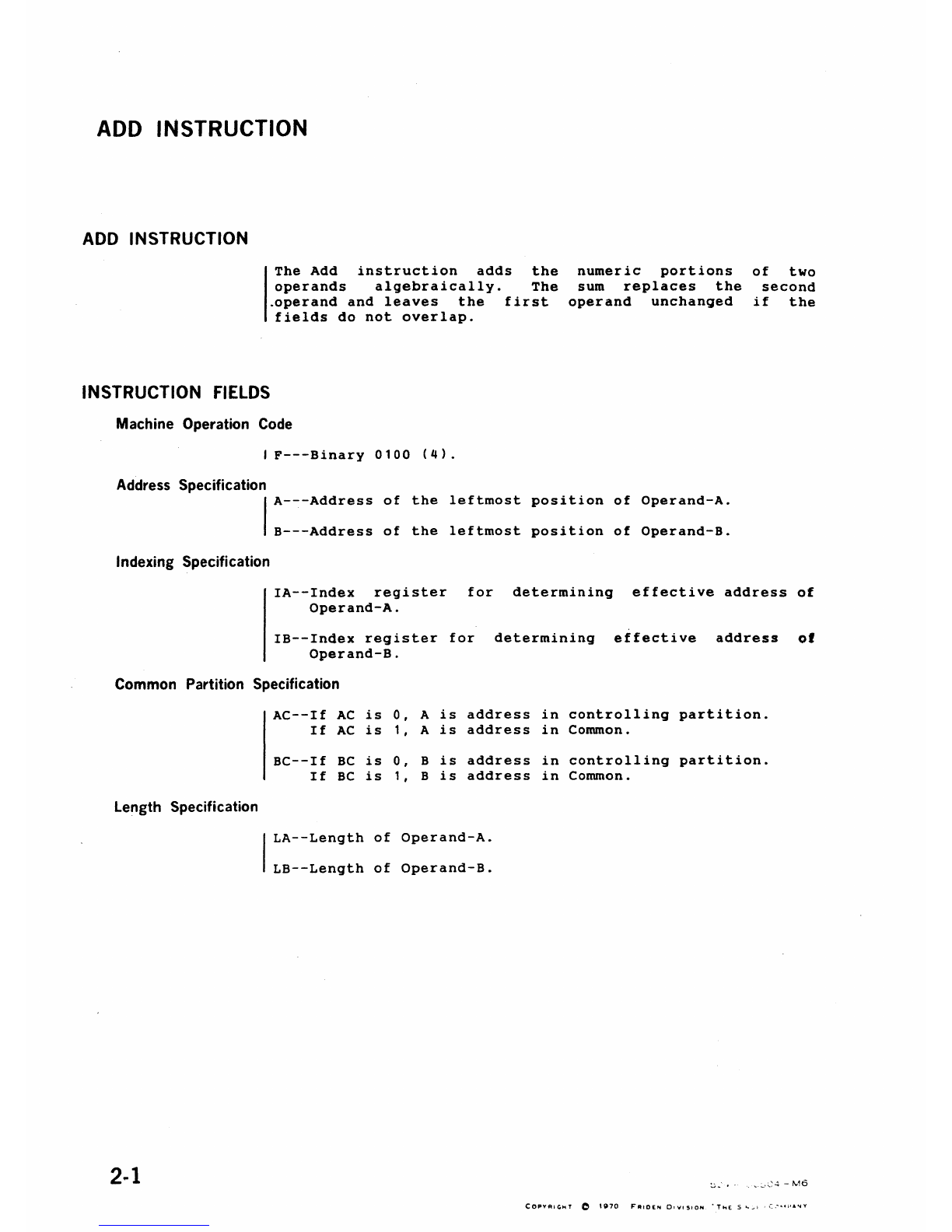

Each

system

Ten

instruction

is

ten

characters

in

length.

Each

instruction

must

be

positioned

so

that

the

address

of

the

leftmost

character

is

a

multiple

of

10

(e.g.,

0,

10,

20,

30

....

etc.).

The

first

few

characters

of

an

instruction

as

they

appear

in

memory

have

the

following

format:

CHARACTER

2 3

[F3

LA

I

F2

A3

IFl

A2

BIT

7 5 4 3 2 1 7 5 4 3 2 7 5 4 3 2

Figure

Gl·l

Instruction Format . Sequential

524

-

700504

-

M6

COPYRIGHT

©

1970

FRIDEN

O'VISIDN

THE

SINGER

COMPANY