–5 –

3

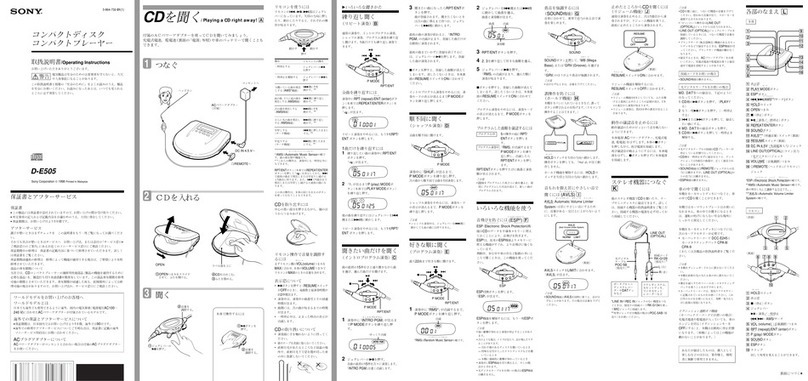

. Insert a VIDEO CD.

1Slide OPEN to open the lid. 2Fit the VIDEO CD to the pivot and

close the lid.

OPEN switch

Label side up

4

. Play a VIDEO CD.

1Press uon the main unit or the wireless remote control.

2Adjust the volume on the equipment connected to this player. (You cannot adjust the

volume on this player except for the signals output from the i/REMOTE jack).

To stop playing, press x.

The player also turn off.

u

VOLUME +/–

u

Do this

Press u.

Press x/CHG (x).

Press u

Press >repeatedly until you find the scene or track.

Press .repeatedly unitl you find the scene or track.

Press the number button of the track (wireless remote

control only).

Press .or >and hold it down until mor M

appears on the TV screen.

To

Pause

Stop

Resume play after pause

Locate the next or succeeding tracks

Locate the current or preceding tracks

Locate a specific track directly

Locate a point in the track while monitoring

the picture*

* To return to normal playback, press u.

The above operations can also be done with the buttons on the supplied earphones with remote

control or wireless remote control.

About the display

•No indication appears on the display while you operate the unit with the wired remote control.

•During play, the track number and the elapsed playing time of the current track appear.

•During pause, the elapsed playing time flashes.

If the volume level does not increase (when listening with the

headphones/earphone)

Is AVLS set to “LIMIT”? Set AVLS to “NORM.”For details, see “To protect your hearing

(AVLS)”on page 24.

If a cable is connected to the AUDIO OUT jack, you cannot adjust the volume. In such a case,

disconnect the cable.

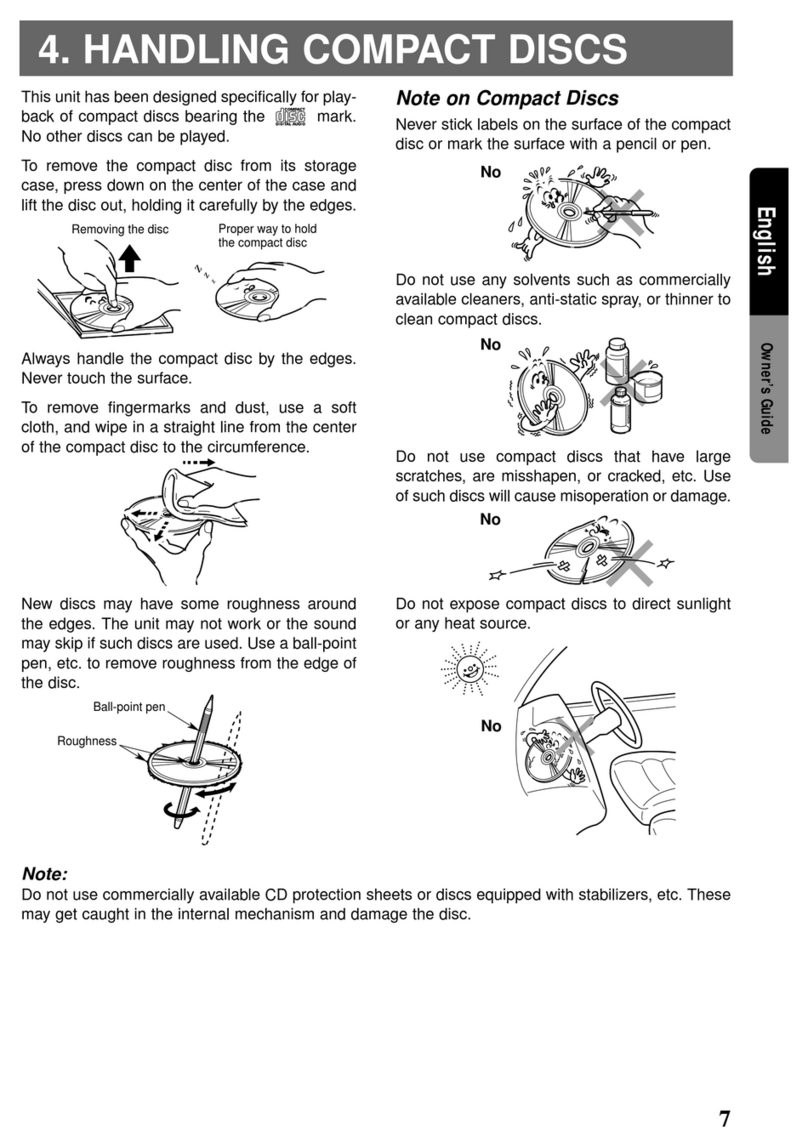

Removing the VIDEO CD

Remove theVIDEO CD as illustrated.

Dent

Playing an audio CD

You can also use rechargeable batteries, alkaline batteries and a car battery. (See “Connecting a

power source”on pages 28 - 30.)

1

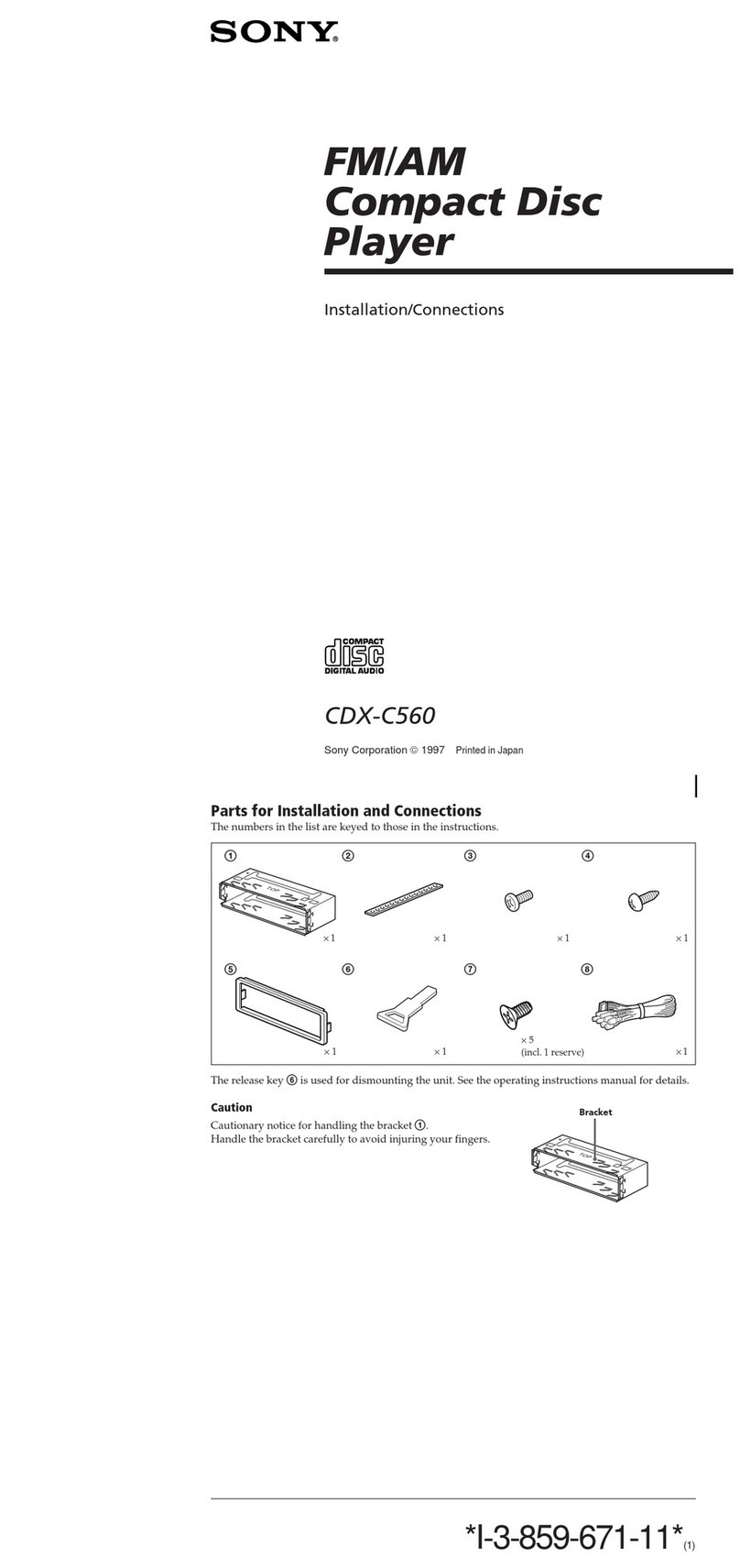

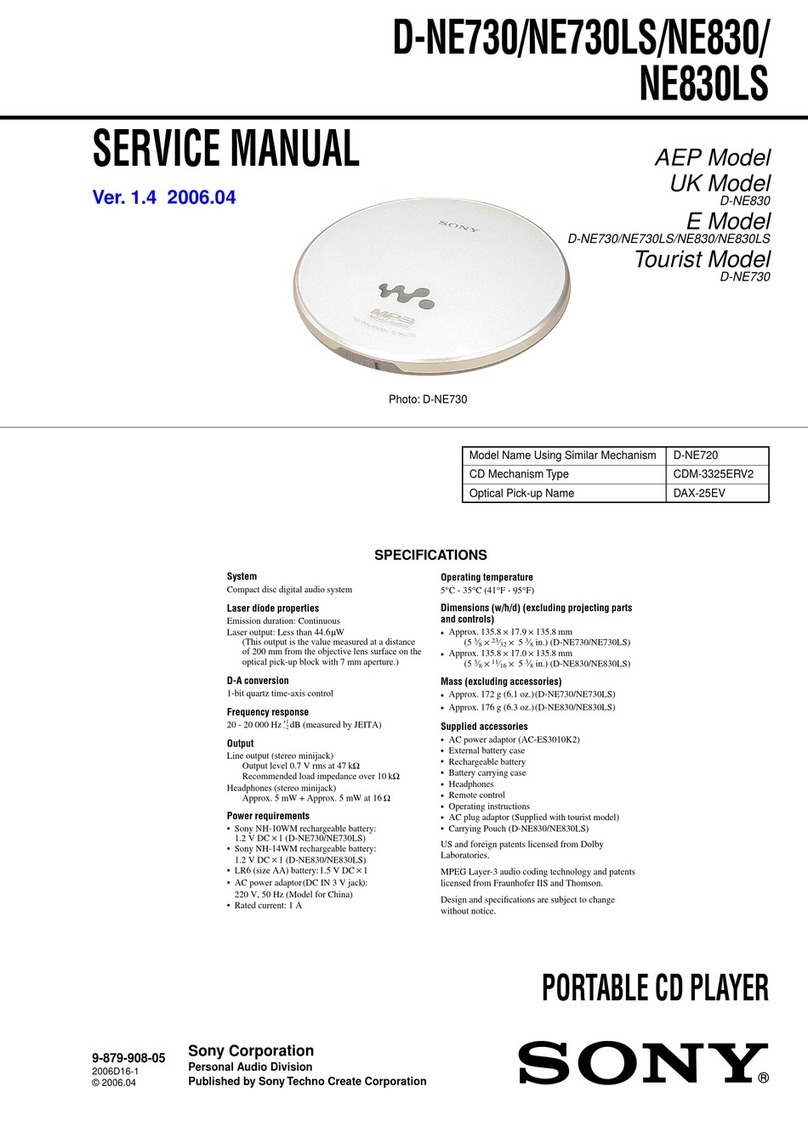

. Connect your CD player.

1Connect the AC power adaptor.

2Connect the earphones with remote

control.

Connect the earphones firmly. A

loose connection may cause noise

during playback.

to DC IN

4.5V

AC power

adaptor

to an AC outlet

to i/REMOTE

2

. Insert an audio CD.

1Slide OPEN to open the lid.

OPEN switch

Label side up

2Fit the audio CD to the pivot and

close the lid.

3

. Play an audio CD.

1Press u on the main unit or press

the jog lever on the remote control

toward u.

2Adjust the volume by pressing

VOLUME + or –.

To stop playing, press x.

The player is also turned off.

u

VOLUME +/–

Jog lever

VOLUME

Earphones with

remote control

(supplied)

Note

When playing back an audio CD using the AC

power adaptor, it takes a while until the sound is

heard.

Press

u

x/CHG (x)

u

.once**

.repeatedly**

>once**

>repeatedly**

Number buttons of the track (wireless remote

control only)**

Hold down >**

Hold down .**

To

Pause

Stop

Resume play after pause

Find the beginning of the current track (AMS*)

Find the beginning of previous tracks (AMS)

Find the beginning of the next track (AMS)

Find the beginning of succeeding tracks (AMS)

Locate a specific track directly

Go forward quickly

Go backwards quickly

* Automatic Music Sensor

** These operations are possible during both play and pause.

The above operations can also be done with the buttons on the supplied earphones with remote

control or wireless remote control.

If you press REPEAT/ENTER (RPT/ENT) to display “REPEAT”, you can locate the tracks continuously in the

following order:

•When using >: next track tnext track ...... last track tfirst track tsecond track ......

•When using .: previous track tprevious track ...... first track tlast track ......

About the display

•When playing an audio CD using the AC power adaptor, indications on the remote control

display window go off until the sound is heard.

•When you press u, the total number of tracks in the audio CD and total playing time appear

for about two seconds.

•During play, the track number and the elapsed playing time of the current track appear.

•Between tracks, the time to the beginning of the next track appears with the “-”indication.

•During pause, the elapsed playing time flashes.

If the volume level does not increase

Is AVLS set to “LIMIT”? Set AVLS to “NORM.”For details, see “To protect your hearing

(AVLS)”on page 24.

If a cable is connected to the AUDIO OUT jack, you cannot adjust the volume. In such a case,

disconnect the cable.

Removing the audio CD

Remove the audio CD as illustrated.

Dent

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com