VX1828B

Preliminary Datasheet Video Processor for Middle Size LCD Panel

P.3/P.64

V1.0 050420

Table of Contents

1. FEATURE............................................................................................................................................5

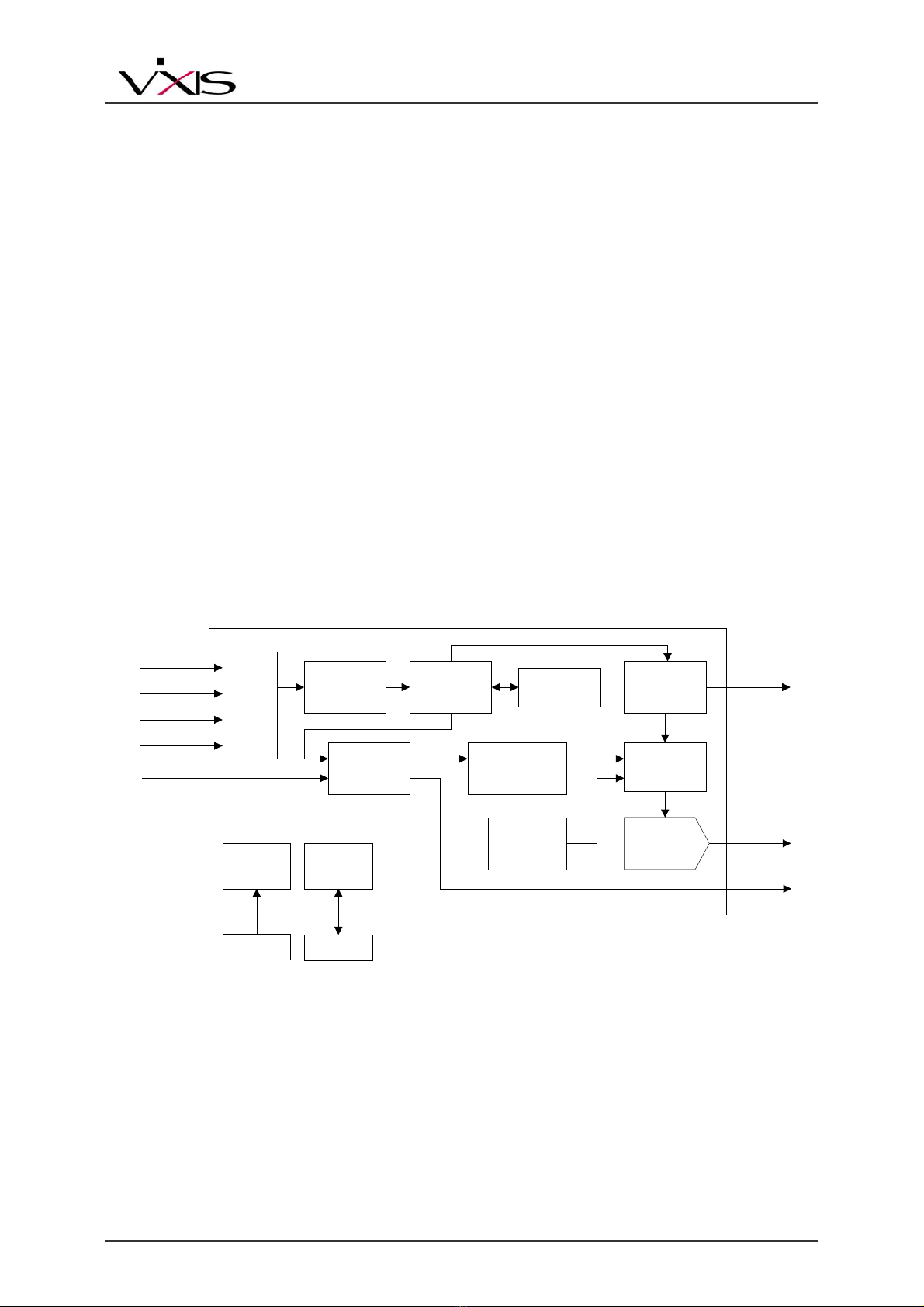

2. GENERAL DESCRIPTION .................................................................................................................6

3. APPLICATION ....................................................................................................................................7

4. PIN CONFIGURATION .......................................................................................................................8

4.1 PINOUT DIAGRAM .......................................................................................................................8

4.2 PIN ASSIGNMENT........................................................................................................................ 9

4.3 PIN DESCRIPTION .....................................................................................................................10

4.4 PIN-TYPE DEFINITION...............................................................................................................13

5. FUNCTION DESCRIPTION..............................................................................................................14

5.1 ANALOG INPUT CONFIGURATION ........................................................................................... 14

5.2 POWER-DOWN OPTION............................................................................................................15

5.3 MODE DETECTION....................................................................................................................15

5.4 COLOR-TRANSIENT IMPROVEMENT (CTI) .............................................................................15

5.5 LUMA/CHROMA ADJUSTMENT.................................................................................................15

5.6 TWO-DIMENSIONAL SHARPNESS ........................................................................................... 16

5.7 BLACK-LEVEL EXTENSION (BLE).............................................................................................17

5.8 INTERLACE DIGITAL INTERFACE ............................................................................................ 18

5.9 GAMMA CORRECTION ..............................................................................................................18

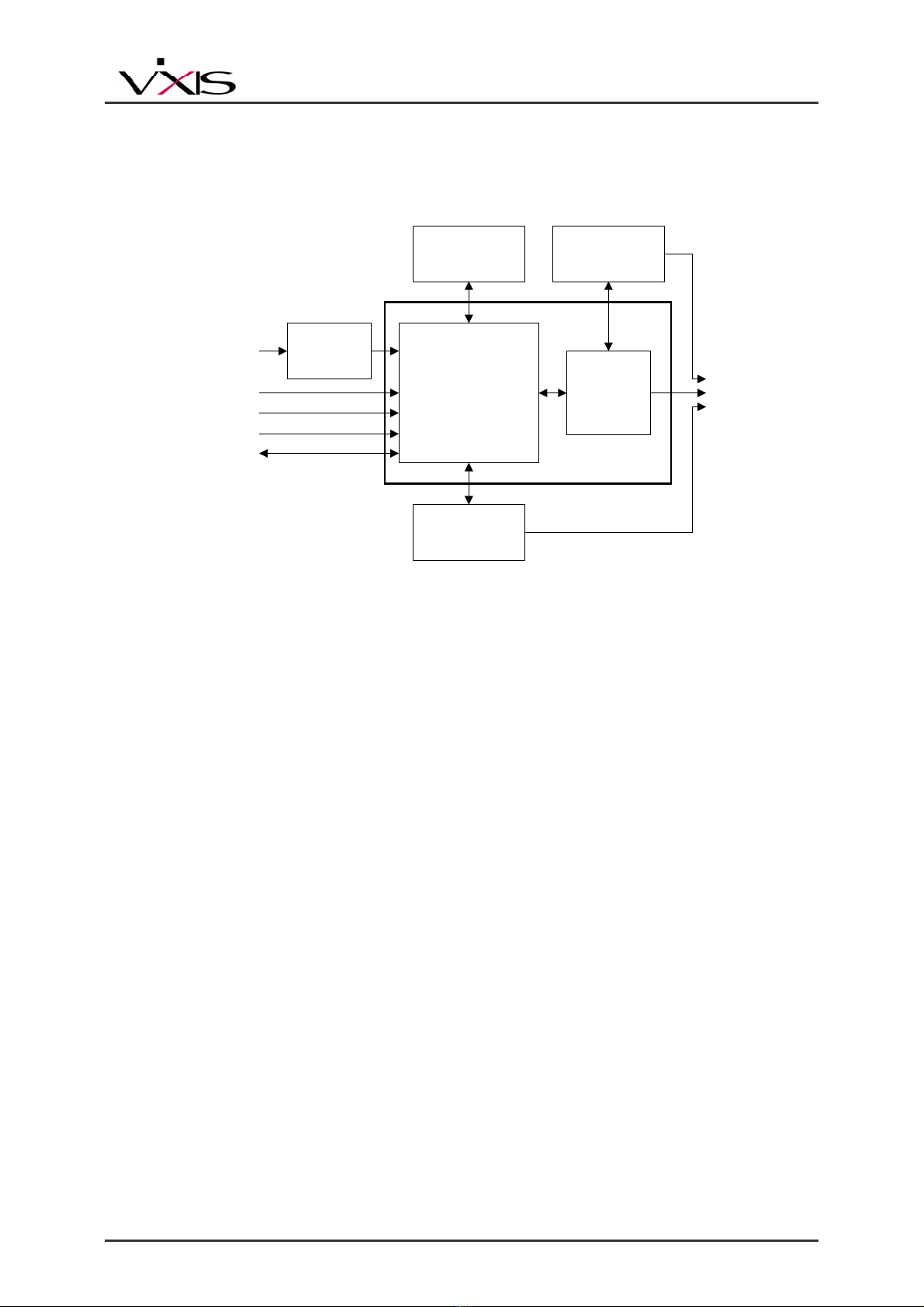

5.10 ON-SCREEN-DISPLAY (OSD)..................................................................................................20

5.10.1 OSD INTRODUCTIONS .....................................................................................................20

5.10.2 OSD DISPLAY BLOCKS.....................................................................................................20

5.10.3 OSD OPERATIONS............................................................................................................21

5.11 LCD TIMING CONTROLLER (T-CON)......................................................................................24

5.12 PULSE WIDTH MODULE (PWM) .............................................................................................24

6. REGISTER DESCRIPTION ..............................................................................................................25

6.1 REGISTER MAP .........................................................................................................................25

6.2 REGISTER DETAILS ..................................................................................................................29

6.2.1 Global Registers ...................................................................................................................29

6.2.2 Analog-Front-End Registers .................................................................................................31

6.2.4 Video Timing Generation Registers......................................................................................33

6.2.5 YC Separation Registers ......................................................................................................36

6.2.6 Demodulation Registers .......................................................................................................37