WM9090 Production Data

w PD, November 2010, Rev 4.1

2

TABLE OF CONTENTS

DESCRIPTION .......................................................................................................1

FEATURES.............................................................................................................1

APPLICATIONS .....................................................................................................1

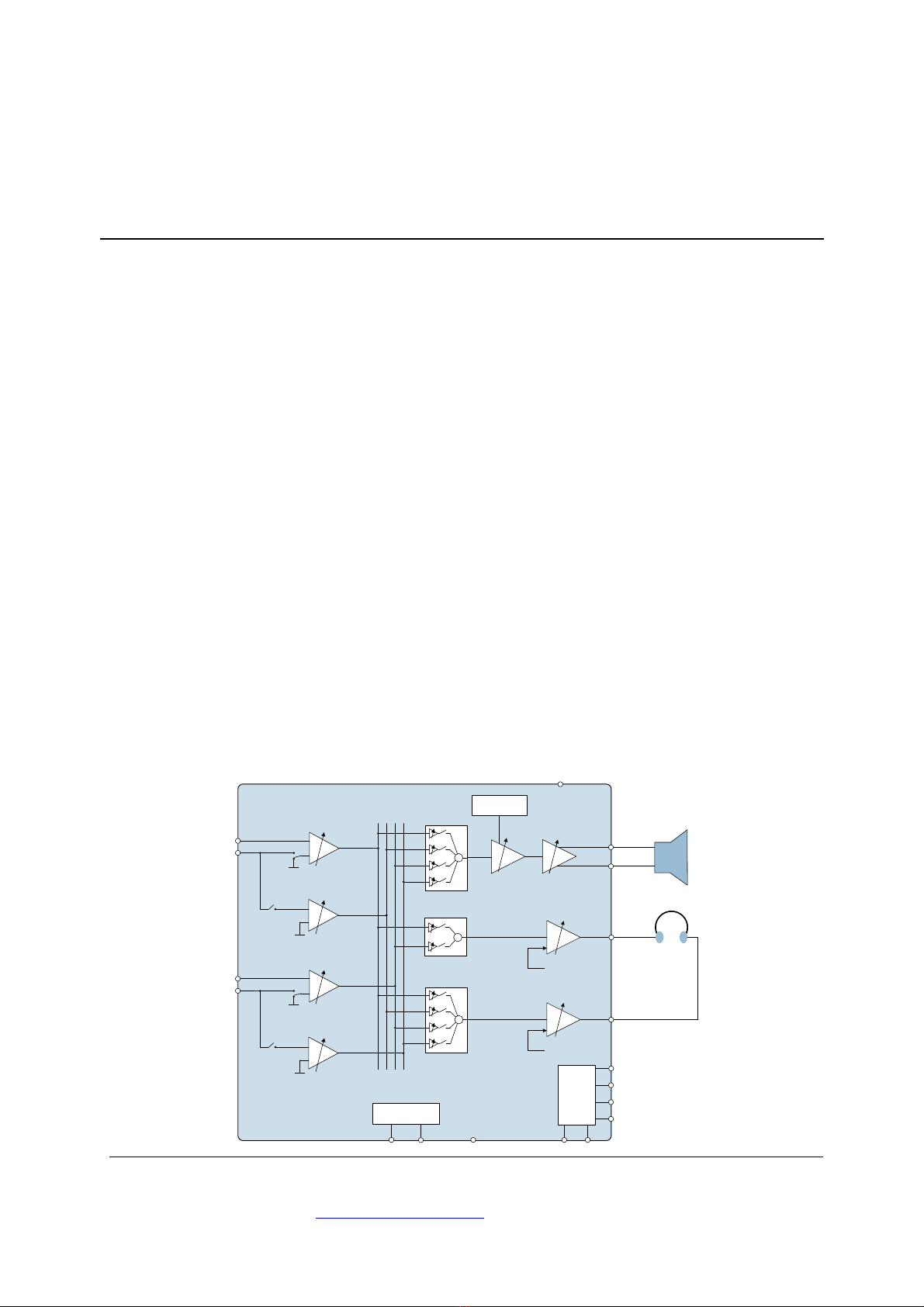

BLOCK DIAGRAM .................................................................................................1

TABLE OF CONTENTS .........................................................................................2

PIN CONFIGURATION...........................................................................................4

ORDERING INFORMATION ..................................................................................4

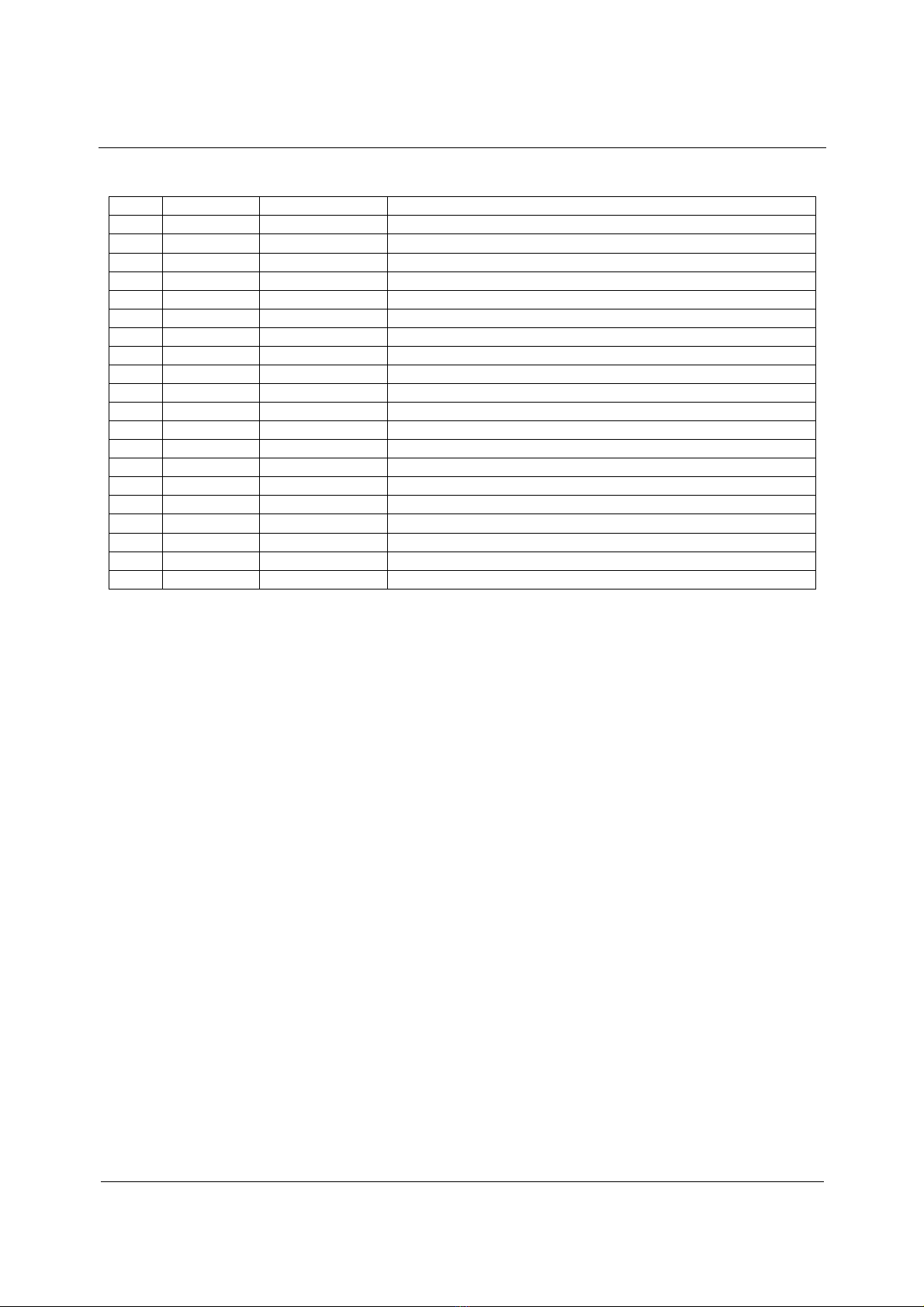

PIN DESCRIPTION ................................................................................................5

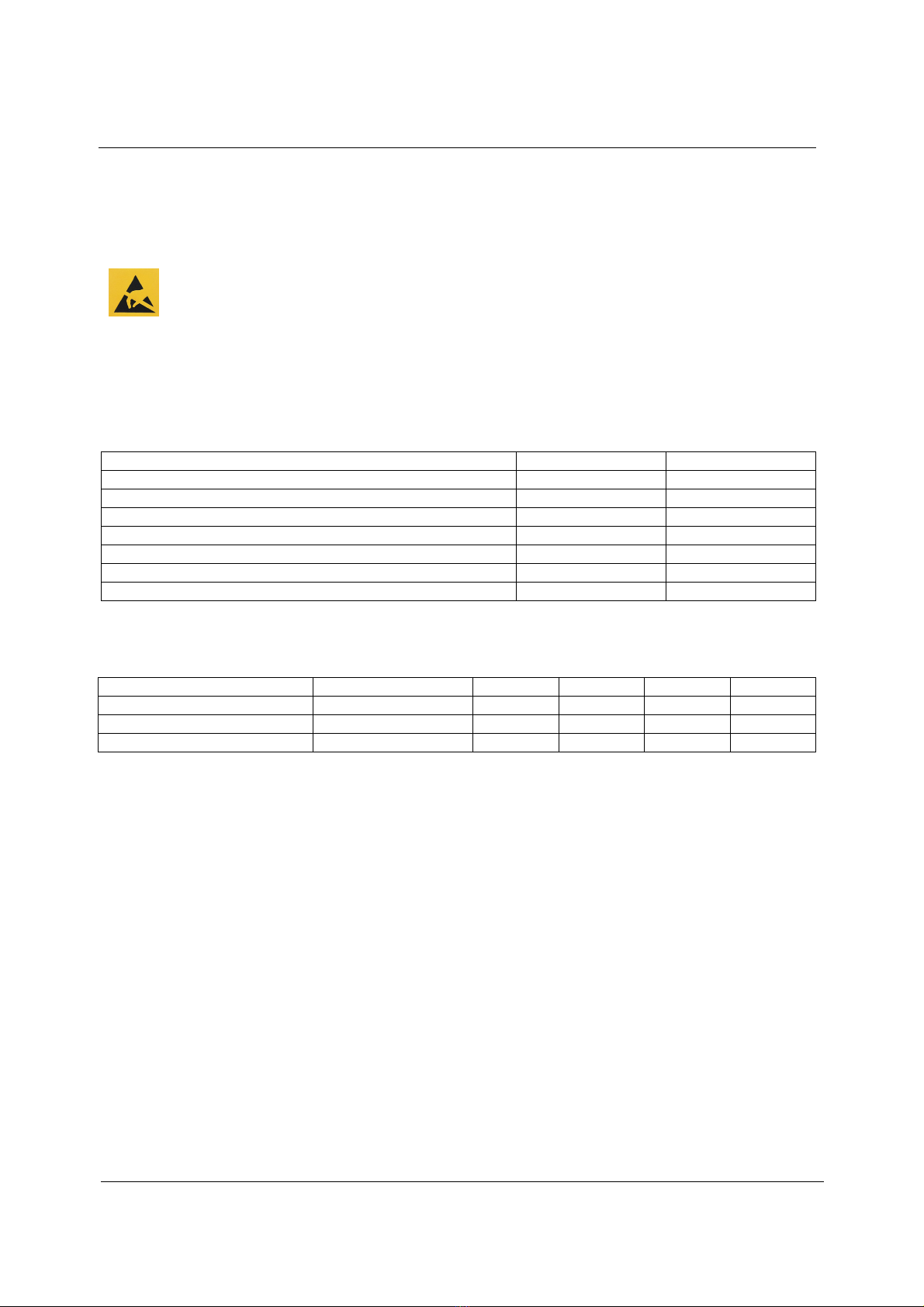

ABSOLUTE MAXIMUM RATINGS.........................................................................6

RECOMMENDED OPERATING CONDITIONS .....................................................6

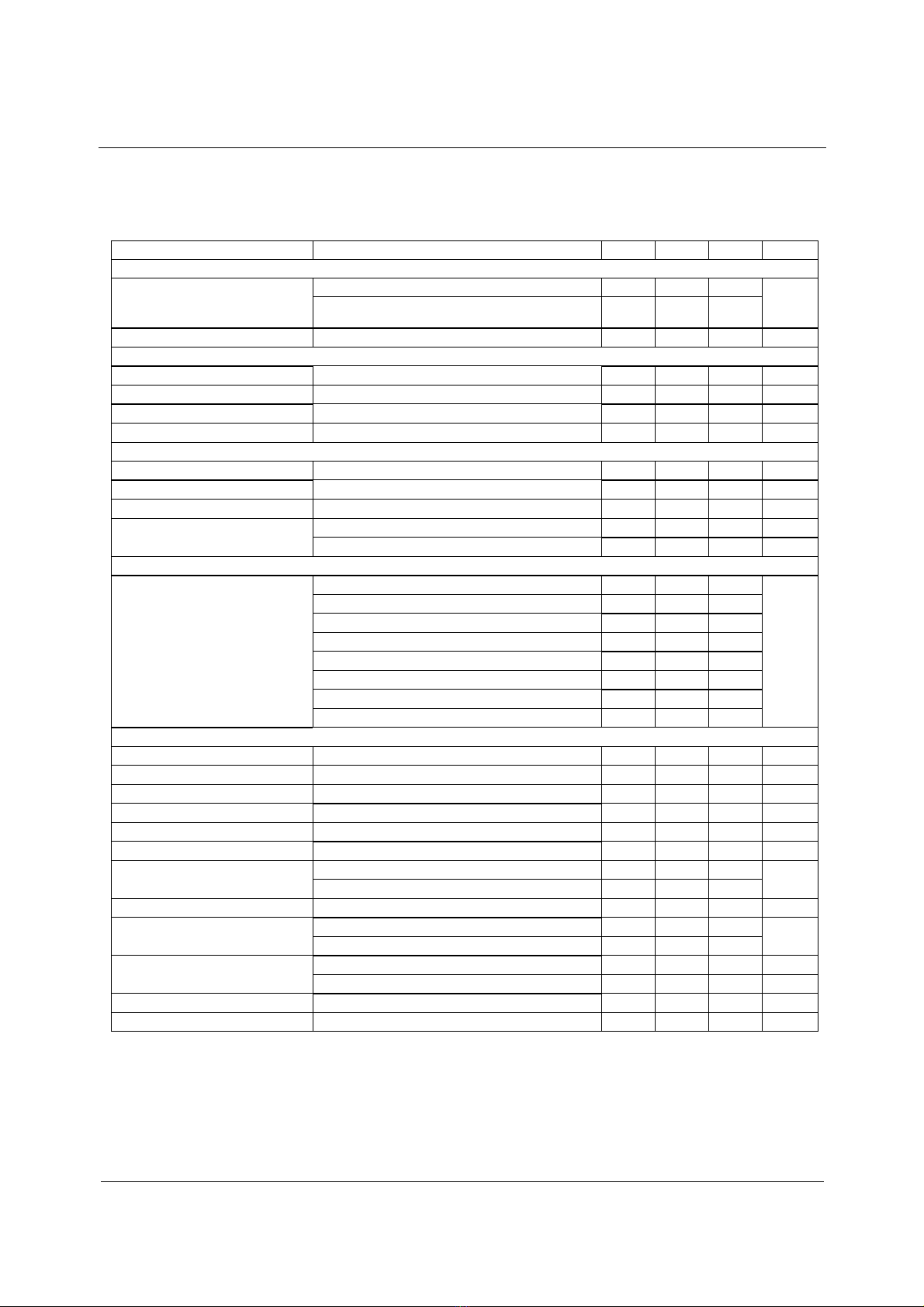

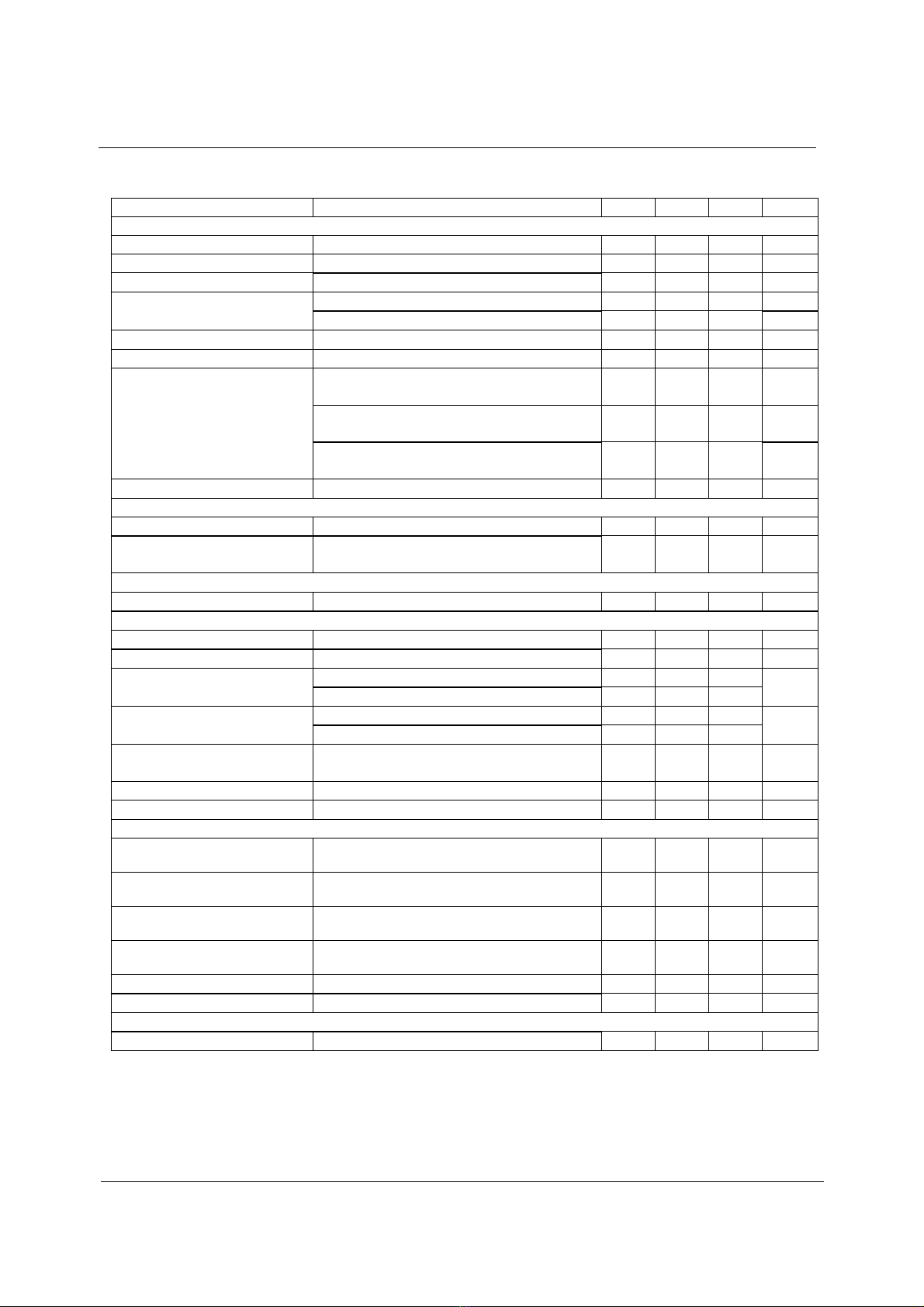

ELECTRICAL CHARACTERISTICS ......................................................................7

TERMINOLOGY............................................................................................................. 9

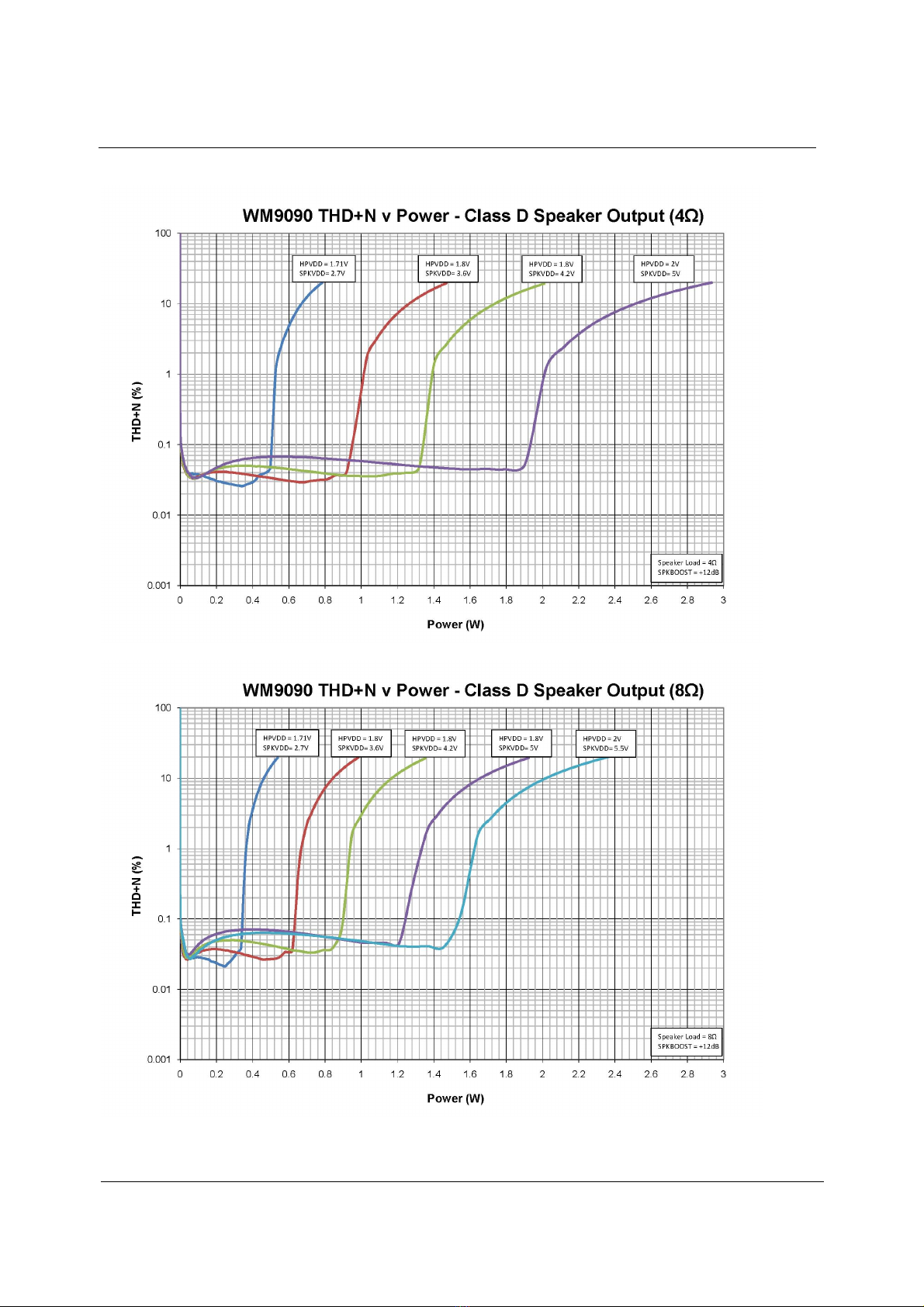

PERFORMANCE PLOTS............................................................................................. 10

TYPICAL PERFORMANCE..................................................................................11

POWER CONSUMPTION............................................................................................ 11

AUDIO SIGNAL PATHS DIAGRAM .....................................................................12

CONTROL INTERFACE TIMING .........................................................................13

DEVICE DESCRIPTION.......................................................................................14

INTRODUCTION.......................................................................................................... 14

INPUT SIGNAL PATH.................................................................................................. 15

LINE INPUTS ............................................................................................................................................ 16

INPUT PGA ENABLE ................................................................................................................................ 16

INPUT PGA CONFIGURATION ................................................................................................................ 17

INPUT PGA VOLUME CONTROL............................................................................................................. 17

OUTPUT SIGNAL PATH.............................................................................................. 20

OUTPUT SIGNAL PATHS ENABLE.......................................................................................................... 20

SPEAKER MIXER CONTROL ................................................................................................................... 21

SPEAKER OUTPUT VOLUME CONTROL................................................................................................ 22

SPEAKER BOOST MIXER CONTROL...................................................................................................... 22

HEADPHONE MIXER CONTROL ............................................................................................................. 23

HEADPHONE OUTPUT VOLUME CONTROL.......................................................................................... 24

AUTOMATIC GAIN CONTROL (AGC) ......................................................................... 27

AGC CONTROL ........................................................................................................................................ 27

AGC ANTI-CLIP ........................................................................................................................................ 27

AGC POWER LIMITING............................................................................................................................ 29

ANALOGUE OUTPUTS ............................................................................................... 31

SPEAKER OUTPUT CONFIGURATIONS................................................................................................. 31

HEADPHONE OUTPUT CONFIGURATIONS ........................................................................................... 32

CLOCKING CONTROL ................................................................................................ 32

CONTROL INTERFACE .............................................................................................. 34

CONTROL WRITE SEQUENCER................................................................................ 37

INITIATING A SEQUENCE ....................................................................................................................... 37

PROGRAMMING A SEQUENCE .............................................................................................................. 38

DEFAULT SEQUENCES........................................................................................................................... 40

POWER SEQUENCES AND POP SUPPRESSION CONTROL .................................. 43

INPUT VMID CLAMPS .............................................................................................................................. 43

HEADPHONE ENABLE/DISABLE............................................................................................................. 43

RECOMMENDED HEADPHONE START UP SEQUENCE....................................................................... 45