Table of Contents

Revision History...............................................................................................................2

Chapter 1: Introduction.............................................................................................. 5

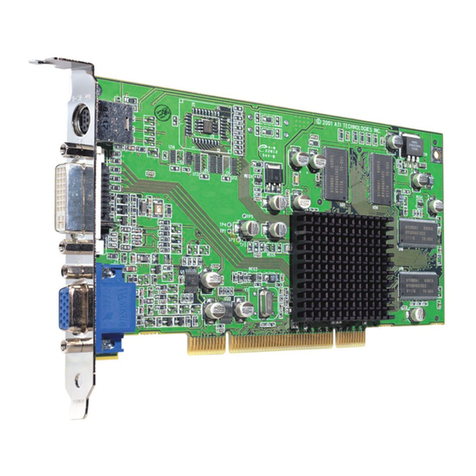

Block Diagram..............................................................................................................................7

Card Features...............................................................................................................................7

Card Specifications......................................................................................................................9

Design Flows................................................................................................................................ 9

Chapter 2: Card Installation and Configuration......................................... 14

Electrostatic Discharge Caution...............................................................................................14

Installing Alveo Data Center Accelerator Cards in Server Chassis......................................14

FPGA Configuration...................................................................................................................15

Chapter 3: Card Component Description........................................................ 16

UltraScale+ FPGA....................................................................................................................... 16

DDR4 DIMM Memory................................................................................................................16

Quad SPI Flash Memory........................................................................................................... 16

USB JTAG Interface.................................................................................................................... 17

FT4232HQ USB-UART Interface............................................................................................... 17

PCI Express Endpoint................................................................................................................17

QSFP28 Module Connectors.................................................................................................... 18

I2C Bus........................................................................................................................................18

Status LEDs.................................................................................................................................19

Card Power System................................................................................................................... 19

Appendix A: Xilinx Design Constraints (XDC) File...................................... 20

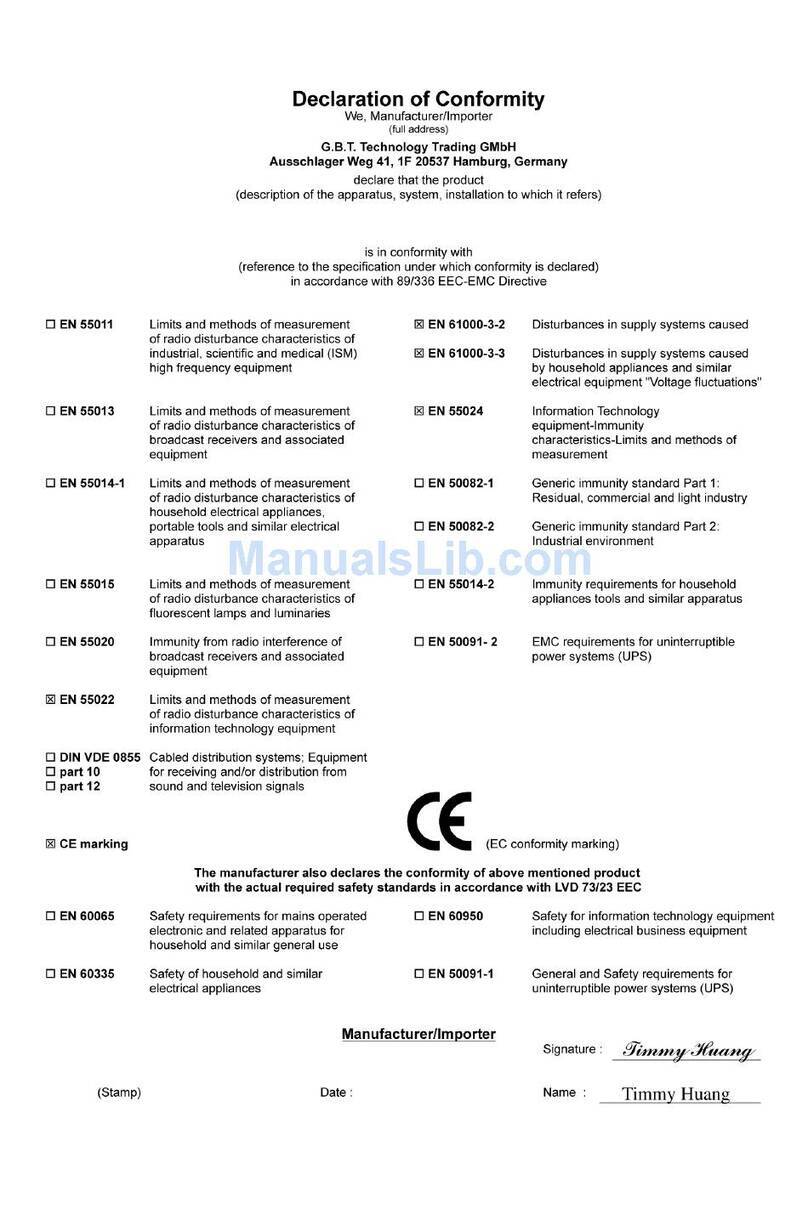

Appendix B: Regulatory and Compliance Information........................... 21

CE Directives.............................................................................................................................. 21

CE Standards..............................................................................................................................21

Compliance Markings............................................................................................................... 22

Appendix C: Additional Resources and Legal Notices............................. 23

UG1289 (v1.1.1) November 20, 2019 www.xilinx.com

Alveo U200 and U250 Accelerator Cards 3