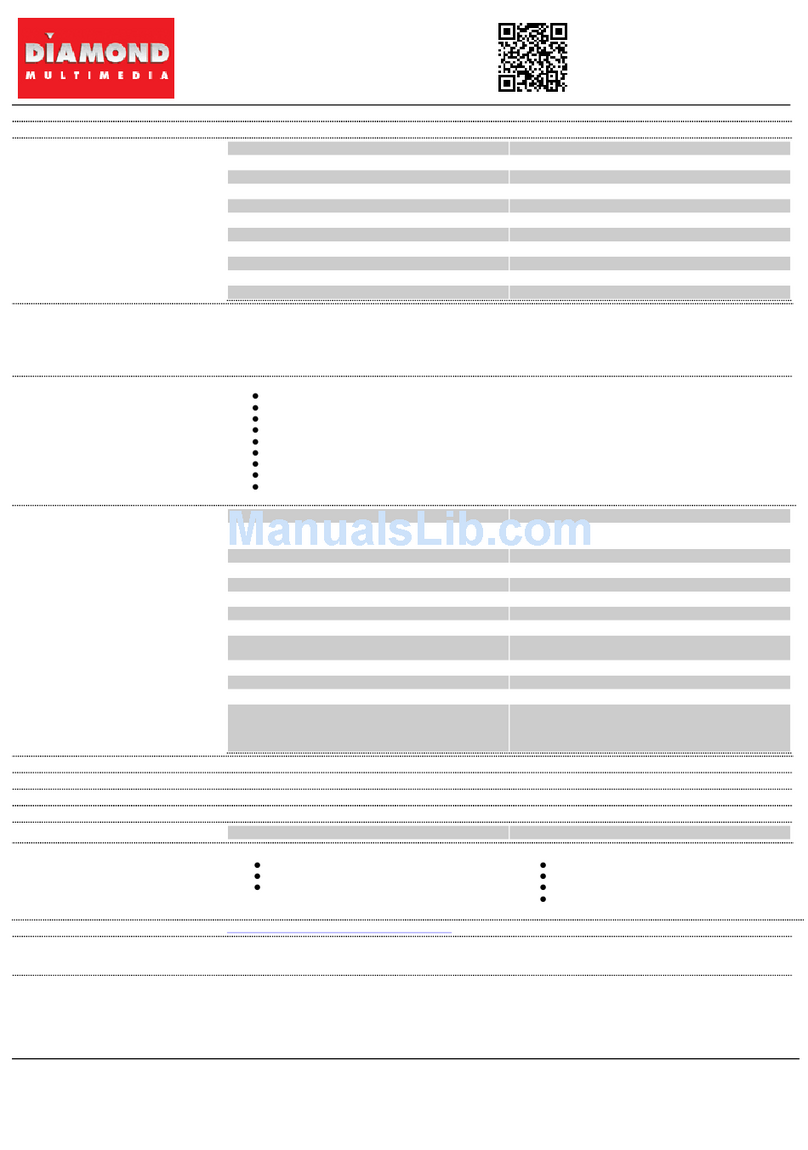

Table 1: Zynq UltraScale+ MPSoC ZU19 Pin Map (cont'd)

Pin Number Signal Name Interface

C30 CLK_GPIO_5 GPIO - Zynq UltraScale+ MPSoC <--

>Clock Synth

D29 CLK_GPIO_6 GPIO - Zynq UltraScale+ MPSoC <--

>Clock Synth

AP19 MPSOC_RFSOC_PL_GPIO1 GPIO - Zynq UltraScale+ MPSoC <--

>Zynq UltraScale+ RFSoC PL

F13 MPSOC_RFSOC_PL_GPIO10 GPIO - Zynq UltraScale+ MPSoC <--

>Zynq UltraScale+ RFSoC PL

E13 MPSOC_RFSOC_PL_GPIO11 GPIO - Zynq UltraScale+ MPSoC <--

>Zynq UltraScale+ RFSoC PL

E12 MPSOC_RFSOC_PL_GPIO12 GPIO - Zynq UltraScale+ MPSoC <--

>Zynq UltraScale+ RFSoC PL

AR19 MPSOC_RFSOC_PL_GPIO2 GPIO - Zynq UltraScale+ MPSoC <--

>Zynq UltraScale+ RFSoC PL

AP18 MPSOC_RFSOC_PL_GPIO3 GPIO - Zynq UltraScale+ MPSoC <--

>Zynq UltraScale+ RFSoC PL

AP17 MPSOC_RFSOC_PL_GPIO4 GPIO - Zynq UltraScale+ MPSoC <--

>Zynq UltraScale+ RFSoC PL

AN19 MPSOC_RFSOC_PL_GPIO5 GPIO - Zynq UltraScale+ MPSoC <--

>Zynq UltraScale+ RFSoC PL

AN18 MPSOC_RFSOC_PL_GPIO6 GPIO - Zynq UltraScale+ MPSoC <--

>Zynq UltraScale+ RFSoC PL

F15 MPSOC_RFSOC_PL_GPIO7 GPIO - Zynq UltraScale+ MPSoC <--

>Zynq UltraScale+ RFSoC PL

F14 MPSOC_RFSOC_PL_GPIO8 GPIO - Zynq UltraScale+ MPSoC <--

>Zynq UltraScale+ RFSoC PL

G14 MPSOC_RFSOC_PL_GPIO9 GPIO - Zynq UltraScale+ MPSoC <--

>Zynq UltraScale+ RFSoC PL

J30 MPSOC_RFSOC_PS_GPIO1 GPIO - Zynq UltraScale+ MPSoC <--

>Zynq UltraScale+ RFSoC PS

K30 MPSOC_RFSOC_PS_GPIO2 GPIO - Zynq UltraScale+ MPSoC <--

>Zynq UltraScale+ RFSoC PS

L29 MPSOC_RFSOC_PS_GPIO3 GPIO - Zynq UltraScale+ MPSoC <--

>Zynq UltraScale+ RFSoC PS

L30 MPSOC_RFSOC_PS_GPIO4 GPIO - Zynq UltraScale+ MPSoC <--

>Zynq UltraScale+ RFSoC PS

M29 MPSOC_RFSOC_PS_GPIO5 GPIO - Zynq UltraScale+ MPSoC <--

>Zynq UltraScale+ RFSoC PS

D14 MPSOC_MSP_GPIO1 GPIO - Zynq UltraScale+ MPSoC <-->SC

D13 MPSOC_MSP_GPIO2 GPIO - Zynq UltraScale+ MPSoC <-->SC

AH19 SOC_SCL I2C Bus

AJ18 SOC_SDA I2C Bus

M37 MAC_MP_T0_N Inter-SoC 100G MAC

M36 MAC_MP_T0_P Inter-SoC 100G MAC

L35 MAC_MP_T1_N Inter-SoC 100G MAC

L34 MAC_MP_T1_P Inter-SoC 100G MAC

Chapter 2: Pin Mapping

UG1495 (v1.0) December 17, 2021 www.xilinx.com

T1 Telco Accelerator Card User Guide 10