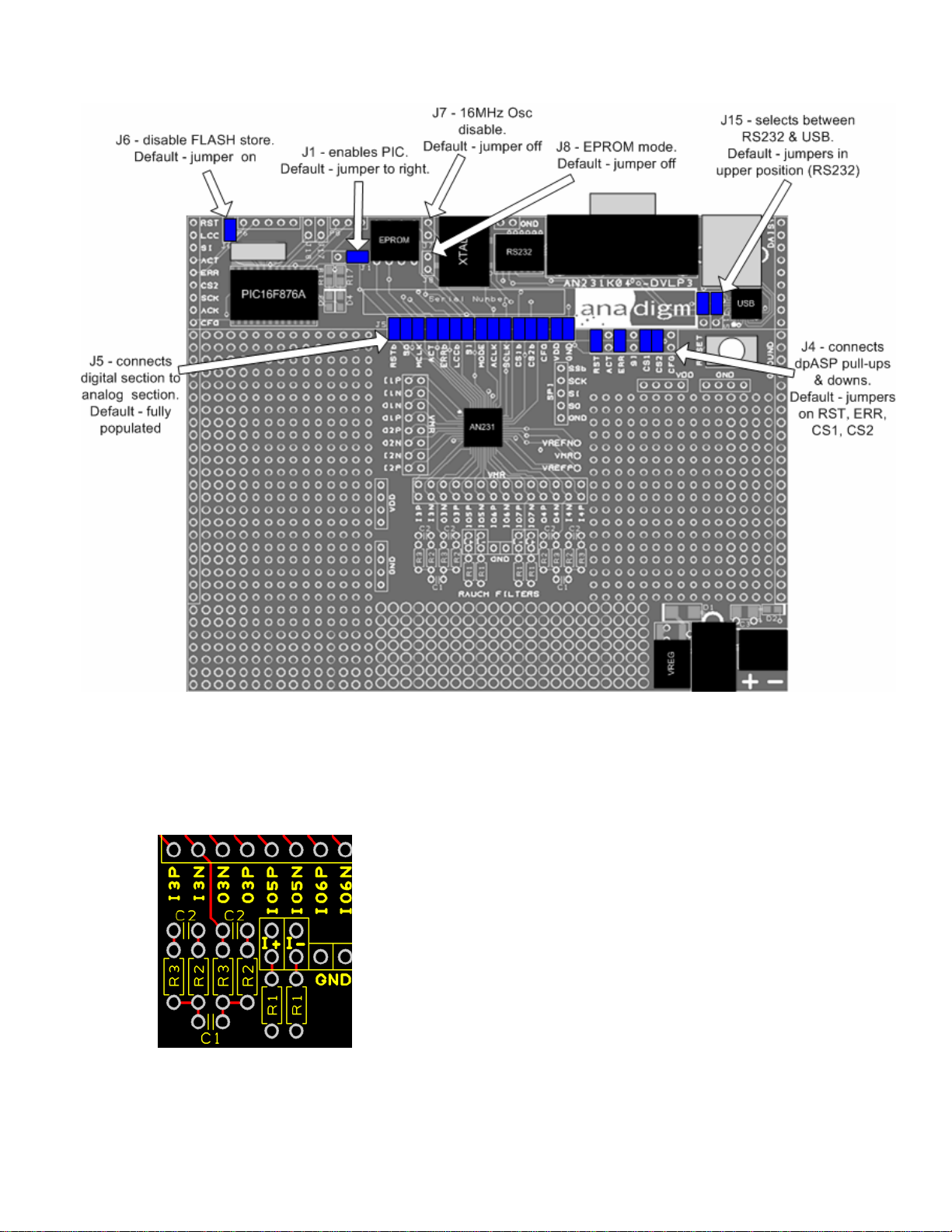

AN231K04-DVLP3 – AnadigmApex Development Board

UM023100-K001h Page 7 of 16

6.0 Other Features

6.1 VREF Pins

The 3 reference pins on the dpASP device – VMR (+1.5V), VREFP (+2.5V) and VREFN (+0.5V) – have been

connected via the p.c.b. tracks to the 3 holes to the right of the dpASP (see figure 2). In addition, VMR is available

on the inner ring or inner two rows of pins that are adjacent to the analog I/Os.

NOTE: These reference voltages are not designed to provide current.

6.2 Header Pins

All of the analog I/Os of the dpASP are brought out to header pins for easy connection. Next to these header pins is

a second row of header pins connected to VMR (+1.5V). This allows the user to connect any dpASP analog I/O to

VMR using shorting jumpers, resistor jumpers or capacitor jumpers. A shorting link (jumper) should only be used

when the I/O cell is configured as an input. Damage may occur to the device if an output if shorted to VMR.

6.3 EPROM

There is an SPI EEPROM socket in the digital section of the board. To put the board into EEPROM mode, starting

from the default jumper position (detailed below, section 7):

1. Put a jumper onto J8 which sits right next to the EPROM socket, and

2. Put a jumper on J4 in the position marked SI so that this pin is connected to a pull-down.

3. Make sure that there are jumpers on J5 in the positions marked GND, VDD, CFG, ACLK, SI, MCLK and SO

(it is OK to put jumpers in all positions of J5).

4. Move the jumper on J1 to the left to disable the PIC.

Press the “reset” button to download the circuit from the EPROM into the dpASP.

Note that an EEPROM integrated circuit is not supplied with this Development Kit. If you wish to use an SPI

EEPROM, source one and place it in to the socket on the board. An example of a compatible SPI EPROM is the

Atmel AT25080.

To write the EPROM follow this procedure:

1. With the board powered down, place a jumper on J8 to put the board in EPROM mode.

2. Make sure that the jumper J1 is placed to the right to enable the PIC.

3. Make sure that there is no jumper on J6 (FLASH storage must be enabled to write the EPROM).

4. Remove the jumpers marked MCLK and SO from the digital interface J5.

5. Power up the board and configure it in the usual way with the circuit that is required to be stored in EPROM.

6. Power down the board and replace the jumpers marked MCLK and SO on the digital interface J5.

7. Move the jumper J1 to the left to disable the PIC.

8. Keep the jumper on J8. Also make sure that there is a jumper on J4 in the SI position.

9. Power up the board and it will configure from the EPROM. Resetting the board will also cause it to be

configured from the EPROM. Note that there will be no LEDs lit to show that the configuration was successful.

This is because the LEDs are driven by the PIC and this is disabled when booting from EPROM.

*NOTE: before configuring the board, a setting needs to be changed in AnadigmDesigner®2 if the circuit is to be

stored in EPROM. To change this setting, go to the Settings menu in AnadigmDesigner®2, select Active Chip

Settings, then select the Chip tab. In the pull-down menu labelled “How is this mode pin connected on the target

board?” select “Mode pin has been tied high (VDD)”. Click on OK. Then configure the board. If an EPROM

programmer is used to program the EPROM, this setting still needs to be changed in AnadigmDesigner®2 before

generating the data for programming into the EPROM.

6.4 Reset Button

There is a reset button near the upper right corner of the board. This resets both the dpASP and the PIC (unless

the PORb jumper is removed from J5 or the J1 jumper is in the left position).

In EPROM mode, press the reset button to load the circuit from the EPROM into the dpASP.

6.5 SPI Port

There is an SPI port for direct control of the dpASP by an external SPI controller. Note that all the jumpers should

be removed from J5 when the SPI port is used. (see the AN231E04 dpASP specification and use guide for details

of this SPI connection)