ASAHI AKD55X4-B User manual

[AKD55X4-B]

<KM119202> 2015/09

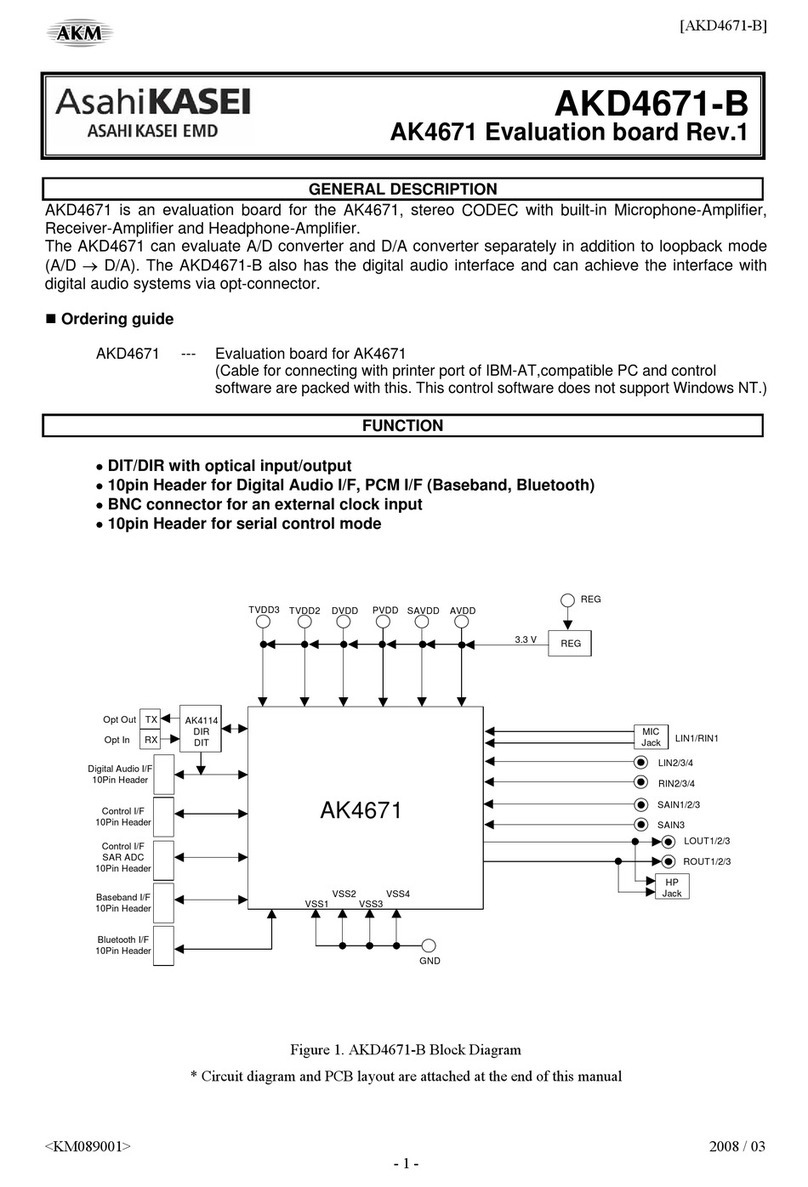

GENERAL DESCRIPTION

The AKD55X4-B is an evaluation board for AK55X4/X2, which is 32bit, 8k – 768kHz, 4ch/2ch ADC.

4ch ADC (AK55X4) : AK5534, AK5554, AK5574 2ch ADC (AK55X2) : AK5552, AK5572

The AKD55X4-B is includes the analog input circuit and also has a digital interface transmitter .

Further, the AKD55X4-B can achieve the interface with digital audio systems via BNC-connector.

Ordering guide

AKD55X4-B -- Evaluation board for AK55X4/X2

FUNCTION

DIT with BNC or Optical digital output.

ADC 4ch/2ch input is possible.

BNC connector for an external clock input.

AK4118A

(DIT)

AIN1

AIN2

Clock

Generator

+VOP

Input

Buffer

AK55X4

AK55X2

-VOP

TVDD

Regulators

5V/3.3V

+15V

-15V

AVDD

3.3V

BNC_TX

(OUT)

DSP Data

10pin Header

AIN3

AIN4

Input

Buffer

キャノンコネクタ

(IN)

OPT_TX

(OUT)

1.8V

VDD18

Figure 1. AKD55X4-B Block Diagram

* Circuit diagram and PCB layout are attached at the end of this manual.

AK55X4/X2 Evaluation Board Rev.2

- 1-

[AKD55X4-B]

<KM119202> 2015/09

Evaluation Board Diagram

Board Diagram

J801 J802 J800

SW604

SW600

U4

J200

J202 J203

J201

SW603

SW601

PORT500

T1 T2

J805 J804

T3

J806 J807 J808

J809

J300

J302 J303

J301

T4

T5

SW602

J400

PORT400

PORT602

PORT601

PORT600

PORT610

J600

SW400

U1

AKD55X4-B

AK55X4/X2

-15V VSS +15V VBIAS AVDD VCC TVDD VDD18 D3.3V

Figure 2. AKD55X4-B Board Diagram

Description

(1) U1 ( AK55X4/AK55X2 )

32bit,8k - 768kHz,4ch/2ch A/D Converter.

(2) J200,J201,J300,J301 ( Analog data )

Cannon connector : Differential Analog Input

(3) J202,J203,J302,J303 ( Analog data )

BNC Connector : Single-ended Analog Input.

(4) J400 / PORT400 ( Digital data )

BNC Connector / Optical Connector: Digital Output.

(5) J800, J801, J802,J804,J805,J806,J807,J808,J809 ( Power supply )

Power Supply Connector.

(6) PORT600,PORT601 ( pin header )

Pin header for evaluation (MCLK, BICK, LRCK, SDTO1, SDTO2, TDMIN).

- 2-

[AKD55X4-B]

<KM119202> 2015/09

(7) PORT602 ( pin header )

Pin header for evaluation (DCLK, DSDOL1/R1, DSDOL2/R2).

(8) U4 ( AK4118A )

AK4118A has DIT. Transports output data from AK55X4/X2.

(9) SW600 ( Toggle switch )

Toggle type-switch PDN for AK55X4/X2.

“H” : PDN = High

“L” : PDN = Low

(10) SW601 ( Toggle switch )

Toggle type-switch PDN for AK4118A.

“H” : PDN = High

“L” : PDN = Low

(11) SW602,SW603,SW604 ( Dip switch)

DIP type-switch for AK55X4/X2.

“H” : Digital signal = High

“L” : Digital Signal = Low

(12) SW400 ( Dip switch (Dual In-line Package switch)

DIP type-switch for AK4118A.

“H” : Digital signal = High

“L” : Digital Signal = Low

(13) J600 ( MCLK external input )

BNC Connector : External Clock Input (MCLK).

(14) T1, T2, T3, T4, T5

Regulator for AK55X4/X2, AK4118A, Logic Circuit.

T1 : Regulated AVDD, VBIAS (5.0V/3.3V) from +15V.

T2 : Regulated VCC1, VCC2 (5.0V) from +15V.

T3 : Regulated TVDD (3.3V) from +5V.

T4 : Regulated TVDD, VDD18 (1.8V) from +5V

T5 : Regulated D33V (3.3V) from +5V.

- 3-

[AKD55X4-B]

<KM119202> 2015/09

Evaluation Board Manual

Operation sequence

[1] Power supply line settings

[2] Jumped pins settings

[3] DIP switches settings

[4] Toggle switches settings

[5] Register control (Serial control)

[6] Evaluation modes

- 4-

[AKD55X4-B]

<KM119202> 2015/09

[1] Power supply line settings

(1-1) Power supply settings : Used the regulator (T1,T2,T3,T4,T5) <Default>

Set up the power supplied lines :

* Each supply line should be distributed from the power supply unit.

Name Color Setting (Typ) Function Comments Default Settings

J800 +15V Green +15V Regulator and Op-amp

power supply

Should always be connected +15V

J801 -15V Blue -15V Regulator and Op-amp

power supply

Should always be connected -15V

J804 AVDD Red +5.0V / 3.3V AK55X4/X2 AVDD 5.0V/3.3V regulator is used,

R807=short by default.

When jack is used,

R808=short.

REG :

(R807 = short)

J805 VBIAS Red +5.0V / 3.3V Referential Voltage

source for Op-amp

5.0V/3.3V regulator is used,

R809=short by default.

When jack is used,

R810=short.

REG :

(R809 = short)

J809 VCC Red +5.0V 3.3V Regulator power

supply

5.0V regulator is used,

R811=short by default.

When jack is used,

R812=short.

REG :

(R811 = short)

J806 TVDD Orange +1.8 / +3.3V/ AK55X4/X2 TVDD,

Logic IC power supply

3.3V regulator is used,

JP800=3.3V and JP801=REG

by default.

When 1.8V regulator is used,

JP800=1.8V and JP801=REG.

When jack is used,

JP801=JACK short.

REG (3.3V) :

(JP800=3.3V and

JP801=REG)

J807 VDD18 Orange +1.8V AK55X4/X2 VDD18 LDO of AK55X4/X2 is used,

JP802=open by default.

When 1.8V regulator is used,

JP802=REG.

When jack is used,

JP802=JACK.

Open :

(JP802=open)

J808 D3.3V Orange +3.3V AK4118A 3.3V VDD,

Logic IC power supply

3.3V regulator is used,

JP803=REG by default.

When jack is used,

JP803=JACK.

REG :

(JP803=REG)

J802 VSS Black 0V Ground Should always be connected 0V

Table 1-1. Power supply line setting ( default : used the regulator )

- 5-

[AKD55X4-B]

<KM119202> 2015/09

(1-2) About jumper for power supply :

The roles of the jumper or the short resistance for each power supply supplied from the regulator are as follows.

Connection of the jumper for power supply :

Name Function Comments Default Settings

R807

R808

AVDD1 Select regulator power supply

or jack for AVDD1

AVDD for AK55X4/X2:

R1007=short : 5.0V/3.3V regulator is used. (default)

R1008=short : Jack is used.

REG :

R807=short

R808=open

R809

R810

VBIAS Select regulator power supply

or jack for VBIAS

VBIAS for Op-amp Referential Voltage source:

R809=short : 5.0V/3.3V regulator is used. (default)

R810=short : Jack is used.

REG :

R809=short

R810=open

R811

R812

VCC1,

VCC2

Select regulator power supply

or jack for 5.0V Regulator

power supply

VCC1, VCC2 for 5.0V Regulator power supply:

R811=short : 5.0V regulator is used. (default)

R812=short : Jack is used.

REG :

R811=short

R812=open

JP800 TVDD-VSEL Select regulator power supply

3.3V or 1.8V for TVDD

TVDD for AK55X4/X2 and Logic IC:

JP800=3.3V : 3.3V regulator is used. (default)

JP800=1.8V : 1.8V regulator is used.

3.3V :

JP800=3.3V

JP801 TVDD-SEL Select regulator power supply

or jack for TVDD

TVDD for AK55X4/X2 and Logic IC:

JP801=REG : Regulator is used. (default)

JP801=JACK: Jack is used.

REG :

JP801=REG

JP802 VDD18-SEL Select External power supply or

LDO power supply of AK55XX

for VDD18

VDD18 selector for AK55X4/X2:

JP802=REG : External Power supply of 1.8V regulator is

used.

JP802=JACK : External Power supply of Jack is used.

JP802=open : LDO of AK55X4/X2 is used. (default)

LDO of AK55XX :

JP802=open

JP803 D33V-SEL Select regulator power supply

or jack for D33V

D33V for AK4118A and Logic IC:

JP1003=REG : 3.3V regulator is used. (default)

JP1003=JACK : Jack is used.

REG :

JP803=REG

Table 1-2. Jumper for power supply

- 6-

[AKD55X4-B]

<KM119202> 2015/09

[2] Jumped pins settings

No Names Default Functions

1 JP400 TXDATA-SEL COAX Select COAX / Optical Connector for TX data of AK4118A.

COAX: COAX for TX data of AK4118A. (default)

OPT: Optical for TX data of AK4118A.

2 PORT605 BICK-SEL DIT Select input / output to AK55X4/X2 (U1) BICK

DIT: BICK-AK4118A-T (default)

PORT: Pin Header PORT600-BICK

GND: Connected to VSS

Open: No signal

3 PORT606 LRCK-SEL DIT Select input / output to AK55X4/X2 (U1) LRCK

DIT: LRCK-AK4118A-T (default)

PORT: Pin Header PORT600-LRCK

GND: Connected to VSS

Open: No signal

4 PORT607 BICK-PHASE THR Select polarity (non-inverted output / inverted output) of

BICK_SEL inputs / outputs.

THR: Non-inverted output. (default)

INV: Inverted output.

5 PORT608 SDTO_SEL SDTO1 Select input to DIT:AK4118A (U4) DAUX

SDTO1: AK55X4/X2-SDTO1 is used. (default)

SDTO2: AK55X4/X2-SDTO2 is used.

open: No signal for DAUX-AK4118A-T

6 PORT609 TDMI-SEL Open Select connect to AK55X4/X2 (U1) TDMI

Open: No signal for TDMIN (default)

Short: Pin Header PORT601-TDMIN

7 PORT610 MCKI-SEL DIT Select input to AK55X4/X2 (U1) MCLK

DIT: MCLK-AK4118A-T (default)

PORT: Pin Header PORT600-MCLK

EXT: External MCLK (JACK:J600 EXT) input.

GND: Connected to VSS

8 JP600 EXT Open Open: No input (default)

Short: External MCLK (JACK:J600 EXT) input.

9 JP700 PS-SEL1 SDA/CDTI Select input / output to AK55X4/X2 (U1) CKS0/SDA/CDTI

SDA/CDTI:

SDA/CDTI signal input / output to AK55X4/X2. (default)

CKS0:

CKS0 signal of SW803 input to AK55X4/X2.

10 JP701 PS-SEL2 CAD0-I2C/CSN Select input to AK55XX (U1) CKS1/CAD0-I2C/CSN

CAD0-I2C/CSN:

CAD0-I2C/CSN signal input to AK55XX. (default)

CKS1:

CKS1 signal of SW803 input to AK55XX.

11 JP702 PS-SEL3 CAD0-I2C Select input to JP701 CAD0-I2C/CSN

CAD0-I2C:

CAD0-I2C signal of SW602 input to JP701. (default)

CSN:

CSN signal of SW602 input to JP701.

- 7-

[AKD55X4-B]

<KM119202> 2015/09

12 JP703 PS-SEL4 SCL/CCLK Select input to AK55X4/X2 (U1) CKS2/SCL/CCLK

SCL/CCLK:

SCL/CCLK signal input to AK55X4/X2. (default)

CKS2:

CKS2 signal of SW603 input to AK55X4/X2.

13 JP704 PS-SEL5 CAD1 Select input to AK55X4/X2 (U1) CKS3/CAD1

CAD1: CAD1 signal input to AK55X4/X2. (default)

CKS3: CKS3 signal of SW603 input to AK55X4/X2.

14 JP705 PS-SEL6 PS Select input to AK55X4/X2 (U1) PS/CAD0-SPI

PS:

PS signal input to AK55X4/X2. (default)

CAD0-SPI:

CAD0-SPI signal of SW602 input to AK55X4/X2.

15 JP800 TVDD-VSEL 3.3V Select power supply voltage of TVDD

3.3V: Regulator T3 (+5V => 3.3V) (default)

1.8V: Regulator T4 (+5V => 1.8V)

16 JP801 TVDD-SEL TVDD Select power supply to TVDD

REG: Regulator T3/T4 (default)

JACK: Power supply jack J806 “TVDD”

17 JP802 VDD18-SEL REG Select power supply to VDD18

REG: Regulator T4 (default)

JACK: Power supply jack J807 “VDD18”

18 JP803 D33V-SEL REG Select power supply to D33V

REG: Regulator T5 (+5V => 3.3V) (default)

JACK: Power supply jack J808 “D3.3V”

Table 2. Main board Jumper pin setting

- 8-

[AKD55X4-B]

<KM119202> 2015/09

[3] DIP switches settings

(3-1). Setting for SW400 (Sets AK4118A (U4) audio format and master clock setting)

No. Switch Name Function default

1 DIF2 Set-up of DIF0 pin. H

2 DIF1 Set-up of DIF1 pin. L

3 DIF0 Set-up of DIF2 pin. H

4 OCKS1 Set-up of OCKS1 pin. H

5 OCKS0 Set-up of OCKS0 pin. L

Table 3-1. SW400 Setting (AK4118A)

Mode

DIF2 pin

SW400_1

DIF1 pin

SW400_2

DIF0 pin

SW400_3 DAUX SDTO LRCK BICK

DIF2 bit DIF1 bit DIF0 bit I/O I/O

0 0 0 0 24bit, Left

justified

16bit, Right

justified H/L O 64fs O

1 0 0 1 24bit, Left

justified

18bit, Right

justified H/L O 64fs O

2 0 1 0 24bit, Left

justified

20bit, Right

justified H/L O 64fs O

3 0 1 1 24bit, Left

justified

24bit, Right

justified H/L O 64fs O

4 1 0 0 24bit, Left

justified

24bit, Left

justified H/L O 64fs O

5 1 0 1 24bit, I2S 24bit, I2S L/H O 64fs O default

6 1 1 0 24bit, Left

justified

24bit, Left

justified H/L I 64-128fs I

7 1 1 1 24bit, I

2

S 24bit, I

2

S L/H I 64-128fs I

Table 3-2. Audio format (AK4118A)

OCKS1 pin

SW400_4

OCKS0 pin

SW400_5 (X’tal) MCKO1 MCKO2 fs (max)

OCKS1 bit OCKS0 bit

0 0 256fs 256fs 256fs 96 kHz

0 1 256fs 256fs 128fs 96 kHz

1 0 512fs 512fs 256fs 48 kHz default

1 1 128fs 128fs 64fs 192 kHz

Table 3-3. Master Clock Frequency Select (AK4118A)

- 9-

[AKD55X4-B]

<KM119202> 2015/09

(3-2). Setting for SW802 (Sets AK55X4/X2 (U1) )

No. Switch Name Function default

1 TEST TEST Enable. L

2 PW0 ADC Power Management and Monaural / Stereo select. H

3 PW1 ADC Power Management and Monaural / Stereo select. H

4 PW2 ADC Power Management and Monaural / Stereo select. H

5 MSN

Master/Slave select.

L: Slave Mode

H: Master Mode

L

6 CAD0-SPI Chip Address0 Pin in 3-wire serial control mode.

(I2C pin =”L”)

L

7 CAD0-I2C Chip Address0 Pin in I2C bus serial control mode.

(I2C pin =”H”, PS pin =”L”)

L

8 CAD1

Chip Address1 Pin in I2C bus or 3-wire serial control mode.

(3-wire : I2C pin =”L”)

(I2C bus : I2C =”H”, PS pin ”L”)

L

Table 3-4. SW602 Setting

(3-3). Setting for SW603 (Sets AK55X4/X2 (U1) )

No. Switch Name Function default

1 CKS0 Clock Mode Setting #0 L

2 CKS1 Clock Mode Setting #1 H

3 CKS2 Clock Mode Setting #2 H

4 CKS3 Clock Mode Setting #3 L

5 DIF0/DSDSEL0

DIF0 : Audio Data Format select in PCM Mode

L: MSB justified

H: I2S

DSDSEL0 : DSD Sampling Rate Control in DSD Mode

H

6 DIF1/DSDSEL1

DIF1 : Audio Data Format select in PCM Mode

L: 24-bit Mode

H: 32-bit Mode

DSDSEL1 : DSD Sampling Rate Control in DSD Mode

L

7 SLOW/DCKB SLOW : Slow Roll-OFF Digital Filter select in PCM Mode

DCLKB : Polarity of DCLK in DSD Mode

L

8 SD/PMOD SD : Short Delay Digital Filter select in PCM Mode

PMOD : DSD Phase Modulation Mode select in DSD Mode

L

Table 3-5. SW603 Setting

- 10-

[AKD55X4-B]

<KM119202> 2015/09

(3-4). Setting for SW604 (Sets AK55X4/X2 (U1) )

No. Switch Name Function default

1 LDOE

LDO Enable

L: LDO Disable

H: LDO Enable

H

2 ODP Output Data Placement Select. L

3 TDM0 TDM Interface Format select #0 L

4 TDM1 TDM Interface Format select #1 L

5 PS

Control mode select (I2C pin =”H”)

L: I2C Bus serial control mode

H: Parallel control mode

L

6 I2C

Control mode select

L: 3-wire serial control mode

H: I2C Bus serial control mode

H

7 DP

DSD Mode Enable

L: PCM Mode

H: DSD Mode

L

8 HPFE/DCKS

HPFE : High Pass Filter Enable

L: HPF Disable

H: HPF Enable

DCKS : Master Clock Frequency select at DSD Mode (DSD only)

L: 512fs

H: 768fs

H

Table 3-6. SW604 Setting

- 11-

[AKD55X4-B]

<KM119202> 2015/09

Parallel Mode, ODP pin = “L” :

PW0 pin

SW602_2

PW1 pin

SW602_3

PW2 pin

SW602_4

Power ON/OFF Data on Slot

Ch4 Ch3 Ch2 Ch1 Slot 4 Slot 3 Slot 2 Slot 1

L L L OFF OFF OFF OFF All “0” All “0” All “0” All “0”

L L H ON ON OFF OFF (CH3+4)

/2

(CH3+4)

/2

All “0” or

TDMI

All “0” or

TDMI

L H L OFF OFF ON ON All “0” or

TDMI

All “0” or

TDMI

(CH1+2)

/2

(CH1+2)

/2

L H H ON ON ON ON (CH3+4)

/2

(CH3+4)

/2

(CH1+2)

/2

(CH1+2)

/2

H L L OFF ON ON ON All “0” CH3 CH2 CH1

H L H ON ON OFF OFF CH4 CH3 All “0” All “0”

H H L OFF OFF ON ON All “0” All “0” CH2 CH1

H H H ON ON ON ON CH4 CH3 CH2 CH1 default

Table 3-7-1-1. Channel Power & Mono Mode Select (ODP pin = “L”) (AK55X4)

Parallel Mode, ODP pin = “H” :

PW0 pin

SW602_2

PW1 pin

SW602_3

PW2 pin

SW602_4

Power ON/OFF Data on Slot

Ch4 Ch3 Ch2 Ch1 Slot 4 Slot 3 Slot 2 Slot 1

L L L OFF OFF OFF OFF All “0” All “0” All “0” All “0”

L L H ON ON ON ON All “0” or

TDMI

All “0” or

TDMI

(CH3+4)

/2

(CH1+2)

/2

L H L ON ON ON ON CH4 CH3 CH2 CH1

L H H ON ON ON ON

All “0”

or

TDMI

All “0”

or

TDMI

All “0”

or

TDMI

(CH1+2

+3+4)/4

H L L ON ON ON ON CH4 CH3 CH2 CH1

H L H ON ON ON ON All “0” or

TDMI

All “0” or

TDMI

(CH3+4)

/2

(CH1+2)

/2

H H L ON ON ON ON CH4 CH3 CH2 CH1

H H H ON ON ON ON All “0” or

TDMI

All “0” or

TDMI

All “0” or

TDMI

(CH1+2

+3+4)/4

Table 3-7-1-2. Channel Power & Mono Mode Select (ODP pin = “H”) (AK55X4)

- 12-

[AKD55X4-B]

<KM119202> 2015/09

Parallel Mode, ODP pin = “L” :

PW0 pin

SW602_2

PW1 pin

SW602_3

PW2 pin

SW602_4

Power

ON/OFF Data on Slot

Ch2 Ch1 Slot 2 Slot 1

L L L OFF OFF All “0” All “0”

L L H ON OFF CH2 All “0”

L H L OFF ON All “0” CH1

L H H ON ON (CH2+1)

/2

(CH2+1)

/2

H L L OFF OFF All “0” All “0”

H L H ON OFF CH2 All “0”

H H L OFF ON All “0” CH1

H H H ON ON CH2 CH1 default

Table 3-7-2-1. Channel Power & Mono Mode Select (ODP pin = “L”) (AK55X2)

Parallel Mode, ODP pin = “H” :

PW0 pin

SW602_2

PW1 pin

SW602_3

PW2 pin

SW602_4

Power

ON/OFF Data on Slot

Ch2 Ch1 Slot 2 Slot 1

L L L OFF OFF All “0” All “0”

L L H ON ON (CH2+1)

/2

(CH2+1)

/2

L H L ON ON CH2 CH1

L H H ON ON All “0”

or TDMI

(CH2+1)

/2

H L L ON ON CH2 CH1

H L H ON ON (CH2+1)

/2

(CH2+1)

/2

H H L ON ON CH2 CH1

H H H ON ON All “0”

or TDMI

(CH2+1)

/2

Table 3-7-2-2. Channel Power & Mono Mode Select (ODP pin = “H”) (AK55X2)

- 13-

[AKD55X4-B]

<KM119202> 2015/09

CKS3 pin

SW603-4

CKS2 pin

SW603-3

CKS1 pin

SW603-2

CKS0 pin

SW603-1

MSN pin

SW602-5

MCLK

Frequency fs Range

L(0) L(0) L(0) L(0) L(0) 128fs

24M

Quad Speed Mode

108kHz fs 216kHz

H(1)

L(0) L(0) L(0) H(1) L(0) 192fs

36M

Quad Speed Mode

108kHz fs 216kHz

H(1)

L(0) L(0) H(1) L(0) L(0) 256fs

12M

Normal Speed Mode

8kHz fs 54kHz

H(1)

L(0) L(0) H(1) H(1) L(0) 256fs

24M

Double Speed Mode

54kHz fs 108kHz

H(1)

L(0) H(1) L(0) L(0) L(0) 384fs

36M

Double Speed Mode

54kHz fs 108kHz

H(1)

L(0) H(1) L(0) H(1) L(0) 384fs

18M

Normal Speed Mode

8kHz fs 54kHz

H(1)

L(0) H(1) H(1) L(0) L(0) 512fs

24M

Normal Speed Mode

8kHz fs 54kHz

default

H(1)

L(0) H(1) H(1) H(1) L(0) 768fs

36M

Normal Speed Mode

8kHz fs 54kHz

H(1)

H(1) L(0) L(0) L(0) L(0) 64fs

24M

Oct Speed Mode

fs = 384kHz

H(1)

H(1) L(0) L(0) H(1) L(0) 32fs

24M

Hex Speed Mode

fs = 768kHz

H(1)

H(1) L(0) H(1) L(0) L(0) 96fs

36M

Oct Speed Mode

fs = 384kHz

H(1)

H(1) L(0) H(1) H(1) L(0) 48fs

36M

Hex Speed Mode

fs = 768kHz

H(1)

H(1) H(1) L(0) L(0) L(0) 64fs

49.1M

Hex Speed Mode

fs = 768kHz

H(1)

H(1) H(1) L(0) H(1) L(0) 1024fs

32M

Normal Speed Mode

8kHz ≤fs ≤32kHz

H(1)

H(1) H(1) H(1) L(0) L(0) NA NA

H(1)

H(1) H(1) H(1) H(1) L(0) Auto 8kHz fs 216kHz

-

Table 3-8. MCLK Frequency Select (AK55X4/X2)

- 14-

[AKD55X4-B]

<KM119202> 2015/09

DSDSEL1 pin

SW603-6

DSDSEL0 pin

SW603-5

Frequency Mode DSD Sampling Frequency

fs=32kHz fs=44.1kHz fs=48kHz

L(0) L(0) 64fs 2.048MHz 2.8224MHz 3.072MHz default

L(0) H(1) 128fs 4.096MHz 5.6448MHz 6.144MHz

H(1) L(0) 256fs 8.192MHz 11.2896MHz 12.288MHz

H(1) H(1) - Reserved

(8.192MHz)

Reserved

(11.2896MHz)

Reserved

(12.288MHz)

Table 3-9. DSD Sampling Frequency Select (AK55X4/X2)

No. Multiplex

Mode

Speed

Mode

TDM1

SW604-4

TDM0

SW604-3

MSN

SW602-5

DIF1

SW603-6

DIF0

SW603-5 SDTO LRCK BICK MCLK

Pol. I/O Freq. I/O Freq. I/O

0

Normal

Normal

Double

Quad

L(0) L(0)

L(0)

L(0) L(0) 24-bit, MSB ↑I 48-128fs I 128-1024fs I

1 L(0) H(1) 24-bit, I2S↓I 48-128fs I 128-1024fs I default

2 H(1) L(0) 32-bit, MSB ↑I 64-128fs I 128-1024fs I

3 H(1) H(1) 32-bit, I2S↓I 64-128fs I 128-1024fs I

4

H(1)

L(0) L(0) 24-bit, MSB ↑O 64fs O 128-1024fs I

5 L(0) H(1) 24-bit, I2S↓O 64fs O 128-1024fs I

6 H(1) L(0) 32-bit, MSB ↑O 64fs O 128-1024fs I

7 H(1) H(1) 32-bit, I2S↓O 64fs O 128-1024fs I

8

OCT

HEX L(0) L(0)

L(0)

* L(0) 16-bit, MSB ↑I 32fs I 32-96fs I

9 * H(1) 16-bit, I2S↓I 32fs I 32-96fs I

10 * L(0) 24-bit, MSB ↑I 48fs I 32-96fs I

11 * H(1) 24-bit, I2S↓I 48fs I 32-96fs I

12 L(0) L(0) 24-bit, MSB ↑O 64fs O 32-96fs I

13 L(0) H(1) 24-bit, I2S↓O 64fs O 32-96fs I

14 H(1) L(0) 32-bit, MSB ↑O 64fs O 32-96fs I

15 H(1) H(1) 32-bit, I2S↓O 64fs O 32-96fs I

16

H(1)

* L(0) 16-bit, MSB ↑I 32fs I 32fs I

17 * H(1) 16-bit, I2S↓I 32fs I 32fs I

18 * L(0) 24-bit, MSB ↑I 48fs I 48fs I

19 * H(1) 24-bit, I2S↓I 48fs I 48fs I

20 L(0) L(0) 24-bit, MSB ↑O 64fs O 64fs I

21 L(0) H(1) 24-bit, I2S↓O 64fs O 64fs I

22 H(1) L(0) 32-bit, MSB ↑O 64fs O 64fs I

23 H(1) H(1) 32-bit, I2S ↓O 64fs O 64fs I

Table 3-10. Audio Interface Format Select ( Normal mode, OCT/HEX mode) : PCM Mode (AK55X4/X2)

- 15-

[AKD55X4-B]

<KM119202> 2015/09

No. Multiplex

Mode

Speed

Mode

TDM1

SW604-4

TDM0

SW604-3

MSN

SW602-5

DIF1

SW603-6

DIF0

SW603-5 SDTO LRCK BICK MCLK

Edg. I/O Freq. I/O Freq. I/O

24

TDM128

Normal

Double

Quad

L(0) H(1)

L(0)

L(0) L(0) 24-bit, MSB I 128fs I 128-1024fs I

25 L(0) H(1) 24-bit, I2SI 128fs I 128-1024fs I

26 H(1) L(0) 32-bit, MSB I 128fs I 128-1024fs I

27 H(1) H(1) 32-bit, I2SI 128fs I 128-1024fs I

28

H(1)

L(0) L(0) 24-bit, MSB O 128fs O 128-1024fs I

29 L(0) H(1) 24-bit, I2SO 128fs O 128-1024fs I

30 H(1) L(0) 32-bit, MSB O 128fs O 128-1024fs I

31 H(1) H(1) 32-bit, I2SO 128fs O 128-1024fs I

32

TDM256 Normal

Double H(1) L(0)

L(0)

L(0) L(0) 24-bit, MSB I 256fs I 256-1024fs I

33 L(0) H(1) 24-bit, I2SI 256fs I 256-1024fs I

34 H(1) L(0) 32-bit, MSB I 256fs I 256-1024fs I

35 H(1) H(1) 32-bit, I2SI 256fs I 256-1024fs I

36

H(1)

L(0) L(0) 24-bit, MSB O 256fs O 256-1024fs I

37 L(0) H(1) 24-bit, I2SO 256fs O 256-1024fs I

38 H(1) L(0) 32-bit, MSB O 256fs O 256-1024fs I

39 H(1) H(1) 32-bit, I2SO 256fs O 256-1024fs I

40

TDM512 Normal H(1) H(1)

L(0)

L(0) L(0) 24-bit, MSB I 512fs I 512-1024fs I

41 L(0) H(1) 24-bit, I2SI 512fs I 512-1024fs I

42 H(1) L(0) 32-bit, MSB I 512fs I 512-1024fs I

43 H(1) H(1) 32-bit, I2SI 512fs I 512-1024fs I

44

H(1)

L(0) L(0) 24-bit, MSB O 512fs O 512-1024fs I

45 L(0) H(1) 24-bit, I2SO 512fs O 512-1024fs I

46 H(1) L(0) 32-bit, MSB O 512fs O 512-1024fs I

47 H(1) H(1) 32-bit, I2SO 512fs O 512-1024fs I

Table 3-11. Audio Interface Format Select ( TDM mode) : PCM Mode (AK55X4/X2)

SD

SW603-8

SLOW

SW603-7

Filter

L L Sharp Roll-off Filter default

L H Slow Roll-off Filter

H L Short Delay Sharp Roll-off Filter

H H Short Delay Slow Roll-off Filter

Table 3-12. Digital Filter Select : PCM Mode (AK55X4/X2)

LDOE

SW604-1

PDN

SW600 LDO VDD18 pin TVDD pin

Power Supply

L L OFF External Power Supply 1.7~1.98V 1.7~1.98V

L H OFF External Power Supply 1.7~1.98V 1.7~1.98V

H L OFF Internal 500Pull Down 3.0~3.6V

H H ON LDO Power Output 3.0~3.6V default

Table 3-13. LDO Select (AK55X4/X2)

- 16-

[AKD55X4-B]

<KM119202> 2015/09

I2C pin

SW604-6

PS pin

SW604-5 Control Mode

L L 3-wire Serial

L H 3-wire Serial

H L I2C Bus default

H H Parallel

Table 3-14. Control Mode Select (AK55X4/X2)

- 17-

[AKD55X4-B]

<KM119202> 2015/09

[4] Toggle switches settings

Up=”H”, Down=”L”

[SW600] ( Power Down (PDN) for AK55X4/X2):

Power Down (PDN) Switch for AK55X4/X2

Reset AK55X4/X2 (U1) once by brining SW600 to “L” once upon power-up.

Keep “H” when AK55X4/X2 is in use; keep “L” when AK55X4/X2 is not in use.

[SW601] ( Power Down (PDN) for AK4118A):

Power Down (PDN) Switch for AK4118A

Reset AK4118A (U4) once by brining SW601 to “L” once upon power-up.

Keep “H” when AK4118A is in use; keep “L” when AK4118A is not in use.

- 18-

[AKD55X4-B]

<KM119202> 2015/09

[5] Register control (Serial control)

AKD55X4-A can be controlled printer port (parallel port).

Connect board to PC using 10-wire flat cable (PORT500 – serial uP-IF) included with the AKD55X4-A.

There is a mark on the no.1-pin of the 10-pin connector. See Figure 3..

The pin assignments of PORT below.

PORT700

uP I/F

1

2

9

10

GND

GND

GND

GND

GND

CSN

CCLK / SCL

CDTI / SDA

NC

NC

Figure 3. The pin assignments of PORT500

The control software is packed with the evaluation board. The software operation sequence is included in the

evaluation board manual.

- 19-

[AKD55X4-B]

<KM119202> 2015/09

[6] Evaluation modes

(6-1) ADC Differential Analog Input Connector ( 4ch/2ch Mode )

ADC

Channel Ch1 Ch2 Ch3 Ch4

4ch J200 J201 J300 J301

2ch J200 J201 - -

Table 6-1. Differential Analog Input Connector

(6-1-1) 4ch mode

1ch: Cannon connector = J200, 2ch: Cannon connector = J201

3ch: Cannon connector = J300, 4ch: Cannon connector = J301

(6-1-2) 2ch mode

1ch: Cannon connector = J200, 2ch: Cannon connector = J201

(6-2) ADC Master / Slave Mode

(6-2-1) Slave Mode

SW602-5 = “L” ( MSN pin = “L” )

(6-2-2) Matser Mode

SW602-5 = “H” ( MSN pin = “H” )

(6-3) ADC PCM / DSD Mode

(6-3-1) PCM Mode

SW602-5 = “L” ( MSN pin = “L” ), SW604-7 = “L” ( DP pin = “L” )

(6-3-2) DSD Mode

SW602-5 = “H” ( MSN pin = “H” ) , SW604-7 = “H” ( DP pin = “H” )

(6-4) ADC (Analog Digital) : PCM Mode, Slave Mode

Toggle switch setting:

SW600 SW601

L→H L→H

AK55X4/X2(U1) : Used AK4118A(U4) : Used

Table 6-2. Toggle switch setting

Start up Control Register Setting

1: Port Reset & Write Default.

2: Set Addr: 02h = “13” to Data and Clock format on ADC. Other control register settings are default.

Mode settings : Normal Speed Mode, 24bit, I2S, MCLK=256fs

DIF1-0: Audio Data Interface Modes Select (Table 3-5, Table 3-10)

CKS3-0: Sampling Speed Mode and MCLK Frequency Select (Table 3-5, Table 3-8)

Addr Register Name D7 D6 D5 D4 D3 D2 D1 D0

02H Control 1 CKS3 CKS2 CKS1 CKS0 DIF1 DIF0 HPFE

R/W R/W R/W R/W R/W R/W R/W R/W R/W

Default 0 0 0 0 0 0 0 1

Table 6-3. Addr 02H control register setting

- 20-

This manual suits for next models

2

Table of contents

Other ASAHI Motherboard manuals