beneq Lumineq EL320.240-FA3 User manual

EL320.240-FA3

Multi-Color

QVGA TFEL Display

Operation Manual

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 1

EL320.240-FA3

Operation Manual

Operation Manual

EL320.240-FA3 Display

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 2

Table of contents:

1EL320.240-FA3 multi-color QVGA display ................................................................................................ 3

1.1 Features and benefits .................................................................................................................... 3

2Installation and set-up.......................................................................................................................... 4

2.1 Mounting TFEL displays.................................................................................................................. 4

2.2 Cable length ................................................................................................................................. 4

2.3 Cleaning....................................................................................................................................... 4

2.4 Avoiding burn-in ........................................................................................................................... 4

2.5 Power supply and video sequencing and overcurrent protection .......................................................... 5

2.6 Internal frame buffer ..................................................................................................................... 5

2.7 Color bit-mapping and color considerations ...................................................................................... 5

2.8 Display overlay considerations ........................................................................................................ 6

3Specifications and operation .................................................................................................................. 7

3.1 Environmental .............................................................................................................................. 7

3.2 Over-temp condition...................................................................................................................... 7

3.3 Optical......................................................................................................................................... 8

3.3.1 Displayed colors .................................................................................................................... 8

3.4 Power ........................................................................................................................................ 10

3.5 Display interface ......................................................................................................................... 11

3.5.1 Video mode selection ........................................................................................................... 12

3.5.2 Connector........................................................................................................................... 13

3.5.3 Display input descriptions ..................................................................................................... 14

3.5.4 Video mode timing—SGD video mode..................................................................................... 15

3.5.5 Video mode timing—AMLCD video mode, QVGA....................................................................... 17

3.5.6 Video mode timing—AMLCD video mode, QVGA, fixed .............................................................. 18

3.5.7 Video mode timing—AMLCD video mode, VGA......................................................................... 19

3.5.8 Video mode timing—AMLCD video mode, VGA, fixed ................................................................ 20

3.6 Dimming .................................................................................................................................... 21

3.7 Self-test mode ............................................................................................................................ 22

3.8 Reliability ................................................................................................................................... 22

3.9 Safety and EMI performance......................................................................................................... 22

3.10 Mechanical characteristics ............................................................................................................ 23

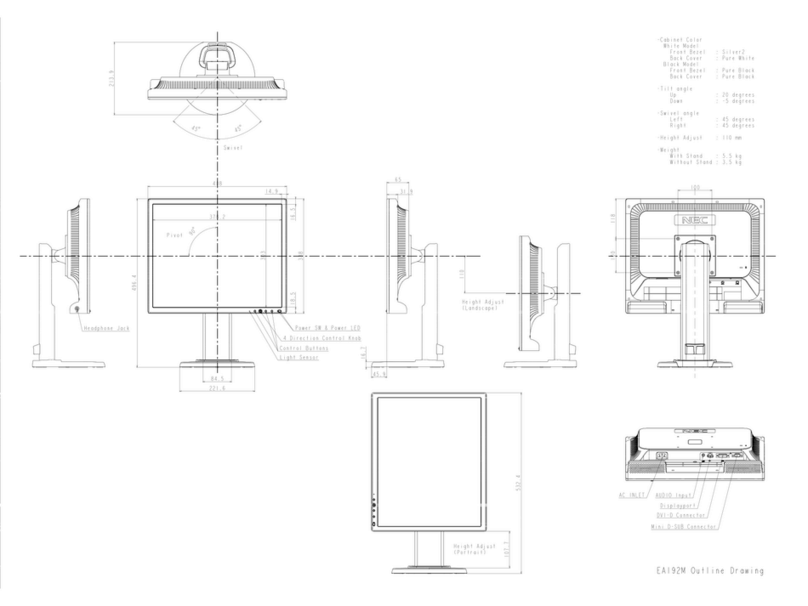

3.10.1 Display dimensions and component envelope .......................................................................... 23

4Description of warranty....................................................................................................................... 25

5Ordering information .......................................................................................................................... 25

6Support and service............................................................................................................................ 26

7RoHS II............................................................................................................................................. 26

Operation Manual

EL320.240-FA3 Display

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 3

1EL320.240-FA3 multi-color QVGA display

The EL320.240-FA3 thin film electroluminescent (TFEL) multi-color display is a high-

performance alternative to QVGA (320 x 240) LCDs and the ideal solution in demanding

applications where superior visual performance, extreme temperature range, and

environmental ruggedness are critical.

The EL320.240-FA3 utilizes Lumineq®Displays’ proprietary Integral Contrast Enhancement

(ICEBrite™) technology combined with red and green filters patterned over Lumineq Displays’

industry-leading yellow phosphor to achieve unparalleled image quality in hues of red, green

and yellow. Three intensity levels in each of the red and green sub-pixels generate 16 distinct

colors (9 chromatically different colors, black, and 2 mid-levels of red, green, and yellow.)

The display consists of a solid state TFEL glass panel, depicted below, with a 124 mm

diagonal active area, and control electronics assembled into a space-saving, rugged package

for easy mounting.

1.1 Features and benefits

Excellent visual performance:

Unparalleled crisp, clear image

Excellent contrast

Unbeatable viewing angle of > 179° for all colors in all directions

No off-axis color or contrast shift

Extremely wide operation temperature range: -50˚C to 85 °C

Instant turn on at -50 °C: no heaters needed, no warm up time

Long life phosphor: allows >11 years of continuous operation

Wide dimming range via digital control and analog voltage input

Rugged solid state construction

Great reliability: MTBF > 50,000 hours demonstrated

Low cost of ownership: no maintenance, no lamps to replace

AMLCD-type panel interface, 3 V and 5 V logic compatible

RoHS compliance

Operation Manual

EL320.240-FA3 Display

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 4

2Installation and set-up

Do not drop, bend, or flex the display. Do not allow objects to strike the surface of the

display.

CAUTION: The display uses CMOS and devices. These components are electrostatic-

sensitive. Unpack, assemble, and examine this assembly in a static-controlled area only.

When shipping, use packing materials designed for protection of electrostatic-sensitive

components.

2.1 Mounting TFEL displays

Properly mounted, TFEL displays can withstand high shock loads as well as severe vibration

found in demanding applications. However, the glass panel used in a TFEL display will break if

subjected to bending stresses, high impact, or excessive loads.

Avoid bending the display. Stresses are often introduced when a display is mounted into a

product. Ideally, the mounting tabs of the display should be the only point of contact with the

system. Use a spacer or boss for support; failure to do so will bend the display and cause the

glass to break. The instrument enclosure or frame should not flex or distort in such a way

that the bending loads might be transferred to the display during use. The EL320.240-FA3

mounting tabs are designed for 3 mm screws. Mounting surfaces should be flat to within

±0.6 mm (±0.025"). Use all the mounting holes provided. Failure to do so will impair the

shock and vibration resistance of the final installation.

WARNING: These products generate voltages capable of causing personal injury (high

voltage up to 235 VAC). Do not touch the display electronics during operation.

2.2 Cable length

A cable length of 0.5 m (20 inches) or less is recommended. Longer cables may cause visual

artifacts, such as pixel “jitter”, due to data transfer problems between the host and the

display.

2.3 Cleaning

As with any glass surface, care should be taken to minimize scratching. Clean the display

glass with mild, water-based detergents only. Apply the cleaner sparingly to a soft cloth, then

wipe the display. Disposable cleaning cloths are recommended to minimize the risk of

inadvertently scratching the display with particles embedded in a re-used cloth.

2.4 Avoiding burn-in

As with other light-emitting displays, displaying fixed patterns on the screen may cause burn-

in where luminance variations can be noticed after many hours of operation. To avoid image

burn-in, use a screensaver or use periodic image inversion, if possible. Note that the rate of

image burn-in will slow over time so that most of the burned-in image effect occurs in the

first few hundred hours of operation.

Operation Manual

EL320.240-FA3 Display

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 5

2.5 Power supply and video sequencing and overcurrent protection

Any combination or sequencing in the application or removal of VH(12 VDC input power)

and/or video signals will not result in abnormal display operation or display failure.

There is no overcurrent protection on VH, the 12 V power input. To protect against

catastrophic faults, Beneq recommends the use of a fuse or similar protection on the VHinput

to the display.

2.6 Internal frame buffer

This display includes an internal frame buffer, which is required to transform the incoming

video data into the desired displayed data. The display frame rate (the rate at which the

phosphor is scanned) and thus the display brightness are independent of the frame rate of

the user-supplied input data. Video data need not be continuously sent to the display since

previously sent data is stored indefinitely until new data is received.

CAUTION: Some third-party video controllers use frame dithering algorithms to produce

gray scale images. If such algorithms are used, the internal frame buffer may cause

objectionable visual artifacts.

2.7 Color bit-mapping and color considerations

The EL320.240-FA3 utilizes standard AMLCD-type video interface timing. Thus, it is possible

that a video source will be chosen. This provides 18 bits of data per pixel (6 bits each for red,

green, and blue) as is common for AMLCD displays. Because the EL320.240-FA3 requires just

4 bits (two each for red and green) of data per pixel, the 18 bits would need to be mapped

into 4 bits.

One option is to use just the two most significant bits of red and green and leave the rest

open or terminated. This is the easiest approach and will work well if the user is developing

their own content and can refrain from using patterns containing dim colors since these

would be displayed as black. Another option is to electrically “OR” the 3 red MSBs together

and route the result to R1, OR the 3 red LSBs together and route to R0, and do the same for

G1 and G0. Additionally, the bits of blue could be ORd together with either the red or green

bits depending on the characteristics of the images that need to be displayed.

If upgrading from a monochrome EL320.240 display model and using the SGD timing mode,

some engineering effort will be required to map the monochrome SGD data into the color

data required by the EL320.240-FA3. SGD data is one bit per pixel, and 4 pixels of data are

latched per video clock edge. The EL320.240-FA3 is 4 bits per pixel with one pixel of data

latched per clock edge.

Note that care must be taken when selecting colors for a given application to ensure that the

selected colors are differentiated as desired. Although all fifteen colors and black are unique,

some color levels are similar in chromaticity and/or luminance and typically should not be

used together.

Operation Manual

EL320.240-FA3 Display

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 6

The colors in the following “color sets” are distinct but visually similar to each other: 1 & 2, 3

& 7, 4 & 8, 7 & 11, 5 & 6 & 9 & 10, and 13 & 14. For details, see the “Displayed colors”

section of this manual.

In applications where the display is subject to physical motion or vibration, visual artifacts

due to the gray scale frame dithering algorithm become more visible, especially in large

blocks of color. For best results, use colors with no gray scale or 2/3 gray scale and the

highest frame rate setting.

The following table lists the color levels which are dramatically distinct and most suitable for

general use:

Color level

Color description

Similar color levels

3

Green

7

2

Medium Green

1

12

Red

None

8

Medium Red

4

15

Yellow

None

13

Orange

14

9

Brown Mustard

5, 6, and 10

11

Bright Neon Green

7

0

Black

None

2.8 Display overlay considerations

Though not a requirement, often the end system will employ some type of transparent cover

over the front the display. The purpose and construction of the cover varies depending on the

application and economical constraints. The cover may be used to improve contrast under

certain lighting conditions by reducing reflections, to provide additional impact protection, to

provide a more seamless enclosure appearance, or to protect against fluids. Some leading

suppliers of display overlays are: EyeSaver International, Cyro Industries, and Dontech

Incorporated.

Operation Manual

EL320.240-FA3 Display

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 7

3Specifications and operation

3.1 Environmental

Environmental characteristics

Temperature

Operating

-50 °C to +85 °C

Storage

-50 °C to +105 °C

Humidity

Non-condensing, operating

93 % RH max at +40 °C, per IEC 60068-2-78

Condensing, non-operating

95 % RH max at +55 °C, per IEC 60068-2-30

Altitude

Operating/non-operating

0 to 18 km (58k ft) per IEC 60068-2-13

Vibration

Random

0.05 g2/Hz, ASD level, 5-500 Hz per IEC 60068-2-64,

Test Fh.

Operating/non-operating

Shock

Operating/non-operating

100 g, 6 ms, half sine wave on each of six surfaces per

IEC 60068-2-27, test Ea.

3.2 Over-temp condition

The display contains a temperature sensor which measures the temperature of the circuit

board at the lower left corner as viewed from the component side of the board.

If the board temperature exceeds approximately 100 °C, the display will automatically

operate at its lowest luminance setting (as if LUM0 was low and LUM1 was high) to reduce

the board temperature. At no point will the display be shut down. The content of the pattern

will be unaffected.

After surpassing 100 °C, once the board temperature drops below approximately 92 °C (or

the power is cycled), the display will resume normal operation as defined by the LUM0 and

LUM1 settings. Typically, the 100 °C limit may be reached if the 12 V input power exceeds 6

W with the ambient temperature for the display electronics above 80 °C.

Operation Manual

EL320.240-FA3 Display

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 8

3.3 Optical

Optical characteristics

Luminance

Guaranteed

> 75 cd/m²

max frame rate (LUM0=LUM1=0), yellow, center

Typical

95 cd/m²

max frame rate (LUM0=LUM1=0), yellow, center

Guaranteed

> 41 cd/m²

min frame rate (LUM0=0, LUM1=1), yellow, center

Typical

53 cd/m²

min frame rate (LUM0=0, LUM1=1), yellow, center

Black luminance

< 0.2 cd/m²

max frame rate, 5 points: center plus four corners

Luminance non-uniformity

Typical

5%

Max difference of two of five points (center plus four

corners)

Luminance variation across temperature

Maximum

15%

Variation from 25 °C to the operating extremes

Luminance decrease over time

Typical

6%

After 10,000 hours

Typical

15%

After 100,000 hours (> 11 years)

Viewing angle

Minimum

>160in all directions; no change to contrast, color, or luminance

Contrast ratio

Typical

1000:1

@ 0 lux ambient (dark room), maximum frame rate

2.5:1

@ 20k lux ambient (daylight), maximum frame rate

1.5:1

@ 75k lux ambient (direct sun), maximum frame rate

3.3.1 Displayed colors

The display can generate 16 colors based on red and green sub-pixels and frame dithering

(utilizing a three frame period with either a 33% or 66% duty cycle.) Note that the colors in

the following “color sets”are distinct but similar to each other in appearance: 1 & 2, 3 & 7, 4

& 8, 7 & 11, 5 & 6 & 9 & 10, and 13 & 14.

Operation Manual

EL320.240-FA3 Display

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 9

Color

level

R1

R0

G1

G0

Pixel color

description

Typical

chromaticity

(x, y coordinates)

FA1 red

intensity

FA1

green

intensity

0

0

0

0

0

Black

n/a

Off

Off

1

0

0

0

1

Dim Green

.450,.546

Off

1/3

2

0

0

1

0

Medium

Green

.450,.546

Off

2/3

3

0

0

1

1

Green

.450,.546

Off

On

4

0

1

0

0

Dim Red

.606,.393

1/3

Off

5

0

1

0

1

Dim Yellow

Brown

.497,.498

1/3

1/3

6

0

1

1

0

Greenish

Brown

.481,.514

1/3

2/3

7

0

1

1

1

Neon Green

.471,.524

1/3

On

8

1

0

0

0

Medium Red

.606,.393

2/3

Off

9

1

0

0

1

Brown

Mustard

.524,.473

2/3

1/3

10

1

0

1

0

Yellow

Brown

.497,.498

2/3

2/3

11

1

0

1

1

Bright Neon

Green

.480,.521

2/3

On

12

1

1

0

0

Red

.606,.393

On

Off

13

1

1

0

1

Orange

.535,.462

On

1/3

14

1

1

1

0

Bright

Orange

.511,.485

On

2/3

15

1

1

1

1

Yellow

.497,.498

On

On

Operation Manual

EL320.240-FA3 Display

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 10

3.4 Power

The supply voltage and power requirements are shown in the table below. The power will

vary greatly depending on the number of pixels lit and the chosen luminance level (see graph

below.) Power levels will vary up to +/-15% from display to display due to brightness

variation.

Table 1. Supply voltage and power requirements

Parameter

Minimum

Typical

Maximum

Abs

max

Display supply voltage, VH

8 V

12 V

18 V

Supply current, with VH= 8 V

0.59 A

1.16 A

1.44 A

Supply current, with VH= 12 V

0.39 A

0.78 A

0.96 A

Power consumption @ maximum

luminance (LUM0=LUM1=0)

4.7 W

9.3 W

11.5 W

Power consumption @ minimum

luminance (LUM0=0, LUM1 =1)

3.1W

6 W

Quiescent power consumption

(SHUTDOWN = 1)

0.5 W

Note:

1) Maximum power condition: 80% of pixels lit (yellow) per row

2) Abs Max power: 80% of pixels lit (yellow) per row, worst case display sample

2) Typical power: pattern with 10% of pixels lit (yellow) per row, typical display

3) All power numbers are for LUMA open (no analog dimming)

Operation Manual

EL320.240-FA3 Display

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 11

3.5 Display interface

The display supports 5 video interface modes: SGD timing as used on the Beneq

EL320.240.36-HB (though with video data differences to denote colors) and the 4 AMLCD

timing modes used on Sharp and Kyocera QVGA color displays (though using only 2 bits of

red and green data). 4 bits of data per pixel are provided. The data is clocked to the display

with a video clock, VCLK. Frame and line synchronization is provided by the VS, HS, and (if

needed) DE signals.

Video mode detection is performed automatically. The display evaluates the timing of the

incoming video approximately every 25 ms and will shift “on the fly” between video modes as

required.

The internal display controller utilizes a frame buffer to provide the display with the

appropriate modulation on a line-by-line and frame-by-frame basis to implement the color

generation, including frame dithering algorithms. Thus, the input frame rate and the display

scan rate, in general, will not be the same and will not be synchronous.

EL320.240-FA3 Power vs. Percent of Pixels On, for All Three

Luminance Settings, Typical

0

1

2

3

4

5

6

7

8

9

10

020 40 60 80 100

Percentage of pixels turned on (yellow) per row

Power Consumption, watts

Max luminance, 325 Hz

Med luminance, 240 Hz

Min luminance, 180 Hz

Operation Manual

EL320.240-FA3 Display

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 12

3.5.1 Video mode selection

Inputs LUM0 and LUM1 must be set to attain the desired video mode as shown in the

following table.

LUM0 and

LUM1 = 1?

V/Q

input

DE

input

Mode

name

Mode description

(refer to video mode timing for details)

No

0

Active

AMLCD,

QVGA

AMLCD timing. DE determines the

horizontal location of data.

No

0

0

AMLCD,

QVGA,

Fixed

AMLCD timing. Horizontal start of valid data

is a predetermined number of VCLKs from

HS.

No

1

Active

AMLCD,

VGA

AMLCD timing. Displays the upper left

quadrant of a VGA (640x480) input signal

with DE determining the horizontal location

of data.

No

1

0

AMLCD,

VGA,

Fixed

AMLCD timing. Displays the upper left

quadrant of a VGA (640x480) input signal

with the horizontal start of valid data

predetermined.

No

X

1

SGD

SGD timing. Horizontal start of valid data is

the first VCLK after HS.

Yes

X

X

Self test

Displays various patterns at the maximum

refresh rate regardless of video input data.

Useful for verifying display functionality.

Note:

1) DE is considered active if more than 8 logic transitions are detected.

2) SGD mode is similar to that of the Lumineq EL320.240.36 and EL320.240-HB displays, but

with required changes to the video data content to represent color.

3) The AMLCD modes are compatible with those found on the following QVGA displays though

the video data content of 4 bits/pixel is a subset of the typical 18 bits/pixel: Sharp

LQ057Q3DC12, Sharp LQ057Q3DC02, Kyocera TCG057QV1AC.

Operation Manual

EL320.240-FA3 Display

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 13

3.5.2 Connector

The display uses the Samtec EHT-110-01-S-D or equivalent 2 mm locking connector. The

mating connector is in the Samtec TCSD family of cable strips. The proper connector, user-

specified cable length and connector configuration is supplied as a single unit. Consult your

Samtec representative for the cable/connector options. Compatibility with non-Samtec

equivalents should be verified before use.

Figure 1. Data/power connector

Table 2. J1 Connector pin assignment

Signal

Pin

Pin

Signal

VH

1

2

VH

V/Q

3

4

DE

LUMA

5

6

LUM0

VS

7

8

LUM1

HS

9

10

GND

VCLK

11

12

GND

R0

13

14

GND

R1

15

16

GND

G0

17

18

GND

G1

19

20

SHUTDOWN

J1

Pin 1

Pin 19 Pin 1

Pin 2

Key

(Viewed from top of connector)

(Viewed from back of display)

Operation Manual

EL320.240-FA3 Display

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 14

3.5.3 Display input descriptions

Signal

Description

VH

Power supply voltage for display functions. 12 VDC nominal.

V/Q

Format selection: in AMLCD timing modes, selects between VGA mode

(high) and QVGA mode. In VGA mode, the upper left quadrant of data will

be displayed. Internally pulled low.

DE

Data Enable: in AMLCD non-fixed timing modes, the rising edge identifies

the data for the first pixel of each row and must stay high until the data

for the last pixel of each row is clocked. DE is also used to determine the

video timing mode. Internally pulled high to 3.3 V.

LUMA

Analog Luminance Control: used to reduce the display luminance by

reducing the voltage applied to the display phosphor. If left open, defaults

to the luminance set by LUM0 and LUM1.

LUM0, LUM1

Digital Luminance Controls: used to reduce the luminance of the display

by reducing the frequency at which the display is scanned.

VS

Vertical Sync: identifies the start of each frame (entire screen) of data.

Internally pulled low.

HS

Horizontal Sync: identifies the start of each horizontal row of data.

VCLK

Video Clock: the falling edge latches the video data (R0, R1, G0, and G1).

R0

Video data: Least significant bit for red sub-pixel.

R1

Video data: Most significant bit for red sub-pixel.

G0

Video data: Least significant bit for green sub-pixel.

G1

Video data: Most significant bit for green sub-pixel.

SHUTDOWN

Display Shutdown: when high, will disable the display, thus rendering the

display black and minimizing power. All display data will be stored but no

new data accepted when SHUTDOWN is high. Internally pulled low.

GND

Signal return for power and logic.

Operation Manual

EL320.240-FA3 Display

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 15

Table 3. Logic signal requirements

Description

Min

Max

Units

Notes

Absolute input logic voltage

range

-0.3

5.5

V

For all inputs except VH,

LUMA

Logic high voltage

2.0

5.5

V

All input thresholds are TTL

Logic low voltage

-0.3

0.8

V

All input thresholds are TTL

LUMA input voltage

0

5.5

V

Leave open if not used

LUMA input current

-250

0

µA

Note:

1. All logic inputs (except LUMA input) are 5 V tolerant, with 270 Ωseries resistors.

2. Input capacitance for all logic inputs except LUMA is 8 pF typical.

3. DE, LUM0, and LUM1 have > 20 kΩpull-up resistors to 3.3 V.

4. VS, SHUTDOWN, and V/Q have > 20 kΩ pull-down resistors to ground

3.5.4 Video mode timing—SGD video mode

Item

Description

Min.

Max.

Units

1

HS high time

30

ns

2

Last VCLK fall to HS fall

20

ns

3

HS to VCLK rising edge

10

ns

4

R/G data setup to VCLK

10

ns

5

R/G data hold from VCLK

10

ns

6

VCLK period

100

ns

7

VCLK low width

30

ns

8

VCLK high width

30

ns

9

VS high setup to HS low

140

ns

10

VS hold after HS

140

ns

11

VS low setup to HS high

140

ns

12

HS period

34

µs

VS period

240

HS periods

VS frequency

120

Hz

Operation Manual

EL320.240-FA3 Display

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 16

Notes:

1) The first HS falling edge occurring when VS is high indicates the first row.

2) The video data for a given row is clocked in prior to the falling edge of HS.

3) The first 320 VCLK falling edges after the fall of HS clock in the valid data.

4) If video inputs are halted, the previously clocked in data will be displayed.

5) Video frame dithering/gray scale may cause artifacts due to the frame buffer.

6) All timing measurements are made at 1.6 V.

10

HS

VCLK

R/G data

VS

HS

First Line of

Pixel Data

Horizontal Timing

Vertical Timing

Data for First Pixel

Second Line of Pixel Data

8

7

9

11

1

2

4

5

6

3

10

Operation Manual

EL320.240-FA3 Display

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 17

3.5.5 Video mode timing—AMLCD video mode, QVGA

Item

Description

Min.

Max.

Units

1

HS low time

2

200

VCLK periods

2

HS to VCLK phase difference

10

VCLK period - 10

ns

3

HS to DE phase difference

2

HS period - 340

VCLK periods

4

DE set up time

5

VCLK period - 10

ns

5

VCLK frequency

7

MHz

6

R/G data set up to VCLK

5

ns

7

R/G data hold from VCLK

10

ns

8

VS low width

2

34

HS periods

9

VS to HS phase difference

0

HS period –HS low time

ns

10

Vertical start position

After 7 HS rising edges

DE high time

2

HS period - 10

VCLK periods

HS period

50

µs

VS period

251

280

HS periods

HS

VCLK

R/G data

VS

HS

Horizontal Timing

Vertical Timing

data for first pixel

9

8

6

7

5

10

1

horizontal invalid data period

DE

3

4

R/G data

vertical invalid data period

data for first line

Line 1

Line 2

Line N

2

Operation Manual

EL320.240-FA3 Display

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 18

3.5.6 Video mode timing—AMLCD video mode, QVGA, fixed

Item

Description

Min.

Max.

Units

1

HS low time

2

200

VCLK periods

2

HS to VCLK phase difference

10

VCLK period - 10

ns

5

VCLK frequency

7

MHz

6

R/G data set up to VCLK

5

ns

7

R/G data hold from VCLK

10

ns

8

VS low width

2

34

HS periods

9

VS to HS phase difference

0

HS period –HS low time

ns

10

Vertical start position

After 7 HS rising edges

HS period

50

µs

VS period

251

280

HS periods

HS

VCLK

R/G data

VS

HS

Horizontal Timing

Vertical Timing

data for first pixel

9

8

6

7

5

10

1

horizontal invalid data period

clock edge C1

first valid clock =

clock edge C52

R/G data

vertical invalid data period

data for first line

Line 1

Line 2

Line N

2

Operation Manual

EL320.240-FA3 Display

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 19

3.5.7 Video mode timing—AMLCD video mode, VGA

Item

Description

Min.

Max.

Units

1

HS low time

2

200

VCLK periods

2

HS to VCLK phase difference

10

VCLK period - 10

ns

3

HS to DE phase difference

44

HS period - 664

VCLK periods

4

DE set up time

5

VCLK period - 10

ns

5

VCLK frequency

28.33

MHz

6

R/G data set up to VCLK

5

ns

7

R/G data hold from VCLK

10

ns

8

VS low width

2

34

HS periods

9

VS to HS phase difference

0

HS period –HS low time

ns

10

Vertical start position

After 34 HS rising edges

DE high time

2

HS period - 10

VCLK periods

HS period

30

µs

VS period

515

560

HS periods

HS

VCLK

R/G data

VS

HS

Horizontal Timing

Vertical Timing

data for first pixel

9

8

6

7

5

10

1

horizontal invalid data period

DE

3

4

R/G data

vertical invalid data period

data for first line

Line 1

Line 2

Line N

2

Operation Manual

EL320.240-FA3 Display

Beneq Oy

Olarinluoma 9

Tel. +358 9 7599 530

VAT ID FI19563372

FI-02200 Espoo

Fax +358 9 7599 5310

www.beneq.com

Finland

lumineq@beneq.com

www.lumineq.com

Date: February 13, 2017

Document number: ED000813B

Page | 20

3.5.8 Video mode timing—AMLCD video mode, VGA, fixed

Item

Description

Min.

Max.

Units

1

HS low time

2

200

VCLK periods

2

HS to VCLK phase difference

10

VCLK period - 10

ns

5

VCLK frequency

28.33

MHz

6

R/G data set up to VCLK

5

ns

7

R/G data hold from VCLK

10

ns

8

VS low width

2

34

HS periods

9

VS to HS phase difference

0

HS period –HS low time

ns

10

Vertical start position

After 34 HS rising edges

HS period

30

µs

VS period

515

560

HS periods

HS

VCLK

R/G data

VS

HS

Horizontal Timing

Vertical Timing

data for first pixel

9

8

6

7

5

10

1

horizontal invalid data period

clock edge C1

first valid clock =

clock edge C104

R/G data

vertical invalid data period

data for first line

Line 1

Line 2

Line N

2

Table of contents

Other beneq Monitor manuals