— 2 —

SPECIFICATIONS

GENERAL

Keyboard: 61 standard-size keys, 5 octaves (with touch response on/off; ExLight/

Light/Normal/Heavy touch)

Tones: 232 (128 General MIDI, 64 variation, 8 drum, 32 user); with layer and

split

Rhythm instrument tones: 53

Polyphony: 32 notes maximum (16 for certain tones)

Digital effects: 10 (REVERB 1, 2, 3; CHORUS; TREMOLO; PHASE SHIFTER; OR-

GAN SPEAKER; ENHANCER; FLANGER; EQ LOUDNESS)

Auto accompaniment

Rhythm patterns: 110 (100 + 10 user rhythms)

Tempo: Variable (226 steps, = 30 to 255)

Chords: 3 fingering methods (CASIO CHORD, FINGERED, FULL RANGE

CHORD)

Rhythm controller: Start/Stop, Intro, Normal/Normal Fill-In, Variation/Variation Fill-In,

Synchro/Ending

Accomp volume: 0 to 127 (128 steps)

One touch presets: Recalls settings for tone, tempo, layer, and Auto Harmonize in accor-

dance with rhythm.

Auto harmonize: Automatic addition of notes that harmonize with melody note in ac-

cordance with specified Auto Accompaniment chords.

Free session

Number of patterns: 100 (Auto Accompaniment function based on preset chord progres-

sions.)

Song sequencer

Songs: 2

Recording tracks: 6 (2 through 6 are melody tracks)

Recording method: Real-time

Memory capacity

(total for two songs): Approximately 4,900 notes

Punch in: Supported

Pattern sequencer

Number of patterns: 10 (Rhythm numbers 100 to 109)

Memory capacity: Approximately 7,000 notes

Elements: Intro, Normal, Variation, Normal Fill-In, Variation Fill-In, Ending

Parts: Chord 1, 2, 3; Bass; Rhythm

Recording method: Real-time

Registration memory

Number of setups: 20 (5 setups ×4 banks)

Memory contents: Tone, Rhythm, Tempo, Split on/off, Split point, Layer on/off,Auto Har-

monize on/off, Mixer settings, Keyboard channel on/off, DSP (digital

effect) on/off, DSP (digital effect) settings, Accompaniment mode,

Touch Response settings, Assignable jack setting, Transpose, Tun-

ing, Pitch Bend range, Sound range shift on/off

Demo tunes: 2

Synthesizer

Parameters: PCM set, amp envelope set, attack rate, release rate, pitch envelope

set, pitch, level, touch sensitivity, pan, filter sensitivity, filter level, trans-

pose

Mixer Channels: 16

Modes: Internal, External, External/Solo, External/Play

Parameters: Program change number, volume, expression, pan, coarse tuning,

fine tuning, Effect Send

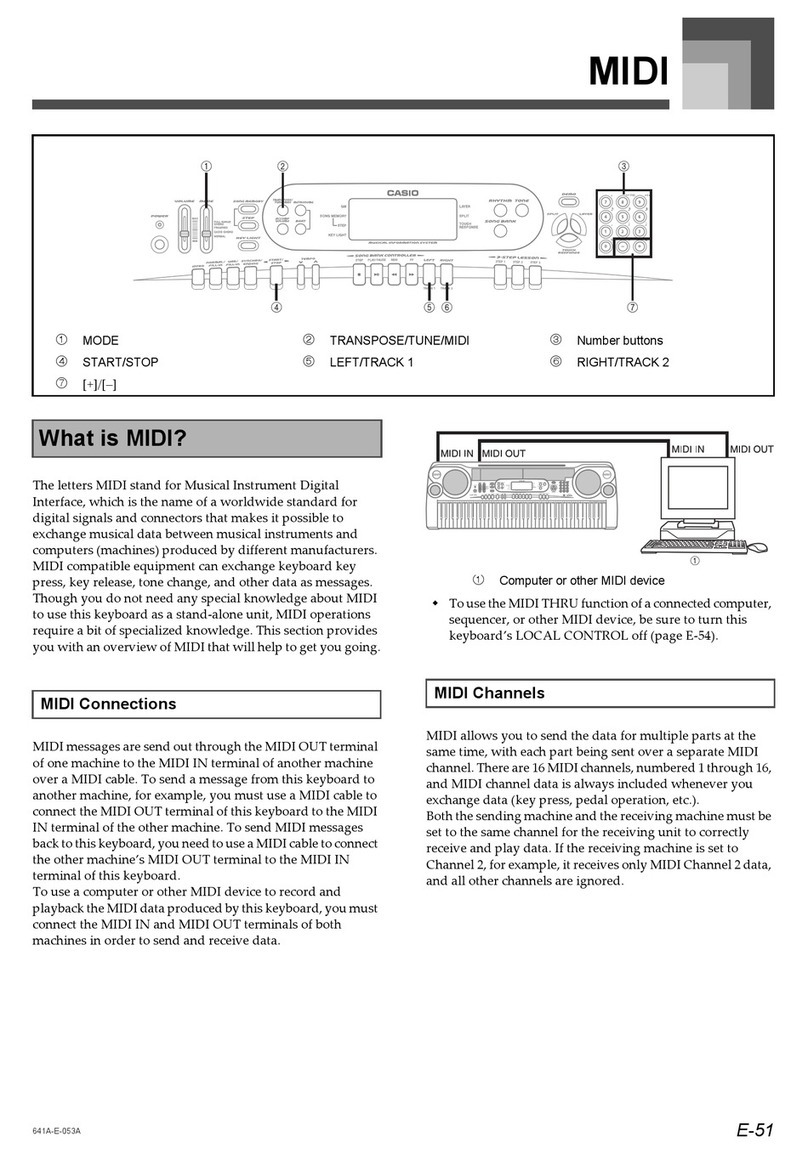

MIDI: 16-channel multi-timbre receive, General MIDI Level 1