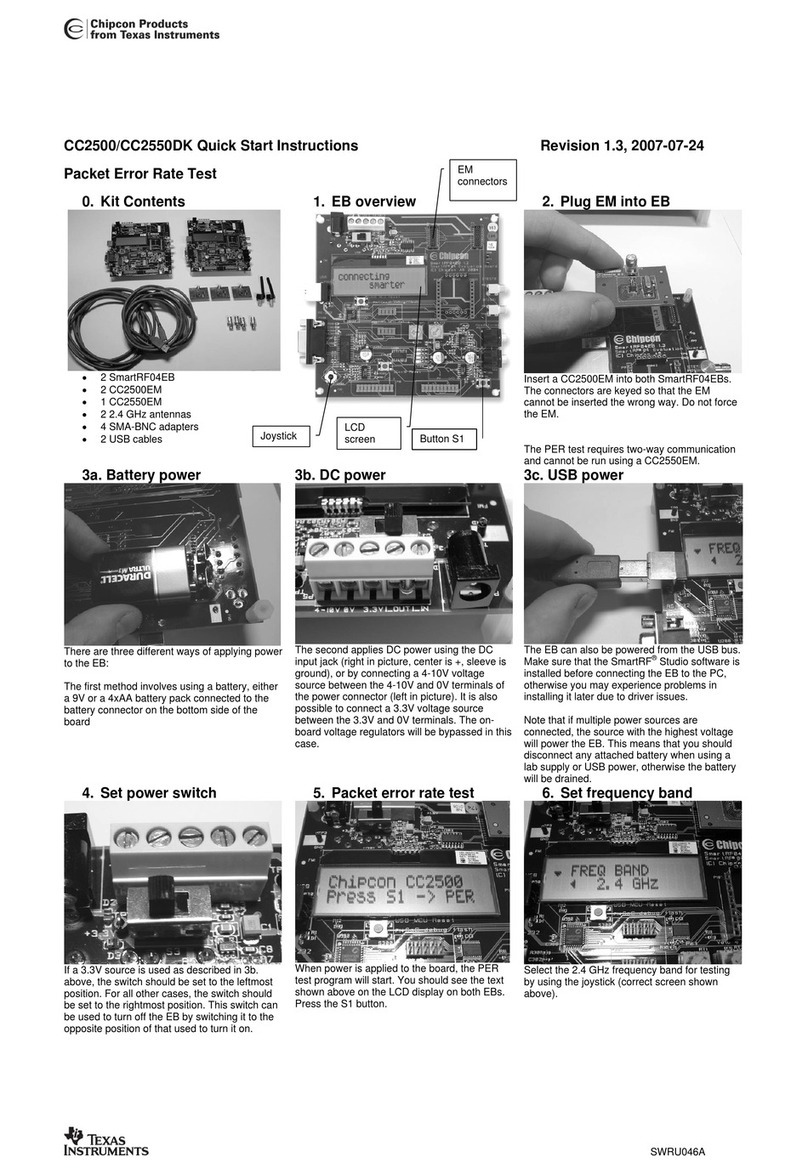

Chipcon CC2500 User manual

CC2500

SWRS040B Page 1 of 92

CC2500

Low-Cost Low-Power 2.4 GHz RF Transceiver

Applications

•2400-2483.5 MHz ISM/SRD band systems

•Consumer electronics

•Wireless game controllers

•Wireless audio

•Wireless keyboard and mouse

•RF enabled remote controls

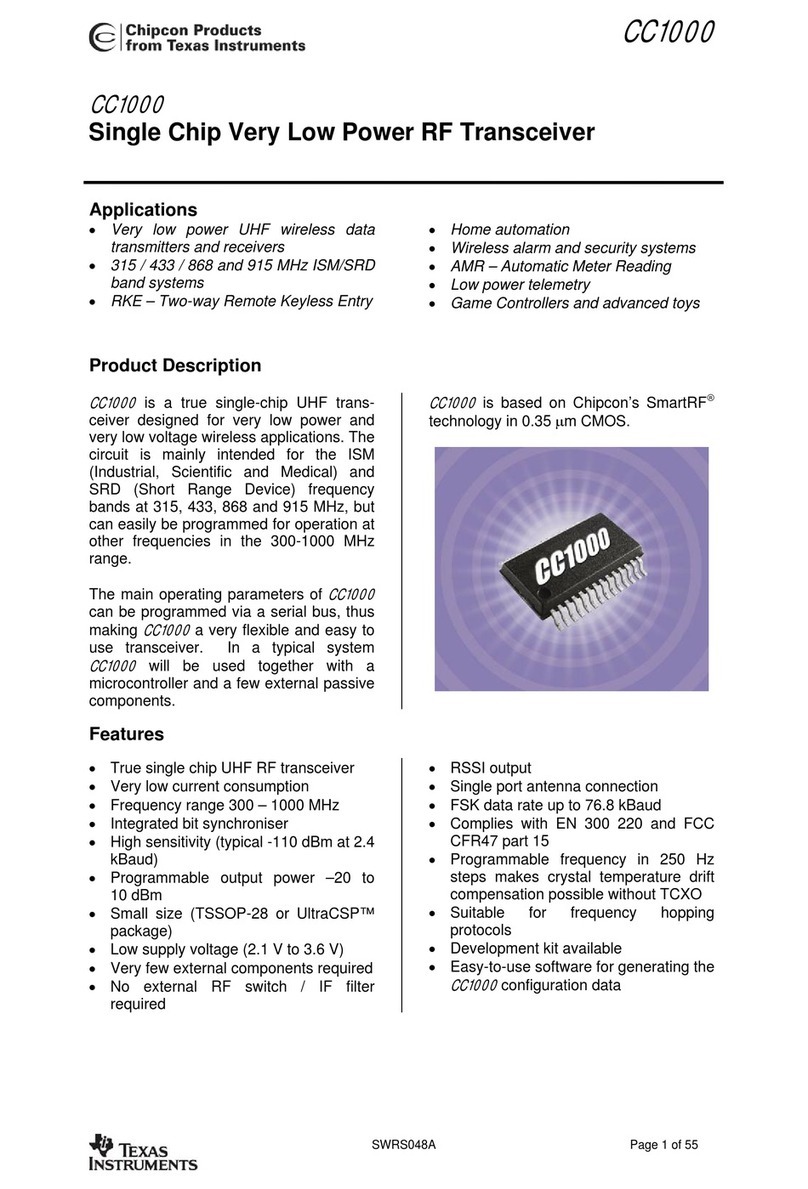

Product Description

The

CC2500

is a low-cost 2.4 GHz transceiver

designed for very low-power wireless appli-

cations. The circuit is intended for the 2400-

2483.5 MHz ISM (Industrial, Scientific and

Medical) and SRD (Short Range Device)

frequency band.

The RF transceiver is integrated with a highly

configurable baseband modem. The modem

supports various modulation formats and has

a configurable data rate up to 500 kBaud.

CC2500

provides extensive hardware support

for packet handling, data buffering, burst

transmissions, clear channel assessment, link

quality indication, and wake-on-radio.

The main operating parameters and the 64-

byte transmit/receive FIFOs of

CC2500

can be

controlled via an SPI interface. In a typical

system, the

CC2500

will be used together with

a microcontroller and a few additional passive

components.

6

7

8

9

10

20

19

18

17

16

Key Features

RF Performance

•High sensitivity (–104 dBm at 2.4 kBaud,

1% packet error rate)

•Low current consumption (13.3 mA in RX,

250 kBaud, input well above sensitivity

limit)

•Programmable output power up to +1 dBm

•Excellent receiver selectivity and blocking

performance

•Programmable data rate from 1.2 to 500

kBaud

•Frequency range: 2400 – 2483.5 MHz

Analog Features

•OOK, 2-FSK, GFSK, and MSK supported

•Suitable for frequency hopping and multi-

channel systems due to a fast settling

frequency synthesizer with 90 us settling

time

•Automatic Frequency Compensation

(AFC) can be used to align the frequency

synthesizer to the received centre

frequency

•Integrated analog temperature sensor

Digital Features

•Flexible support for packet oriented

systems: On-chip support for sync word

detection, address check, flexible packet

length, and automatic CRC handling

•Efficient SPI interface: All registers can be

programmed with one “burst” transfer

•Digital RSSI output

•Programmable channel filter bandwidth

•Programmable Carrier Sense (CS)

indicator

CC2500

SWRS040B Page 2 of 92

•Programmable Preamble Quality Indicator

(PQI) for improved protection against false

sync word detection in random noise

•Support for automatic Clear Channel

Assessment (CCA) before transmitting (for

listen-before-talk systems)

•Support for per-package Link Quality

Indication (LQI)

•Optional automatic whitening and de-

whitening of data

Low-Power Features

•400 nA SLEEP mode current consumption

•Fast startup time: 240 us from SLEEP to

RX or TX mode (measured on EM design)

•Wake-on-radio functionality for automatic

low-power RX polling

•Separate 64-byte RX and TX data FIFOs

(enables burst mode data transmission)

General

•Few external components: Complete on-

chip frequency synthesizer, no external

filters or RF switch needed

•Green package: RoHS compliant and no

antimony or bromine

•Small size (QLP 4x4 mm package, 20

pins)

•Suited for systems compliant with EN 300

328 and EN 300 440 class 2 (Europe),

FCC CFR47 Part 15 (US), and ARIB STD-

T66 (Japan)

•Support for asynchronous and

synchronous serial receive/transmit mode

for backwards compatibility with existing

radio communication protocols

CC2500

SWRS040B Page 3 of 92

Abbreviations

Abbreviations used in this data sheet are described below.

ACP Adjacent Channel Power MSB Most Significant Bit

ADC Analog to Digital Converter MSK Minimum Shift Keying

AFC Automatic Frequency Offset Compensation NA Not Applicable

AGC Automatic Gain Control NRZ Non Return to Zero (Coding)

AMR Automatic Meter Reading OOK On Off Keying

ARIB Association of Radio Industries and Businesses PA Power Amplifier

BER Bit Error Rate PCB Printed Circuit Board

BT Bandwidth-Time product PD Power Down

CCA Clear Channel Assessment PER Packet Error Rate

CFR Code of Federal Regulations PLL Phase Locked Loop

CRC Cyclic Redundancy Check POR Power-on Reset

CS Carrier Sense PQI Preamble Quality Indicator

CW Continuous Wave (Unmodulated Carrier) PQT Preamble Quality Threshold

DC Direct Current RCOSC RC Oscillator

DVGA Digital Variable Gain Amplifier QPSK Quadrature Phase Shift Keying

ESR Equivalent Series Resistance QLP Quad Leadless Package

FCC Federal Communications Commission RC Resistor-Capacitor

FEC Forward Error Correction RF Radio Frequency

FIFO First-In-First-Out RSSI Received Signal Strength Indicator

FHSS Frequency Hopping Spread Spectrum RX Receive, Receive Mode

2-FSK Frequency Shift Keying SMD Surface Mount Device

GFSK Gaussian shaped Frequency Shift Keying SNR Signal to Noise Ratio

IF Intermediate Frequency SPI Serial Peripheral Interface

I/Q In-Phase/Quadrature SRD Short Range Device

ISM Industrial, Scientific and Medical T/R Transmit/Receive

LBT Listen Before Transmit TX Transmit, Transmit Mode

LC Inductor-Capacitor VCO Voltage Controlled Oscillator

LNA Low Noise Amplifier WLAN Wireless Local Area Networks

LO Local Oscillator WOR Wake on Radio, Low power polling

LQI Link Quality Indicator XOSC Crystal Oscillator

LSB Least Significant Bit XTAL Crystal

MCU Microcontroller Unit

CC2500

SWRS040B Page 4 of 92

Table of Contents

APPLICATIONS...........................................................................................................................................1

PRODUCT DESCRIPTION.........................................................................................................................1

KEY FEATURES..........................................................................................................................................1

RF PERFORMANCE ...........................................................................................................................................1

ANALOG FEATURES..........................................................................................................................................1

DIGITAL FEATURES ..........................................................................................................................................1

LOW-POWER FEATURES ...................................................................................................................................2

GENERAL..........................................................................................................................................................2

ABBREVIATIONS........................................................................................................................................3

TABLE OF CONTENTS..............................................................................................................................4

1ABSOLUTE MAXIMUM RATINGS...........................................................................................................7

2OPERATING CONDITIONS......................................................................................................................7

3GENERAL CHARACTERISTICS ...............................................................................................................7

4ELECTRICAL SPECIFICATIONS...............................................................................................................8

4.1 CURRENT CONSUMPTION .....................................................................................................................8

4.2 RF RECEIVE SECTION.........................................................................................................................10

4.3 RF TRANSMIT SECTION......................................................................................................................12

4.4 CRYSTAL OSCILLATOR.......................................................................................................................13

4.5 LOW POWER RC OSCILLATOR............................................................................................................13

4.6 FREQUENCY SYNTHESIZER CHARACTERISTICS...................................................................................14

4.7 ANALOG TEMPERATURE SENSOR .......................................................................................................15

4.8 DC CHARACTERISTICS .......................................................................................................................15

4.9 POWER-ON RESET..............................................................................................................................15

5PIN CONFIGURATION..........................................................................................................................16

6CIRCUIT DESCRIPTION........................................................................................................................18

7APPLICATION CIRCUIT........................................................................................................................18

8CONFIGURATION OVERVIEW ..............................................................................................................20

9CONFIGURATION SOFTWARE ..............................................................................................................21

10 4-WIRE SERIAL CONFIGURATION AND DATA INTERFACE ...................................................................22

10.1 CHIP STATUS BYTE ............................................................................................................................23

10.2 REGISTER ACCESS..............................................................................................................................24

10.3 SPI READ ...........................................................................................................................................24

10.4 COMMAND STROBES ..........................................................................................................................25

10.5 FIFO ACCESS.....................................................................................................................................25

10.6 PATABLE ACCESS.............................................................................................................................25

11 MICROCONTROLLER INTERFACE AND PIN CONFIGURATION...............................................................26

11.1 CONFIGURATION INTERFACE..............................................................................................................26

11.2 GENERAL CONTROL AND STATUS PINS ..............................................................................................26

11.3 OPTIONAL RADIO CONTROL FEATURE ...............................................................................................27

12 DATA RATE PROGRAMMING...............................................................................................................27

13 RECEIVER CHANNEL FILTER BANDWIDTH..........................................................................................28

14 DEMODULATOR,SYMBOL SYNCHRONIZER AND DATA DECISION.......................................................28

14.1 FREQUENCY OFFSET COMPENSATION.................................................................................................28

14.2 BIT SYNCHRONIZATION......................................................................................................................28

14.3 BYTE SYNCHRONIZATION...................................................................................................................29

15 PACKET HANDLING HARDWARE SUPPORT .........................................................................................29

15.1 DATA WHITENING..............................................................................................................................30

15.2 PACKET FORMAT................................................................................................................................30

15.3 PACKET FILTERING IN RECEIVE MODE...............................................................................................32

15.4 CRC CHECK.......................................................................................................................................32

15.5 PACKET HANDLING IN TRANSMIT MODE............................................................................................33

15.6 PACKET HANDLING IN RECEIVE MODE ..............................................................................................33

15.7 PACKET HANDLING IN FIRMWARE......................................................................................................34

16 MODULATION FORMATS.....................................................................................................................34

16.1 FREQUENCY SHIFT KEYING................................................................................................................34

16.2 MINIMUM SHIFT KEYING....................................................................................................................34

CC2500

SWRS040B Page 5 of 92

16.3 AMPLITUDE MODULATION .................................................................................................................35

17 RECEIVED SIGNAL QUALIFIERS AND LINK QUALITY INFORMATION...................................................35

17.1 SYNC WORD QUALIFIER.....................................................................................................................35

17.2 PREAMBLE QUALITY THRESHOLD (PQT)...........................................................................................35

17.3 RSSI...................................................................................................................................................35

17.4 CARRIER SENSE (CS)..........................................................................................................................36

17.5 CLEAR CHANNEL ASSESSMENT (CCA) ..............................................................................................38

17.6 LINK QUALITY INDICATOR (LQI).......................................................................................................38

18 FORWARD ERROR CORRECTION WITH INTERLEAVING........................................................................38

18.1 FORWARD ERROR CORRECTION (FEC)...............................................................................................38

18.2 INTERLEAVING ...................................................................................................................................39

19 RADIO CONTROL ................................................................................................................................40

19.1 POWER-ON START-UP SEQUENCE......................................................................................................40

19.2 CRYSTAL CONTROL............................................................................................................................41

19.3 VOLTAGE REGULATOR CONTROL.......................................................................................................41

19.4 ACTIVE MODES ..................................................................................................................................42

19.5 WAKE ON RADIO (WOR)...................................................................................................................42

19.6 TIMING ...............................................................................................................................................43

19.7 RX TERMINATION TIMER...................................................................................................................44

20 DATA FIFO........................................................................................................................................44

21 FREQUENCY PROGRAMMING ..............................................................................................................45

22 VCO...................................................................................................................................................46

22.1 VCO AND PLL SELF-CALIBRATION ...................................................................................................46

23 VOLTAGE REGULATORS .....................................................................................................................47

24 OUTPUT POWER PROGRAMMING ........................................................................................................47

25 SELECTIVITY ......................................................................................................................................49

26 CRYSTAL OSCILLATOR.......................................................................................................................51

26.1 REFERENCE SIGNAL ...........................................................................................................................51

27 EXTERNAL RF MATCH .......................................................................................................................51

28 PCB LAYOUT RECOMMENDATIONS....................................................................................................52

29 GENERAL PURPOSE /TEST OUTPUT CONTROL PINS ...........................................................................53

30 ASYNCHRONOUS AND SYNCHRONOUS SERIAL OPERATION................................................................55

30.1 ASYNCHRONOUS OPERATION.............................................................................................................55

30.2 SYNCHRONOUS SERIAL OPERATION ...................................................................................................55

31 SYSTEM CONSIDERATIONS AND GUIDELINES .....................................................................................55

31.1 SRD REGULATIONS............................................................................................................................55

31.2 FREQUENCY HOPPING AND MULTI-CHANNEL SYSTEMS.....................................................................56

31.3 WIDEBAND MODULATION NOT USING SPREAD SPECTRUM ................................................................56

31.4 DATA BURST TRANSMISSIONS............................................................................................................56

31.5 CONTINUOUS TRANSMISSIONS ...........................................................................................................56

31.6 CRYSTAL DRIFT COMPENSATION .......................................................................................................57

31.7 SPECTRUM EFFICIENT MODULATION..................................................................................................57

31.8 LOW COST SYSTEMS ..........................................................................................................................57

31.9 BATTERY OPERATED SYSTEMS ..........................................................................................................57

31.10 INCREASING OUTPUT POWER .........................................................................................................57

32 CONFIGURATION REGISTERS ..............................................................................................................58

32.1 CONFIGURATION REGISTER DETAILS –REGISTERS WITH PRESERVED VALUES IN SLEEP STATE ......62

32.2 CONFIGURATION REGISTER DETAILS –REGISTERS THAT LOSE PROGRAMMING IN SLEEP STATE.....81

32.3 STATUS REGISTER DETAILS................................................................................................................82

33 PACKAGE DESCRIPTION (QLP 20)......................................................................................................86

33.1 RECOMMENDED PCB LAYOUT FOR PACKAGE (QLP 20)....................................................................87

33.2 SOLDERING INFORMATION .................................................................................................................87

33.3 TRAY SPECIFICATION .........................................................................................................................87

33.4 CARRIER TAPE AND REEL SPECIFICATION..........................................................................................88

34 ORDERING INFORMATION...................................................................................................................88

35 REFERENCES.......................................................................................................................................88

36 GENERAL INFORMATION ....................................................................................................................89

36.1 DOCUMENT HISTORY .........................................................................................................................89

36.2 PRODUCT STATUS DEFINITIONS .........................................................................................................90

CC2500

SWRS040B Page 6 of 92

37 ADDRESS INFORMATION.....................................................................................................................91

38 TI WORLDWIDE TECHNICAL SUPPORT ...............................................................................................91

CC2500

SWRS040B Page 7 of 92

1 Absolute Maximum Ratings

Under no circumstances must the absolute maximum ratings given in Table 1 be violated. Stress

exceeding one or more of the limiting values may cause permanent damage to the device.

Caution! ESD sensitive device.

Precaution should be used when handling

the device in order to prevent permanent

damage.

Parameter Min Max Unit Condition

Supply voltage –0.3 3.9 V All supply pins must have the same voltage

Voltage on any digital pin –0.3 VDD+0.3,

max 3.9

V

Voltage on the pins RF_P, RF_N

and DCOUPL

–0.3 2.0 V

Voltage ramp-up rate 120 kV/µs

Input RF level +10 dBm

Storage temperature range –50 150 °C

Solder reflow temperature 260 °C According to IPC/JEDEC J-STD-020D

ESD <500 V According to JEDEC STD 22, method A114,

Human Body Model

Table 1: Absolute Maximum Ratings

2 Operating Conditions

The

CC2500

operating conditions are listed in Table 2 below.

Parameter Min Max Unit Condition

Operating temperature –40 85 °C

Operating supply voltage 1.8 3.6 V All supply pins must have the same voltage

Table 2: Operating Conditions

3 General Characteristics

Parameter Min Typ Max Unit Condition/Note

Frequency range 2400 2483.5 MHz There will be spurious signals at n/2·crystal oscillator

frequency (n is an integer number). RF frequencies at

n/2·crystal oscillator frequency should therefore be

avoided (e.g. 2405, 2418, 2431, 2444, 2457, 2470 and

2483 MHz when using a 26 MHz crystal).

Data rate 1.2

1.2

26

500

250

500

kBaud

kBaud

kBaud

2-FSK

GFSK and OOK

(Shaped) MSK (also known as differential offset

QPSK)

Optional Manchester encoding (the data rate in kbps

will be half the baud rate).

Table 3: General Characteristics

CC2500

SWRS040B Page 8 of 92

4 Electrical Specifications

4.1 Current Consumption

Tc = 25°C, VDD = 3.0 V if nothing else stated. All measurement results obtained using the CC2500EM reference design

([4]).

Parameter Min Typ Max Unit Condition

400 nA Voltage regulator to digital part off, register values retained

(SLEEP state). All GDO pins programmed to 0x2F (HW to 0)

900 nA Voltage regulator to digital part off, register values retained, low-

power RC oscillator running (SLEEP state with WOR enabled)

92 µA Voltage regulator to digital part off, register values retained,

XOSC running (SLEEP state with MCSM0.OSC_FORCE_ON set)

Current consumption in

power down modes

160 µA Voltage regulator to digital part on, all other modules in power

down (XOFF state)

8.1 µA Automatic RX polling once each second, using low-power RC

oscillator, with 460 kHz filter bandwidth and 250 kBaud data rate,

PLL calibration every 4th wakeup. Average current with signal in

channel below carrier sense level (MCSM2.RX_TIME_RSSI=1).

35 µA Same as above, but with signal in channel above carrier sense

level, 1.95 ms RX timeout, and no preamble/sync word found.

1.4 µA Automatic RX polling every 15th second, using low-power RC

oscillator, with 460 kHz filter bandwidth and 250 kBaud data rate,

PLL calibration every 4th wakeup. Average current with signal in

channel below carrier sense level (MCSM2.RX_TIME_RSSI=1).

34 µA Same as above, but with signal in channel above carrier sense

level, 29.3 ms RX timeout, and no preamble/sync word found.

1.5 mA Only voltage regulator to digital part and crystal oscillator running

(IDLE state)

Current consumption

7.4 mA Only the frequency synthesizer is running (FSTXON state). This

currents consumption is also representative for the other

intermediate states when going from IDLE to RX or TX, including

the calibration state.

17.0 mA Receive mode, 2.4 kBaud, input at sensitivity limit,

MDMCFG2.DEM_DCFILT_OFF=0

14.5 mA Receive mode, 2.4 kBaud, input well above sensitivity limit,

MDMCFG2.DEM_DCFILT_OFF=0

17.3 mA Receive mode, 10 kBaud, input at sensitivity limit,

MDMCFG2.DEM_DCFILT_OFF=0

14.9 mA Receive mode, 10 kBaud, input well above sensitivity limit,

MDMCFG2.DEM_DCFILT_OFF=0

18.8 mA Receive mode, 250 kBaud, input at sensitivity limit,

MDMCFG2.DEM_DCFILT_OFF=0

15.7 mA Receive mode, 250 kBaud, input well above sensitivity limit,

MDMCFG2.DEM_DCFILT_OFF=0

16.6 mA Receive mode, 250 kBaud current optimized, input at sensitivity

limit, MDMCFG2.DEM_DCFILT_OFF=1

13.3 mA Receive mode, 250 kBaud current optimized, input well above

sensitivity limit, MDMCFG2.DEM_DCFILT_OFF=1

19.6 mA Receive mode, 500 kBaud, input at sensitivity limit,

MDMCFG2.DEM_DCFILT_OFF=0

Current consumption,

RX states

17.0 mA Receive mode, 500 kBaud, input well above sensitivity limit,

MDMCFG2.DEM_DCFILT_OFF=0

CC2500

SWRS040B Page 9 of 92

11.1 mA Transmit mode, –12 dBm output power

15.0 mA Transmit mode, -6 dBm output power

21.2 mA Transmit mode, 0 dBm output power

Current consumption,

TX states

21.5 mA Transmit mode, +1 dBm output power

Table 4: Current Consumption

CC2500

SWRS040B Page 10 of 92

4.2 RF Receive Section

Tc = 25°C, VDD = 3.0 V if nothing else stated. All measurement results obtained using the CC2500EM reference design

([4]).

Parameter Min Typ Max Unit Condition/Note

Digital channel filter

bandwidth

58 812 kHz User programmable. The bandwidth limits are

proportional to crystal frequency (given values assume

a 26.0 MHz crystal).

2.4 kBaud data rate, sensitivity optimized, MDMCFG2.DEM_DCFILT_OFF=0

(2-FSK, 1% packet error rate, 20 bytes packet length, 203 kHz digital channel filter bandwidth)

Receiver sensitivity –104 dBm The RX current consumption can be reduced by

approximately 1.7 mA by setting

MDMCFG2.DEM_DCFILT_OFF=1. The typical sensitivity

is then -102 dBm and the temperature range is from 0oC

to +85oC.

The sensitivity can be improved to typically –106 dBm

with MDMCFG2.DEM_DCFILT_OFF=0 by programming

registers TEST2 and TEST1 (see page 82). The

temperature range is then from 0oC to +85oC.

Saturation –13 dBm

Adjacent channel

rejection

23 dB Desired channel 3 dB above the sensitivity limit. 250

kHz channel spacing

Alternate channel

rejection

31 dB Desired channel 3 dB above the sensitivity limit. 250

kHz channel spacing

See Figure 22 for plot of selectivity versus frequency

offset

Blocking

±10 MHz offset

±20 MHz offset

±50 MHz offset

64

70

71

dBm

dBm

dBm

Wanted signal 3 dB above sensitivity level.

Compliant with ETSI EN 300 440 class 2 receiver

requirements.

10 kBaud data rate, sensitivity optimized, MDMCFG2.DEM_DCFILT_OFF=0

(2-FSK, 1% packet error rate, 20 bytes packet length, 232 kHz digital channel filter bandwidth)

Receiver sensitivity –99 dBm The RX current consumption can be reduced by

approximately 1.7 mA by setting

MDMCFG2.DEM_DCFILT_OFF=1. The typical sensitivity

is then -97 dBm

The sensitivity can be improved to typically –101 dBm

with MDMCFG2.DEM_DCFILT_OFF=0 by programming

registers TEST2 and TEST1 (see page 82). The

temperature range is then from 0oC to +85oC.

Saturation –9 dBm

Adjacent channel

rejection

18 dB Desired channel 3 dB above the sensitivity limit. 250

kHz channel spacing

Alternate channel

rejection

25 dB Desired channel 3 dB above the sensitivity limit. 250

kHz channel spacing

See Figure 23 for plot of selectivity versus frequency

offset

Blocking

±10 MHz offset

±20 MHz offset

±50 MHz offset

59

65

66

dB

dB

dB

Wanted signal 3 dB above sensitivity level.

Compliant with ETSI EN 300 440 class 2 receiver

requirements.

CC2500

SWRS040B Page 11 of 92

Parameter Min Typ Max Unit Condition/Note

250 kBaud data rate, sensitivity optimized, MDMCFG2.DEM_DCFILT_OFF=0

(MSK, 1% packet error rate, 20 bytes packet length, 540 kHz digital channel filter bandwidth)

Receiver sensitivity –89 dBm

Saturation –13 dBm

Adjacent channel rejection 21 dB Desired channel 3 dB above the sensitivity limit. 750

kHz channel spacing

Alternate channel rejection 30 dB Desired channel 3 dB above the sensitivity limit. 750

kHz channel spacing

See Figure 24 for plot of selectivity versus frequency

offset

Blocking

±10 MHz offset

±20 MHz offset

±50 MHz offset

46

53

55

dB

dB

dB

Wanted signal 3 dB above sensitivity level.

Compliant with ETSI EN 300 440 class 2 receiver

requirements.

250 kBaud data rate, current optimized, MDMCFG2.DEM_DCFILT_OFF=1

(MSK, 1% packet error rate, 20 bytes packet length, 540 kHz digital channel filter bandwidth)

Receiver sensitivity –87 dBm

Saturation –12 dBm

Adjacent channel rejection 21 dB Desired channel 3 dB above the sensitivity limit. 750

kHz channel spacing

Alternate channel rejection 30 dB Desired channel 3 dB above the sensitivity limit. 750

kHz channel spacing

See Figure 25 for plot of selectivity versus frequency

offset

Blocking

±10 MHz offset

±20 MHz offset

±50 MHz offset

46

52

55

dB

dB

dB

Wanted signal 3 dB above sensitivity level.

Compliant with ETSI EN 300 440 class 2 receiver

requirements.

500 kBaud data rate, MDMCFG2.DEM_DCFILT_OFF=0 (MDMCFG2.DEM_DCFILT_OFF=1 cannot be used for data rates

>250 kBaud)

(MSK, 1% packet error rate, 20 bytes packet length, 812 kHz digital channel filter bandwidth)

Receiver sensitivity –83 dBm

Saturation –18 dBm

Adjacent channel rejection 14 dB Desired channel 3 dB above the sensitivity limit. 1 MHz

channel spacing

Alternate channel rejection 25 dB Desired channel 3 dB above the sensitivity limit. 1 MHz

channel spacing

See Figure 26 for plot of selectivity versus frequency

offset

Blocking

±10 MHz offset

±20 MHz offset

±50 MHz offset

40

48

50

dB

dB

dB

Wanted signal 3 dB above sensitivity level.

Compliant with ETSI EN 300 440 class 2 receiver

requirements.

General

Spurious emissions

25 MHz – 1 GHz

Above 1 GHz

–57

–47

dBm

dBm

RX latency 9 bit Serial operation. Time from start of reception until data

is available on the receiver data output pin is equal to 9

bit.

Table 5: RF Receive Section

CC2500

SWRS040B Page 12 of 92

4.3 RF Transmit Section

Tc = 25°C, VDD = 3.0 V, 0 dBm if nothing else stated. All measurement results obtained using the CC2500EM reference

design ([4]).

Parameter Min Typ Max Unit Condition/Note

Differential load

impedance

80 + j74 ΩDifferential impedance as seen from the RF-port (RF_P and

RF_N) towards the antenna. Follow the CC2500EM

reference design ([4]) available from the TI website.

Output power,

highest setting

+1

dBm Output power is programmable and full range is available

across the entire frequency band.

Delivered to a 50 Ωsingle-ended load via CC2500EM

reference design ([4]) RF matching network.

Output power,

lowest setting

–30

dBm Output power is programmable and full range is available

across the entire frequency band.

Delivered to a 50 Ωsingle-ended load via CC2500EM

reference design ([4]) RF matching network.

It is possible to program less than -30 dBm output power,

but this is not recommended due to large variation in output

power across operating conditions and processing corners

for these settings.

Occupied bandwidth

(99%)

91

117

296

489

kHz

kHz

kHz

kHz

2.4 kBaud, 38.2 kHz deviation, 2-FSK

10 kBaud, 38.2 kHz deviation, 2-FSK

250 kBaud, MSK

500 kBaud, MSK

Adjacent channel

power (ACP)

-28

-27

-22

-21

dBc

dBc

dBc

dBc

2.4 kBaud, 38.2 kHz deviation, 2-FSK, 250 kHz channel

spacing

10 kBaud, 38.2 kHz deviation, 2-FSK, 250 kHz channel

spacing

250 kBaud, MSK, 750 kHz channel spacing

500 kBaud, MSK, 1 MHz channel spacing

Spurious emissions

25 MHz – 1 GHz

47-74, 87.5-118, 174-

230, 470-862 MHz

1800-1900 MHz

At 2·RF and 3·RF

Otherwise above 1

GHz

–36

–54

–47

–41

–30

dBm

dBm

dBm

dBm

dBm

Restricted band in Europe

Restricted bands in USA

TX latency 8 bit Serial operation. Time from sampling the data on the

transmitter data input pin until it is observed on the RF

output ports.

Table 6: RF Transmit Section

CC2500

SWRS040B Page 13 of 92

4.4 Crystal Oscillator

Tc = 25°C, VDD = 3.0 V if nothing else stated.

Parameter Min Typ Max Unit Condition/Note

Crystal frequency 26 26 27 MHz

Tolerance ±40 ppm This is the total tolerance including a) initial tolerance, b) crystal

loading, c) aging, and d) temperature dependence.

The acceptable crystal tolerance depends on RF frequency and

channel spacing / bandwidth.

ESR 100

Ω

Start-up time 150 µs Measured on CC2500EM reference design ([4]) using crystal

AT-41CD2 from NDK.

This parameter is to a large degree crystal dependent.

Table 7: Crystal Oscillator Parameters

4.5 Low Power RC Oscillator

Tc = 25°C, VDD = 3.0 V if nothing else stated. All measurement results obtained using the CC2500EM reference design

([4]).

Parameter Min Typ Max Unit Condition/Note

Calibrated frequency 34.7 34.7 36 kHz Calibrated RC oscillator frequency is XTAL

frequency divided by 750

Frequency accuracy after

calibration

-1 /

+10

% The RC oscillator contains an error in the

calibration routine that statistically occurs in

17.3% of all calibrations performed. The given

maximum accuracy figures account for the

calibration error. Refer also to the

CC2500

Errata Notes.

Temperature coefficient +0.4 % / °C Frequency drift when temperature changes

after calibration

Supply voltage coefficient +3 % / V Frequency drift when supply voltage changes

after calibration

Initial calibration time 2 ms When the RC oscillator is enabled, calibration

is continuously done in the background as long

as the crystal oscillator is running.

Table 8: RC Oscillator Parameters

CC2500

SWRS040B Page 14 of 92

4.6 Frequency Synthesizer Characteristics

Tc = 25°C, VDD = 3.0 V if nothing else stated. All measurement results obtained using the CC2500EM reference design

([4]). Min figures are given using a 27 MHz crystal. Typ and max figures are given using a 26 MHz crystal.

Parameter Min Typ Max Unit Condition/Note

Programmed

frequency resolution

397 FXOSC/

216

412 Hz 26-27 MHz crystal.

Synthesizer frequency

tolerance

±40 ppm Given by crystal used. Required accuracy (including

temperature and aging) depends on frequency band and

channel bandwidth / spacing.

–78 dBc/Hz @ 50 kHz offset from carrier

–78 dBc/Hz @ 100 kHz offset from carrier

–81 dBc/Hz @ 200 kHz offset from carrier

–90 dBc/Hz @ 500 kHz offset from carrier

–100 dBc/Hz @ 1 MHz offset from carrier

–108 dBc/Hz @ 2 MHz offset from carrier

–114 dBc/Hz @ 5 MHz offset from carrier

RF carrier phase noise

–118 dBc/Hz @ 10 MHz offset from carrier

PLL turn-on / hop time 85.1 88.4 88.4 µs Time from leaving the IDLE state until arriving in the RX,

FSTXON or TX state, when not performing calibration.

Crystal oscillator running.

PLL RX/TX settling

time

9.3 9.6 9.6 µs Settling time for the 1·IF frequency step from RX to TX

PLL TX/RX settling

time

20.7 21.5 21.5 µs Settling time for the 1·IF frequency step from TX to RX

PLL calibration time 694 721 721 µs Calibration can be initiated manually or automatically

before entering or after leaving RX/TX.

Table 9: Frequency Synthesizer Parameters

CC2500

SWRS040B Page 15 of 92

4.7 Analog Temperature Sensor

The characteristics of the analog temperature sensor at 3.0 V supply voltage are listed in Table

10 below. Note that it is necessary to write 0xBF to the PTEST register to use the analog

temperature sensor in the IDLE state.

Parameter Min Typ Max Unit Condition/Note

Output voltage at –40°C 0.654 V

Output voltage at 0°C 0.750 V

Output voltage at +40°C 0.848 V

Output voltage at +80°C 0.946 V

Temperature coefficient 2.43 mV/°C Fitted from –20°C to +80°C

Error in calculated

temperature, calibrated

-2 *0 2

* °C From –20°C to +80°C when using 2.43 mV / °C,

after 1-point calibration at room temperature

*The indicated minimum and maximum error with 1-

point calibration is based on measured values for

typical process parameters

Current consumption

increase when enabled

0.3 mA

Table 10: Analog Temperature Sensor Parameters

4.8 DC Characteristics

Tc = 25°C if nothing else stated.

Digital Inputs/Outputs Min Max Unit Condition

Logic "0" input voltage 0 0.7 V

Logic "1" input voltage VDD-0.7 VDD V

Logic "0" output voltage 0 0.5 V For up to 4 mA output current

Logic "1" output voltage VDD-0.3 VDD V For up to 4 mA output current

Logic "0" input current N/A –50 nA Input equals 0 V

Logic "1" input current N/A 50 nA Input equals VDD

Table 11: DC Characteristics

4.9 Power-On Reset

When the power supply complies with the requirements in Table 12 below, proper Power-On-

Reset functionality is guaranteed. Otherwise, the chip should be assumed to have unknown state

until transmitting an SRES strobe over the SPI interface. See Section 19.1 on page 40 for further

details.

Parameter Min Typ Max Unit Condition/Note

Power ramp-up time 5 ms From 0 V until reaching 1.8 V

Power off time 1 ms Minimum time between power-on and power-off

Table 12: Power-on Reset Requirements

CC2500

SWRS040B Page 16 of 92

5 Pin Configuration

1

20 19 18 17 16

15

14

13

12

11

109876

5

4

3

2

GND

Exposed die

attach pad

SCLK

SO (GDO1)

GDO2

DVDD

DCOUPL

GDO0 (ATEST)

XOSC_Q1

AVDD

XOSC_Q2

AVDD

RF_P

RF_N

GND

AVDD

RBIAS

DGUARD

GND

SI

CSn

AVDD

Figure 1: Pinout Top View

Note: The exposed die attach pad must be connected to a solid ground plane as this is the main

ground connection for the chip.

CC2500

SWRS040B Page 17 of 92

Pin # Pin name Pin type Description

1 SCLK Digital Input Serial configuration interface, clock input

2 SO (GDO1) Digital Output Serial configuration interface, data output.

Optional general output pin when CSn is high

3 GDO2

Digital Output Digital output pin for general use:

•Test signals

•FIFO status signals

•Clear Channel Indicator

•Clock output, down-divided from XOSC

•Serial output RX data

4 DVDD Power (Digital) 1.8 - 3.6 V digital power supply for digital I/O’s and for the digital core

voltage regulator

5 DCOUPL Power (Digital) 1.6 - 2.0 V digital power supply output for decoupling.

NOTE: This pin is intended for use with the

CC2500

only. It can not be

used to provide supply voltage to other devices.

6 GDO0

(ATEST)

Digital I/O

Digital output pin for general use:

•Test signals

•FIFO status signals

•Clear Channel Indicator

•Clock output, down-divided from XOSC

•Serial output RX data

•Serial input TX data

Also used as analog test I/O for prototype/production testing

7 CSn Digital Input Serial configuration interface, chip select

8 XOSC_Q1 Analog I/O Crystal oscillator pin 1, or external clock input

9 AVDD Power (Analog) 1.8 - 3.6 V analog power supply connection

10 XOSC_Q2 Analog I/O Crystal oscillator pin 2

11 AVDD Power (Analog) 1.8 - 3.6 V analog power supply connection

12 RF_P RF I/O Positive RF input signal to LNA in receive mode

Positive RF output signal from PA in transmit mode

13 RF_N RF I/O Negative RF input signal to LNA in receive mode

Negative RF output signal from PA in transmit mode

14 AVDD Power (Analog) 1.8 - 3.6 V analog power supply connection

15 AVDD Power (Analog) 1.8 - 3.6 V analog power supply connection

16 GND Ground (Analog) Analog ground connection

17 RBIAS Analog I/O External bias resistor for reference current

18 DGUARD Power (Digital) Power supply connection for digital noise isolation

19 GND Ground (Digital) Ground connection for digital noise isolation

20 SI Digital Input Serial configuration interface, data input

Table 13: Pinout Overview

CC2500

SWRS040B Page 18 of 92

6 Circuit Description

BIAS

PA

RBIAS XOSC_Q1 XOSC_Q2

CSn

SI

SO (GDO1)

XOSC

SCLK

LNA

0

90

FREQ

SYNTH

ADC

ADC

DEMODULATOR

FEC / INTERLEAVER

PACKET HANDLER

RXFIFO

MODULATOR

TXFIFO

DIGITAL INTERFACE TO MCU

RADIO CONTROL

RF_P

RF_N

GDO2

GDO0(ATEST)

RC OSC

Figure 2:

CC2500

Simplified Block Diagram

A simplified block diagram of

CC2500

is shown

in Figure 2.

CC2500

features a low-IF receiver. The

received RF signal is amplified by the low-

noise amplifier (LNA) and down-converted in

quadrature (I and Q) to the intermediate

frequency (IF). At IF, the I/Q signals are

digitised by the ADCs. Automatic gain control

(AGC), fine channel filtering, demodulation

bit/packet synchronization are performed

digitally.

The transmitter part of

CC2500

is based on

direct synthesis of the RF frequency.

The frequency synthesizer includes a

completely on-chip LC VCO and a 90 degrees

phase shifter for generating the I and Q LO

signals to the down-conversion mixers in

receive mode.

A crystal is to be connected to XOSC_Q1 and

XOSC_Q2. The crystal oscillator generates the

reference frequency for the synthesizer, as

well as clocks for the ADC and the digital part.

A 4-wire SPI serial interface is used for

configuration and data buffer access.

The digital baseband includes support for

channel configuration, packet handling, and

data buffering.

7 Application Circuit

Only a few external components are required

for using the

CC2500

. The recommended

application circuit is shown in Figure 3. The

external components are described in Table

14, and typical values are given in Table 15.

Bias Resistor

The bias resistor R171 is used to set an

accurate bias current.

Balun and RF Matching

The components between the RF_N/RF_P pins

and the point where the two signals are joined

together (C122, C132, L121, and L131) form a

CC2500

SWRS040B Page 19 of 92

balun that converts the differential RF signal

on

CC2500

to a single-ended RF signal. C121

and C131 are needed for DC blocking.

Together with an appropriate LC network, the

balun components also transform the

impedance to match a 50 Ωantenna (or

cable). Suggested values are listed in Table

15.

The balun and LC filter component values and

their placement are important to keep the

performance optimized. It is highly

recommended to follow the CC2500EM

reference design ([4]).

Crystal

The crystal oscillator uses an external crystal

with two loading capacitors (C81 and C101).

See Section 26 on page 51 for details.

Power Supply Decoupling

The power supply must be properly decoupled

close to the supply pins. Note that decoupling

capacitors are not shown in the application

circuit. The placement and the size of the

decoupling capacitors are very important to

achieve the optimum performance. The

CC2500EM reference design ([4]) should be

followed closely.

Component Description

C51 Decoupling capacitor for on-chip voltage regulator to digital part

C81/C101 Crystal loading capacitors, see Section 26 on page 51 for details

C121/C131 RF balun DC blocking capacitors

C122/C132 RF balun/matching capacitors

C123/C124 RF LC filter/matching capacitors

L121/L131 RF balun/matching inductors (inexpensive multi-layer type)

L122 RF LC filter inductor (inexpensive multi-layer type)

R171 Resistor for internal bias current reference

XTAL 26-27 MHz crystal, see Section 26 on page 51 for details

Table 14: Overview of External Components (excluding supply decoupling capacitors)

Antenna

(50 Ohm)

Digital Inteface

1.8V-3.6V power supply

6 GDO0

7 CSn

8 XOSC_Q1

9 AVDD

10 XOSC_Q2

SI 20

GND 19

DGUARD 18

RBIAS 17

GND 16

1 SCLK

2 SO (GDO1)

3 GDO2

4 DVDD

5 DCOUPL

AVDD 15

AVDD 14

RF_N 13

RF_P 12

AVDD 11

XTAL

C122

C132

L131

L121 L122

C123 C124

R171

C81 C101

C51

CSn

GDO0

(optional)

GDO2

(optional)

SO

(GDO1)

SCLK

SI

CC2500

DIE ATTACH PAD:

C131

C121

Alternative:

Folded dipole PCB

antenna (no external

components needed)

Figure 3: Typical Application and Evaluation Circuit (excluding supply decoupling capacitors)

CC2500

SWRS040B Page 20 of 92

Component Value Manufacturer

C51 100 nF ±10%, 0402 X5R Murata GRM15 series

C81 27 pF ±5%, 0402 NP0 Murata GRM15 series

C101 27 pF ±5%, 0402 NP0 Murata GRM15 series

C121 100 pF ±5%, 0402 NP0 Murata GRM15 series

C122 1.0 pF ±0.25 pF, 0402 NP0 Murata GRM15 series

C123 1.8 pF ±0.25 pF, 0402 NP0 Murata GRM15 series

C124 1.5 pF ±0.25 pF, 0402 NP0 Murata GRM15 series

C131 100 pF ±5%, 0402 NP0 Murata GRM15 series

C132 1.0 pF ±0.25 pF, 0402 NP0 Murata GRM15 series

L121 1.2 nH ±0.3 nH, 0402 monolithic Murata LQG15HS series

L122 1.2 nH ±0.3 nH, 0402 monolithic Murata LQG15HS series

L131 1.2 nH ±0.3 nH, 0402 monolithic Murata LQG15HS series

R171 56 kΩ±1%, 0402 Koa RK73 series

XTAL 26.0 MHz surface mount crystal NDK, AT-41CD2

Table 15: Bill Of Materials for the Application Circuit

Measurements have been performed with

multi-layer inductors from other manufacturers

(e.g. Würth) and the measurement results

were the same as when using the Murata part.

The Gerber files for the CC2500EM reference

design ([4]) are available from the TI website.

Figure 4: CC2500EM Reference Design ([4])

8 Configuration Overview

CC2500

can be configured to achieve optimum

performance for many different applications.

Configuration is done using the SPI interface.

The following key parameters can be

programmed:

•Power-down / power up mode

•Crystal oscillator power-up / power-down

•Receive / transmit mode

•RF channel selection

•Data rate

•Modulation format

•RX channel filter bandwidth

•RF output power

•Data buffering with separate 64-byte

receive and transmit FIFOs

•Packet radio hardware support

•Forward Error Correction (FEC) with

interleaving

•Data Whitening

•Wake-On-Radio (WOR)

Details of each configuration register can be

found in Section 32, starting on page 58.

Figure 5 shows a simplified state diagram that

explains the main

CC2500

states, together with

typical usage and current consumption. For

detailed information on controlling the

CC2500

state machine, and a complete state diagram,

see Section 19, starting on page 40.

Other manuals for CC2500

1

Table of contents

Other Chipcon Transceiver manuals