On-board Flash Programmer

FP-40 Technical Information

Second Edition (Aug. 31, 2023)

Copyright ©2023 Computex Co., Ltd.

Table of Contents

Document change history...................................................................................... 1

arm Cortex series (JTAG/SWD).............................................................................. 2

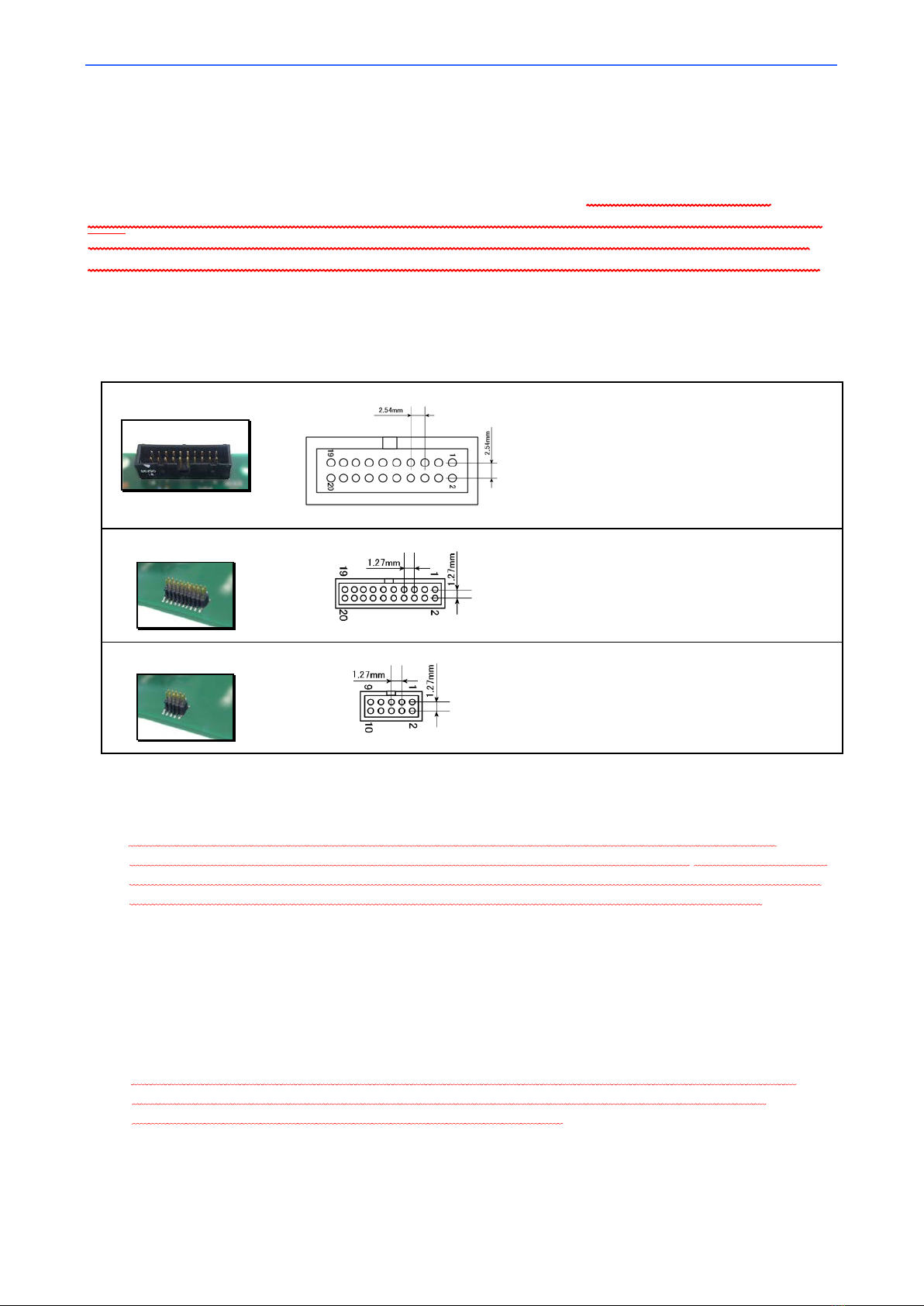

■Supported connectors ................................................................................................................................ 2

■Applicable products .................................................................................................................................... 2

■FP-40 usage environment check chart....................................................................................................... 3

■20-pin 2.54mm-pitch connector .................................................................................................................. 4

①SWD interface ......................................................................................................................................... 4

②JTAG interface......................................................................................................................................... 6

■20-pin 1.27mm-pitch connector .................................................................................................................. 8

③SWD interface ......................................................................................................................................... 8

④JTAG interface......................................................................................................................................... 9

■10-pin 1.27mm-pitch connector ................................................................................................................ 10

⑤SWD interface ....................................................................................................................................... 10

⑥JTAG interface + Trace.......................................................................................................................... 11

■Reference:RZ/A and RZ/T series /SRST, /TRST reference diagram ....................................................... 12

■About FP-40 unique signals ..................................................................................................................... 13

Note ............................................................................................................................................................ 13

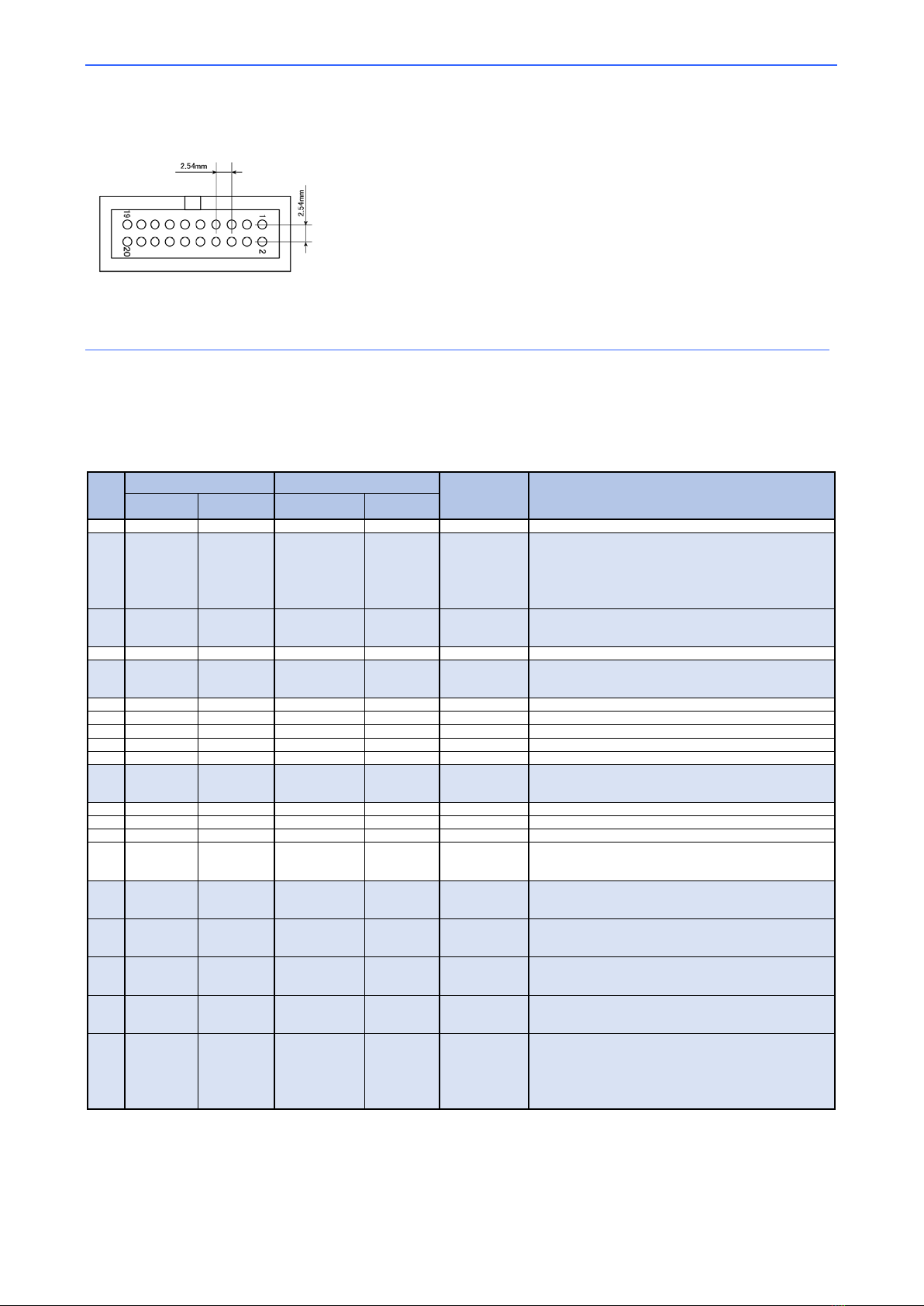

■FP-40 target interface specifications ........................................................................................................ 14

Specifications of the target connector.............................................................................................................. 14

Dimensions of TARGET cable ......................................................................................................................... 15

Target interface voltage level........................................................................................................................... 16

Signal specifications ........................................................................................................................................ 16

UART...................................................................................................................... 18

■Target interface specifications when using UART on the FP-40 unit ........................................................ 18

Specifications of the target connector.............................................................................................................. 18

Dimensions of TARGET cable ......................................................................................................................... 19

Target interface voltage level........................................................................................................................... 19

Signal specifications ........................................................................................................................................ 19

Connection reference diagram ........................................................................................................................ 20

Note................................................................................................................................................................. 20

Common specifications for each interface......................................................... 21

■External I/O functions of FP-40 ................................................................................................................ 21

External input / output function powered by VTref (1 pin)................................................................................ 21

External input / output function using 3.3V I/F ................................................................................................. 21

EX_OK/EX33_OK............................................................................................................................................ 22

EX_STARTn/EX33_STARTn ........................................................................................................................... 23

EX_BSY/EX33_BSY........................................................................................................................................ 23

EX_NG ............................................................................................................................................................ 23

Using each signal in combination .................................................................................................................... 24

External I / O function timing with VTref (1 pin)................................................................................................ 25

External I / O function timing with 3.3V I/F....................................................................................................... 25

C-Flash Settings .............................................................................................................................................. 26