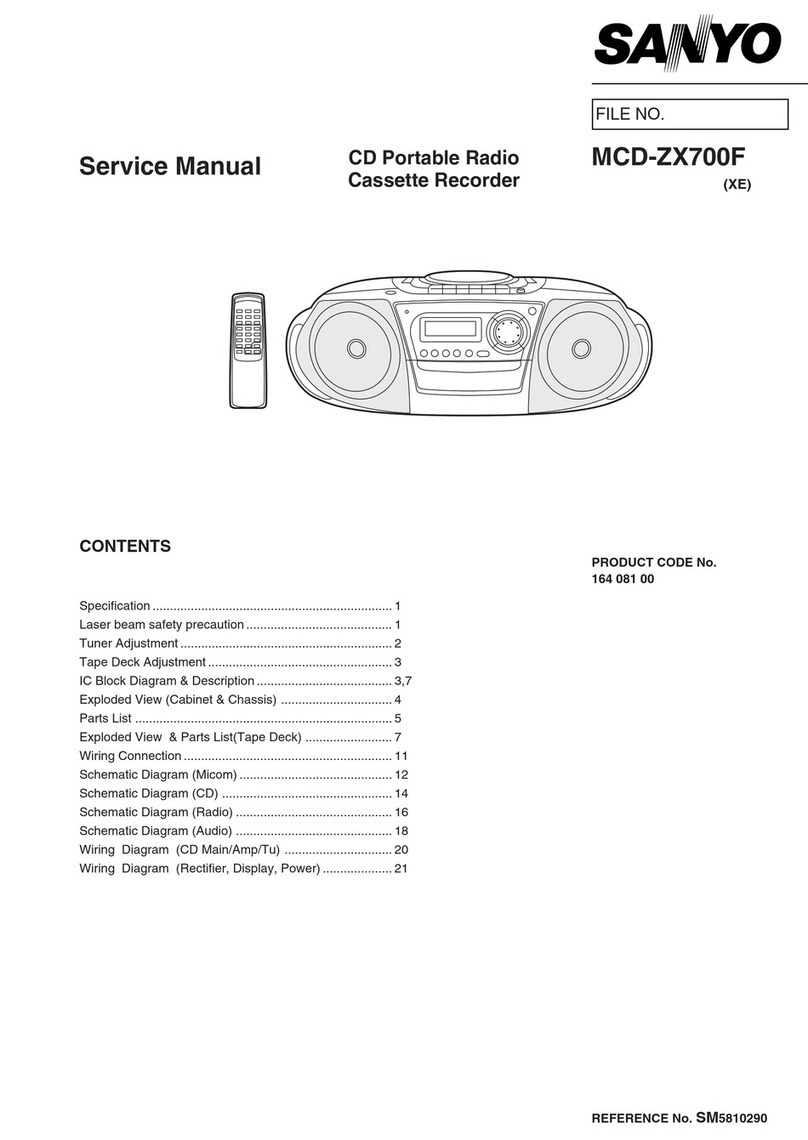

TABLE OF CONTENTS

SECTION 1. CONTROLS AND FUNCTIONS...........................................................................................................3

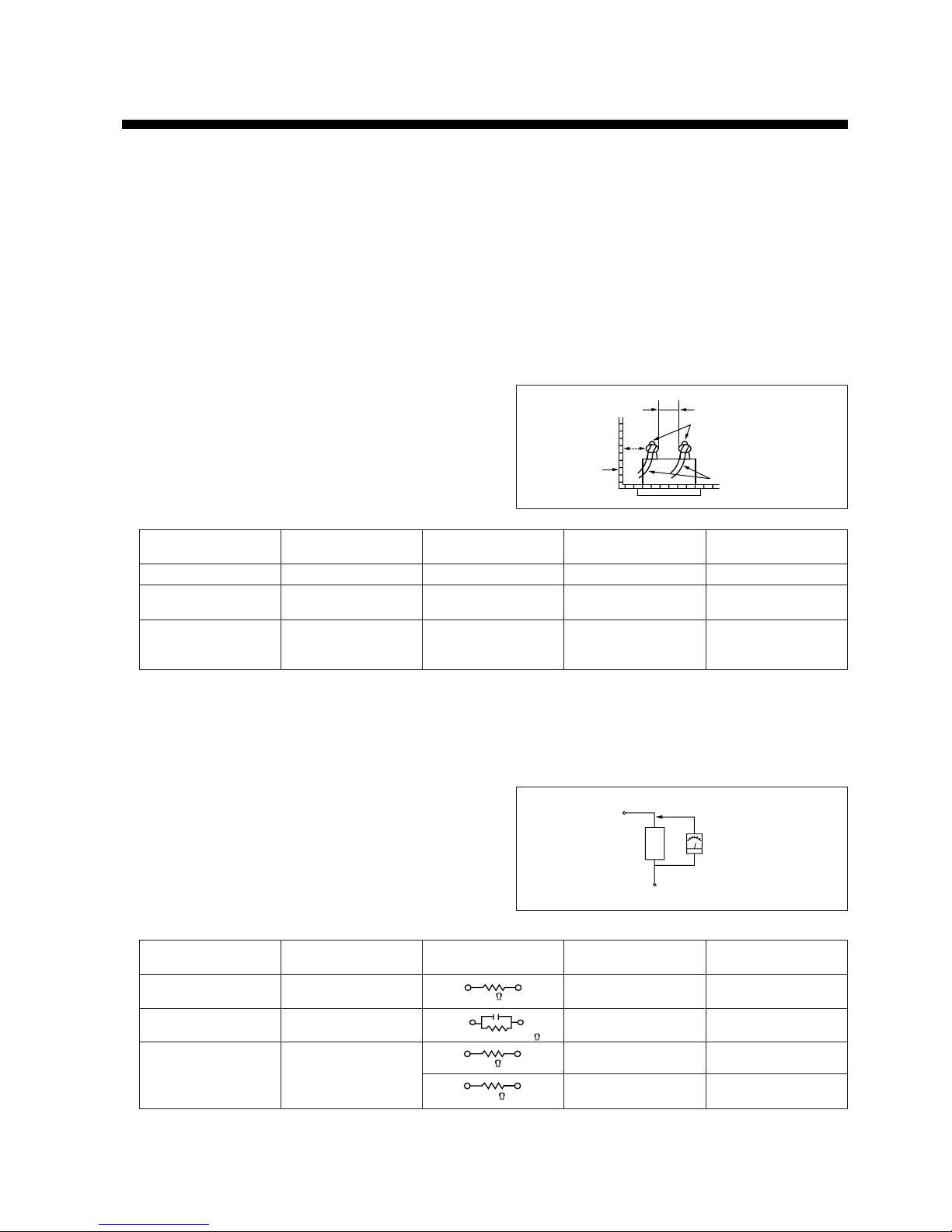

SECTION 2. ELECTRICAL ADJUSTMENTS

2-1. VIDEO CIRCUIT ADJUSTMENT METHODS.....................................................................................................................5

2-2. AUDIO CIRCUIT ADJUSTMENT METHOD.......................................................................................................................7

2-3. IF MODULE CIRCUIT ADJUSTMENT METHODS............................................................................................................8

SECTION 3. CIRCUIT OPERATION PRINCIPLES

3-1. POWER CIRCUIT..............................................................................................................................................................12

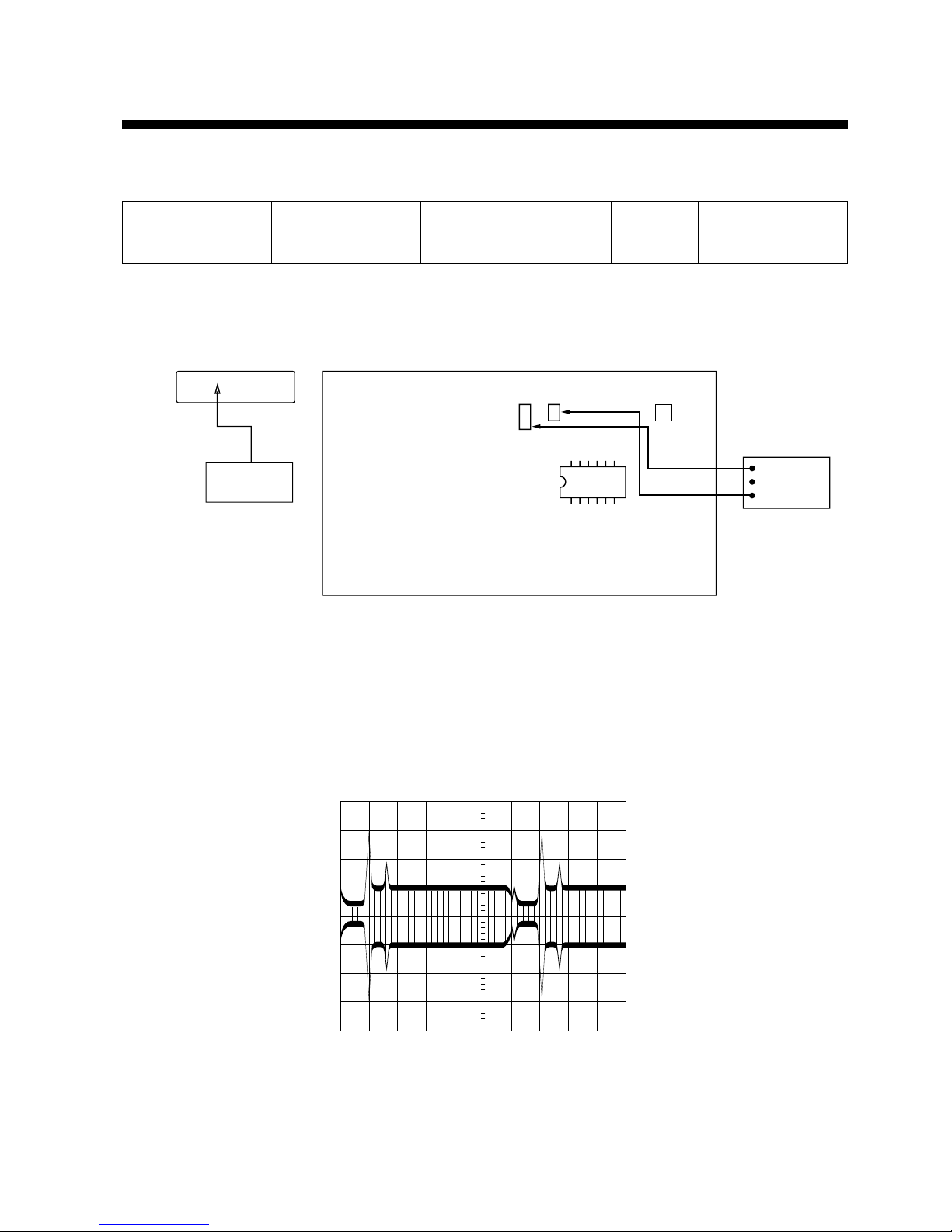

3-2. VIDEO CIRCUIT................................................................................................................................................................14

3-3. IF CIRCUIT OPERATION..................................................................................................................................................19

SECTION 4. TROUBLE SHOOTING FLOW CHART

4-1. POWER CIRCUIT..............................................................................................................................................................21

4-2. PIF CIRCUIT TROUBLE SHOOTING...............................................................................................................................23

4-3. LOGIC CIRCUIT................................................................................................................................................................24

4-4. SERVO-SYSCON CIRCUIT..............................................................................................................................................26

4-5. AUDIO CIRCUIT................................................................................................................................................................34

4-6. VIDEO CIRCUIT................................................................................................................................................................36

SECTION 5. WAVEFORMS OF THE VIDEO CIRCUIT......................................................................................47

SECTION 6. µ-COM PORT DESCRIPTION............................................................................................................51

SECTION 7. CIRCUIT DIAGRAM

7-1. CONNECTION DIAGRAM................................................................................................................................................57

7-2. POWER CIRCUIT..............................................................................................................................................................58

7-3. MAIN CIRCUIT..................................................................................................................................................................59

7-4. LOGIC CIRCUIT................................................................................................................................................................60

7-5. VIDEO CIRCUIT................................................................................................................................................................61

7-6. 2 HEAD PRE AMP CIRCUIT.............................................................................................................................................62

7-7. 4 HEAD PRE AMP CIRCUIT.............................................................................................................................................63

7-8. SECAM COLOUR CIRCUIT.............................................................................................................................................64

7-9. AUDIO CIRCUIT................................................................................................................................................................65

7-10. IF MODULE CIRCUIT.....................................................................................................................................................66

7-11. PIF CIRCUIT....................................................................................................................................................................67

7-12. SW & SCART CIRCUIT...................................................................................................................................................68

7-13. OSD CIRCUIT.................................................................................................................................................................69

7-14. REMOTE CONTROL CIRCUIT (VR-F2B).......................................................................................................................70

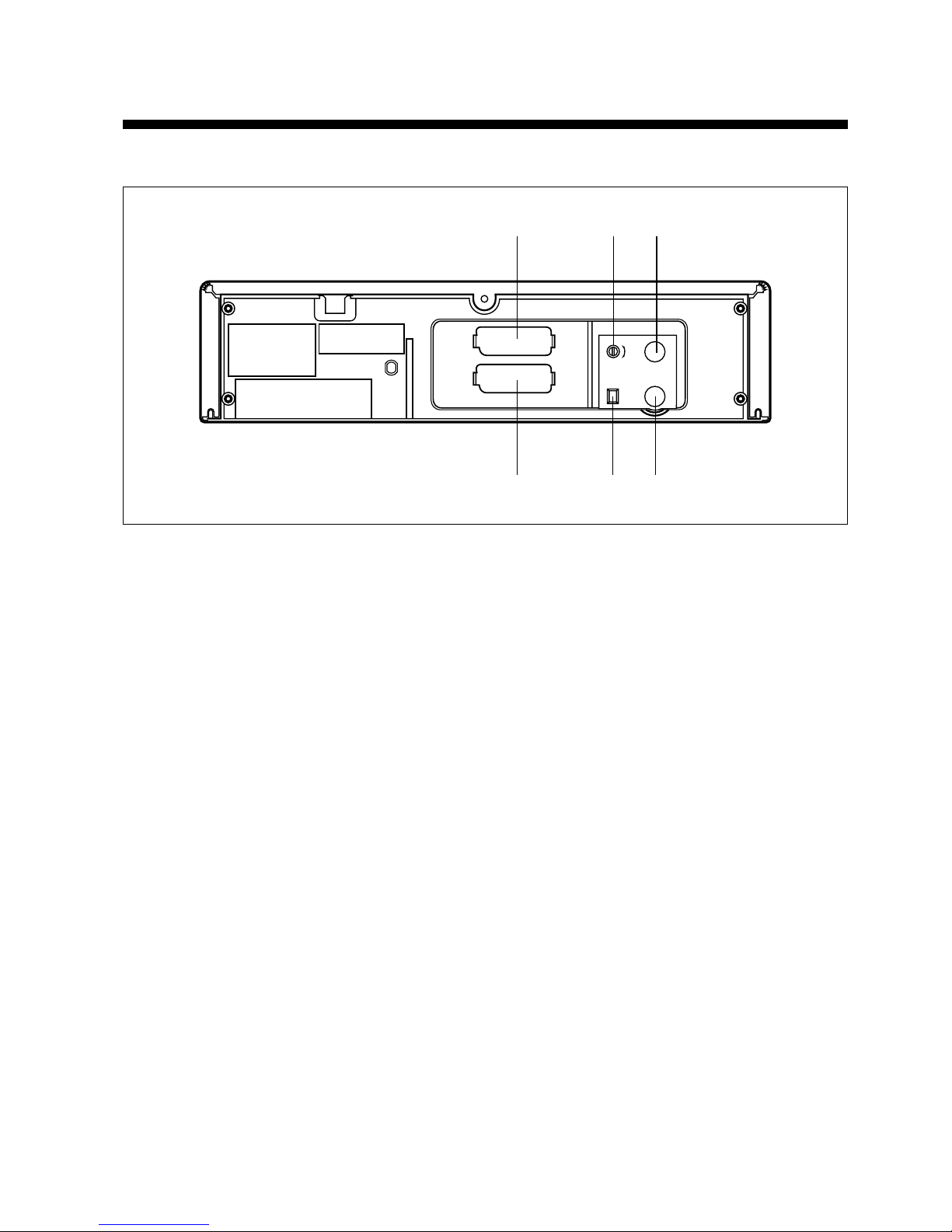

SECTION 8. COMPONENTS LOCATION GUIDE ON PCB (BOTTOM VIEW)

8-1. PCB MAIN.........................................................................................................................................................................71

8-2. PCB POWER.....................................................................................................................................................................72

8-3. PCB PRE AMP (4HEAD)...................................................................................................................................................72

8-4. PCB PRE AMP (2HEAD)...................................................................................................................................................72

8-5. PCB VIDEO.......................................................................................................................................................................73

8-6. PCB IF MODULE..............................................................................................................................................................73

8-7. PCB AV & SCART.............................................................................................................................................................73

8-8. PCB LOGIC.......................................................................................................................................................................74

SECTION 9. DISASSEMBLY

9-1. PACKING ASS'Y...............................................................................................................................................................76

9-2. FRONT PANEL ASSEMBLY.............................................................................................................................................77

9-3. SET TOTAL ASSEMBLY ..................................................................................................................................................80

9-4. INSTRUMENT DISASSEMBLY........................................................................................................................................81

9-5. JIG PCB CONNECTION DIAGRAM.................................................................................................................................89

SECTION 10. ELECTRICAL PART LIST...................................................................................................................90

2