Dave Embedded Systems diDo User manual

HARDWARE MANUAL

ARM Cortex-A8 CPU Module Family

ULTRA Line

D i d o H a r d w a r e M a n u a l v . 1 . 0 . 5

<Page intentionally left blank>

August, 2014 2/78

D i d o H a r d w a r e M a n u a l v . 1 . 0 . 5

Table of Contents

1 Preface.....................................................................................................................................6

1.1 About this manual.............................................................................................................6

1.2 Copyrights/Tra emarks.....................................................................................................6

1.3 Stan ar s..........................................................................................................................6

1.4 Disclaimers.......................................................................................................................6

1.5 Warranty............................................................................................................................6

1.6 Technical Support.............................................................................................................7

1.7 Relate ocuments...........................................................................................................8

1.8 Conventions, Abbreviations, Acronyms............................................................................8

2 Intro uction.............................................................................................................................11

2.1 Pro uct Highlights...........................................................................................................12

2.2 Block DiagramBlock Diagram.........................................................................................13

2.3 Feature Summary...........................................................................................................14

3 Design overview.....................................................................................................................16

3.1 “DaVinci” DM814x / “Sitara” AM387x CPU.....................................................................16

3.2 DDR3 memory bank.......................................................................................................18

3.3 NOR flash bank...............................................................................................................18

3.4 NAND flash bank............................................................................................................18

3.5 Memory Map...................................................................................................................19

3.6 Power supply unit...........................................................................................................19

3.7 CPU mo ule connectors.................................................................................................19

4 Mechanical specifications......................................................................................................21

4.1 Boar Layout...................................................................................................................21

4.2 Connectors......................................................................................................................23

5 System Logic..........................................................................................................................24

5.1 Power..............................................................................................................................24

5.2 PMIC...............................................................................................................................24

5.3 Reset...............................................................................................................................24

5.3.1 MRST (J2.102)........................................................................................................24

5.3.2 PORSTn (J2.109)....................................................................................................24

5.3.3 RSTOUTn (J2.91)....................................................................................................25

5.3.4 CPU_RESETn (J2.15).............................................................................................25

5.3.5 JTAG_TRSTn (J2.100)............................................................................................25

5.4 Voltage monitor...............................................................................................................25

5.5 Boot options....................................................................................................................25

5.5.1 Default boot configuration.......................................................................................26

5.5.2 Boot sequence customization.................................................................................27

5.6 Clock scheme.................................................................................................................27

5.7 Recovery.........................................................................................................................27

5.7.1 JTAG Recovery.......................................................................................................27

5.7.2 UART Recovery.......................................................................................................28

August, 2014 3/78

D i d o H a r d w a r e M a n u a l v . 1 . 0 . 5

5.7.3 SD/MMC Recovery..................................................................................................28

5.8 Multiplexing.....................................................................................................................28

5.9 RTC.................................................................................................................................29

6 Pinout table............................................................................................................................30

6.1 Carrier boar mating connector J1.................................................................................32

6.2 Carrier boar mating connector J2.................................................................................38

6.3 CPU mo ule mount options............................................................................................45

6.4 A itional notes...............................................................................................................46

6.4.1 EN_BCK_LS............................................................................................................46

7 Peripheral interfaces..............................................................................................................47

7.1 Digital Vi eo Output (DVO).............................................................................................47

7.1.1 VOUT0.....................................................................................................................47

7.1.2 VOUT1.....................................................................................................................48

7.2 HDMI...............................................................................................................................49

7.3 Analog SDTV out............................................................................................................50

7.4 Digital Vi eo Input ports..................................................................................................51

7.4.1 VIN0.........................................................................................................................52

7.4.2 VIN1.........................................................................................................................54

7.5 Ethernet ports.................................................................................................................55

7.5.1 EMAC_RMREFCLK................................................................................................56

7.5.2 Ethernet 10/100.......................................................................................................56

7.5.3 Gigabit EMAC..........................................................................................................57

7.6 CAN ports.......................................................................................................................58

7.6.1 DCAN0.....................................................................................................................58

7.6.2 DCAN1.....................................................................................................................58

7.7 UARTs.............................................................................................................................59

7.7.1 UART0.....................................................................................................................59

7.7.2 UART3.....................................................................................................................60

7.7.3 UART5.....................................................................................................................60

7.8 MMC/SD channels..........................................................................................................61

7.8.1 MMC/SD/SDIO0......................................................................................................61

7.8.2 MMC/SD/SDIO1......................................................................................................62

7.8.3 MMC/SD/SDIO2......................................................................................................63

7.9 USB ports........................................................................................................................63

7.9.1 USB0.......................................................................................................................63

7.9.2 USB1.......................................................................................................................64

7.9.3 USB2.......................................................................................................................64

7.9.4 Other USB signals...................................................................................................64

7.10 Touchscreen..................................................................................................................65

7.11 EEPROM.......................................................................................................................65

7.12 Keypa controller..........................................................................................................65

7.13 PCI Express..................................................................................................................66

7.14 SPI buses......................................................................................................................67

August, 2014 4/78

D i d o H a r d w a r e M a n u a l v . 1 . 0 . 5

7.14.1 SPI1.......................................................................................................................67

7.14.2 SPI2.......................................................................................................................68

7.14.3 SPI3.......................................................................................................................68

7.15 I2C buses......................................................................................................................69

7.15.1 I2C2.......................................................................................................................69

7.15.2 I2C3.......................................................................................................................69

7.16 SATA.............................................................................................................................70

7.17 Au io interfaces............................................................................................................70

7.17.1 McASP2.................................................................................................................71

7.18 GPIOs...........................................................................................................................71

7.19 Local Bus......................................................................................................................71

8 Operational characteristics....................................................................................................75

8.1 Maximum ratings.............................................................................................................75

8.2 Recommen e ratings....................................................................................................75

8.3 Power consumption........................................................................................................75

8.3.1 Set 1........................................................................................................................76

8.3.2 Use cases................................................................................................................76

8.4 Heat Dissipation..............................................................................................................77

9 Application notes....................................................................................................................78

Index of Tables

Tab. 1: Relate ocuments........................................................................................................8

Tab. 2: Abbreviations an acronyms use in this manual..........................................................9

Tab. 3: CPU, Memories, Busses..............................................................................................14

Tab. 4: Peripherals...................................................................................................................15

Tab. 5: Electrical, Mechanical an Environmental Specifications............................................15

Tab. 6: DM814x/AM387x comparison......................................................................................18

Tab. 7: DDR2 specifications.....................................................................................................18

Tab. 8: NOR flash specifications..............................................................................................18

Tab. 9: NAND flash specifications............................................................................................19

Tab. 10: ZFF form factor – example of pinout ifferences.......................................................20

Illustration Index

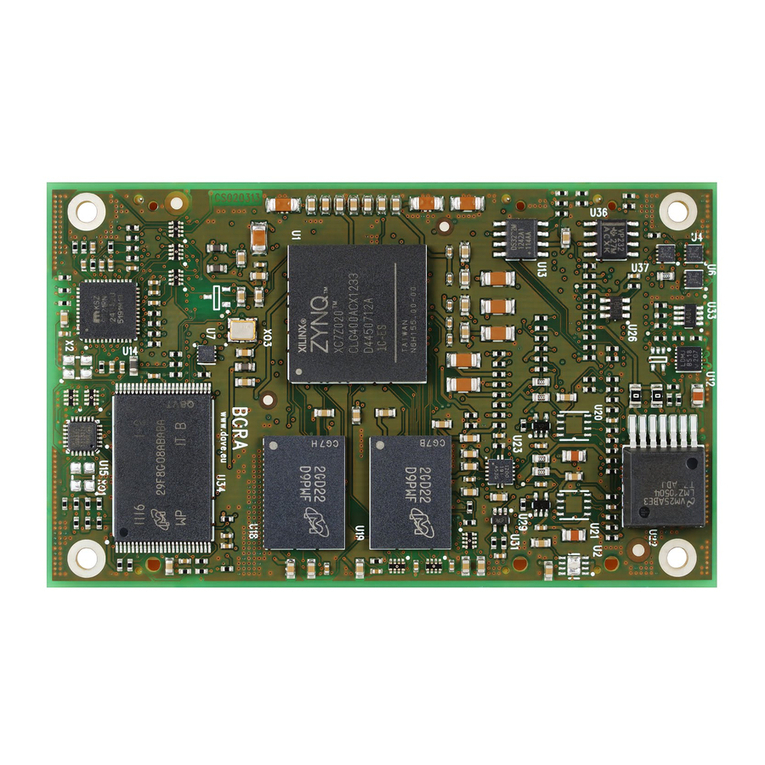

Fig. 1: DIDO CPU mo ule.........................................................................................................11

Fig. 2: DIDO (top-right), NAON (top-left) an MAYA (bottom)...................................................11

Fig. 3: DIDO SOM (top view)....................................................................................................12

Fig. 4: Boar layout - top view..................................................................................................21

Fig. 5: Boar layout - size view.................................................................................................22

Fig. 6: Connectors layout..........................................................................................................23

Fig. 7: Simplifie schematics of EN_BCK2_LS internal pin configuration................................46

August, 2014 5/78

D i d o H a r d w a r e M a n u a l v . 1 . 0 . 5

1 Preface

1.1 About this manual

This Hardware Manual describes the DIDO CPU modules

family design and functions.

Precise speci cations for the Texas Instruments DM814x and

AM387x processors can be found in the CPU datasheets and/or

reference manuals.

1.2 Copyrights/Trademarks

Ethernet® is a registered trademark of XEROX Corporation.

All other products and trademarks mentioned in this manual

are property of their respective owners.

All rights reserved. Speci cations may change any time without

noti cation.

1.3 Standards

DAVE Embedded Systems Srl is certi ed to ISO 9001

standards.

1. Disclaimers

DAVE Embedded Systems does not assume any responsibility

about availability, supplying and support regarding all the

products mentioned in this manual that are not strictly part of

the DIDO CPU module.

DIDO CPU Modules are not designed for use in life support

appliances, devices, or systems where malfunction of these

products can reasonably be expected to result in personal

injury. DAVE Embedded Systems customers who are using or

selling these products for use in such applications do so at their

own risk and agree to fully indemnify DAVE Embedded

Systems for any damage resulting from such improper use or

sale.

1.5 Warranty

DIDO is warranted against defects in material and

August, 2014 6/78

D i d o H a r d w a r e M a n u a l v . 1 . 0 . 5

workmanship for the warranty period from the date of

shipment. During the warranty period, DAVE Embedded

Systems will at its discretion decide to repair or replace

defective products. Within the warranty period, the repair of

products is free of charge as long as warranty conditions are

observed.

The warranty does not apply to defects resulting from improper

or inadequate maintenance or handling by the buyer,

unauthorized modi cation or misuse, operation outside of the

product’s environmental speci cations or improper installation

or maintenance.

DAVE Embedded Systems will not be responsible for any

defects or damages to other products not supplied by DAVE

Embedded Systems that are caused by a faulty DIDO module.

1.6 Technical Support

We are committed to making our product easy to use and will

help customers use our CPU modules in their systems.

Technical support is delivered through email to our valued

customers. Support requests can be sent to

Software upgrades are available for download in the restricted

access download area of DAVE Embedded Systems web site:

http://www.dave.eu/reserved-area. An account is required to

access this area and is provided to customers who purchase the

development kit (please contact [email protected] for

account requests)..

Please refer to our Web site at

http://www.dave.eu/dave-cpu-module-dm814x-dido.html for the

latest product documentation, utilities, drivers, Product

Change Noti cations, Board Support Packages, Application

Notes, mechanical drawings and additional tools and software.

August, 2014 7/78

D i d o H a r d w a r e M a n u a l v . 1 . 0 . 5

1.7 Related documents

Document Location

DAVE Embedded

Systems

Developers Wiki

http://wiki.dave.eu/index.php/Main_Pa

ge

TMS32 DM814x

DaVinci

Technical

Reference Manual

http://www.ti.com/litv/pdf/sprugz8d

DM814x Overview

(on TI Embedded

Processors Wiki )

http://processors.wiki.ti.com/index.ph

p/DM814x_Overview

Integration guide

(on DAVE

Embedded

Systems

Developers Wiki)

http://wiki.dave.eu/index.php/Integrati

on_guide_%28Dido%29

Tab. 1: Related documents

1.8 Conventions, Abbreviations, Acronyms

Abbreviation Definition

BTN Button

DSP Digital Signal Processor

DVO Digital Video Output

GPI General purpose input

GPIO General purpose input and output

GPO General purpose output

HDVPSS HD Video Processing Subsystems

HDVCIP HD Video Image Coprocessing

NELK NAON Embedded Linux Kit

PCB Printed circuit board

August, 2014 8/78

D i d o H a r d w a r e M a n u a l v . 1 . 0 . 5

Abbreviation Definition

RTC Real time clock

SOM System on module

VIP Video Input Port

PMIC Power Management Integrated Circuit

ZFF Z Form Factor

Tab. 2: Abbreviations and acronyms used in this manual

August, 2014 9/78

D i d o H a r d w a r e M a n u a l v . 1 . 0 . 5

Revision History

Version Date Notes

.9. March 2 13 First Draft

.9.1 March 2 13 First Release

.9.2 March 2 13 First Release with DIDO

development kit

Minor fixes

1. . April 2 13 Released with NELK 4. .

Minor fixes

1. .1 May 2 13 Added information on

EMAC_RMREFCLK signal

Minor fixes

1. .2 December 2 13 Fixed JTAG_TDO and JTAG_TCK

pinout table entries

1. .3 January 2 14 Updated pin J2.97 information

Minor fixes

1. .4 April 2 14 SPI2: removed J2.36 from the

muxable signals

Added HDMI CEC and HPDET

information

1. .5 August 2 14 Added EMAC_RMREFCLK

termination resistors information

Updated block diagram

Minor fixes

August, 2014 10/78

Table of contents

Other Dave Embedded Systems Computer Hardware manuals

Dave Embedded Systems

Dave Embedded Systems AXEL ULTRA User manual

Dave Embedded Systems

Dave Embedded Systems ARM Cortex-A9 MPCore User manual

Dave Embedded Systems

Dave Embedded Systems ARM Cortex-A9 MPCore User manual

Dave Embedded Systems

Dave Embedded Systems AXEL LITE User manual

Dave Embedded Systems

Dave Embedded Systems AXEL ULTRA User manual

Popular Computer Hardware manuals by other brands

EMC2

EMC2 VNX Series Hardware Information Guide

Panasonic

Panasonic DV0PM20105 Operation manual

Mitsubishi Electric

Mitsubishi Electric Q81BD-J61BT11 user manual

Gigabyte

Gigabyte B660M DS3H AX DDR4 user manual

Raidon

Raidon iT2300 Quick installation guide

National Instruments

National Instruments PXI-8186 user manual