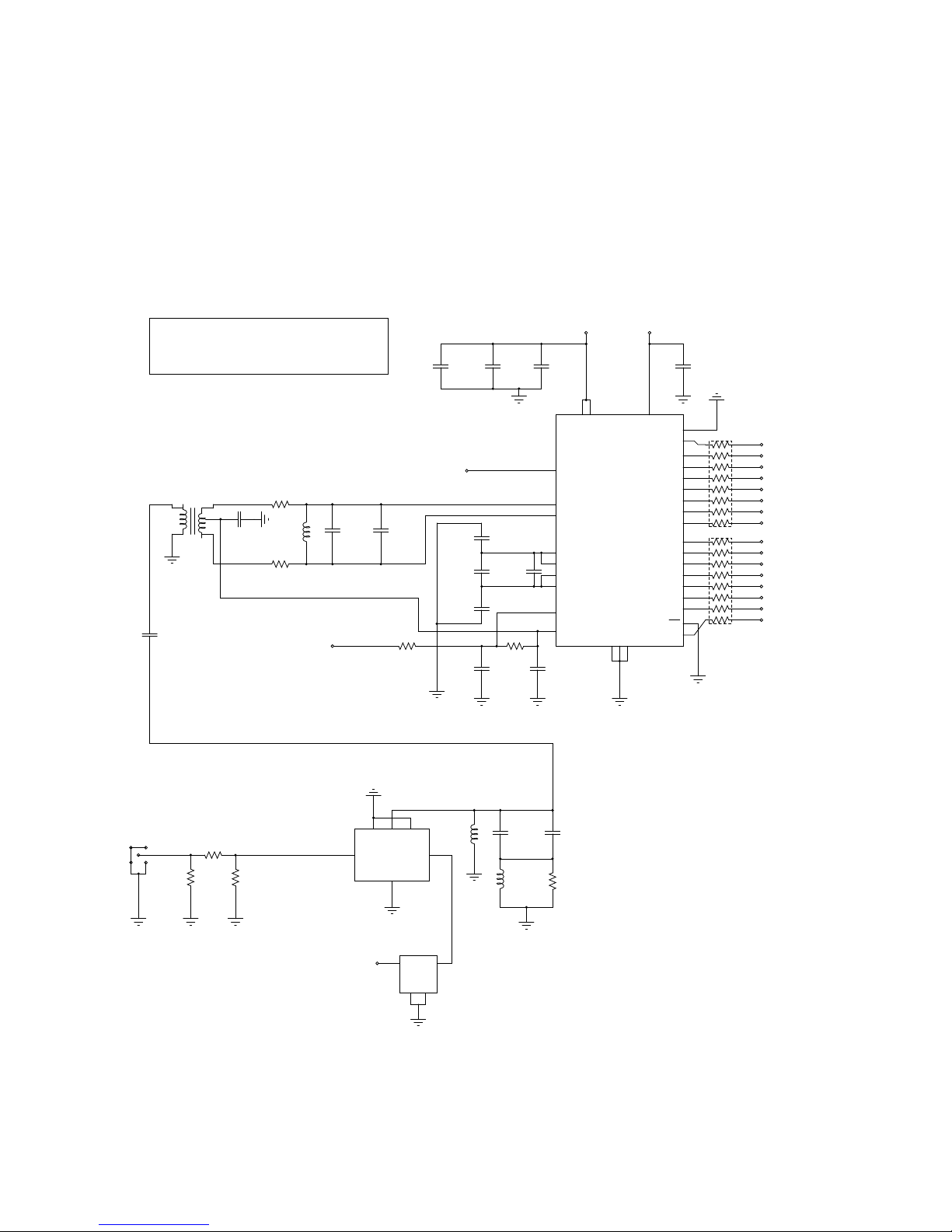

LLRF4.6 Evaluation Board

Dmitry Teytelman

July 7, 2014

Introduction

This document is an update of LLRF4 documentation packet, describing up-to-date in-

formation on 2013 LLRF4.6 revision of the board. The main difference between LLRF4

(last revision 4.2, dated 2009-06-28) and LLRF4.6 is the FPGA. The updated board uses

Spartan-6 FPGA in CS324 package. Normally, the boards are assembled with the largest

and fastest part fitting the footprint — XC6SLX45-3CSG324. While smaller parts can be

used, there is little rationale to do so.

Besides the component changes, several new or improved features have been incorporated:

•Transition from Spartan-3 XC3S1000 to Spartan-6 XC6SLX45;

•New FPGA core supply switcher capable of 2.5 A;

•Power supply jumpers replaced by zero ohm resistors;

•Maximally flat PCB backside for thermal pad mounting on cold plate;

•Reduced parasitics on RF/IF inputs

•High quality stripline LO distribution network, capable of 3 GHz;

•LO 1:8 splitter works to 3.4 GHz;

•LVDS signals routed as 100 Ω differential lines;

•LVDS termination resistors deleted;

•DS1822 thermometer in TO-92 replaced by DS18B20 in SO-8;

•Improved input channel shielding assembly.

The rest of this paper walks through these changes in detail.

FPGA

LLRF4.6 transitions to a more modern Xilinx FPGA. The part is also slightly faster

than the old Spartan-3. A short summary of differences between the two parts is shown

below. Of course, logic cells comparison is imprecise, since Spartan-6 uses new 6-input

LUT architecture. Xilinx uses some fudge factors to convert slice counts to vague “logic

cells”. XC3S1000 XC6SLX45 Notes

Logic cells 17280 43661

Multipliers 24 58 DSP48A1 in S6

BlockRAM 24 116 18kbits

One quirk of LLRF4.6 FPGA setup is that two data bits on high-speed DAC interface are

driven by dual function pins R15 (IO L1P CCLK 2) and V10 (IO L30N GCLK0 USERCCLK 2).

The bitfile must be generated with startup clock set to CCLK (-g StartUpClk:CClk

option of bitgen) for these pins to function as user outputs.

1