Diversified Technology CPB-4612 Operating manual

Artisan Technology Group is your source for quality

new and certied-used/pre-owned equipment

• FAST SHIPPING AND

DELIVERY

• TENS OF THOUSANDS OF

IN-STOCK ITEMS

• EQUIPMENT DEMOS

• HUNDREDS OF

MANUFACTURERS

SUPPORTED

• LEASING/MONTHLY

RENTALS

• ITAR CERTIFIED

SECURE ASSET SOLUTIONS

SERVICE CENTER REPAIRS

Experienced engineers and technicians on staff

at our full-service, in-house repair center

WE BUY USED EQUIPMENT

Sell your excess, underutilized, and idle used equipment

We also offer credit for buy-backs and trade-ins

www.artisantg.com/WeBuyEquipment

REMOTE INSPECTION

Remotely inspect equipment before purchasing with

our interactive website at www.instraview.com

LOOKING FOR MORE INFORMATION?

Visit us on the web at www.artisantg.com for more

information on price quotations, drivers, technical

specications, manuals, and documentation

Contact us: (888) 88-SOURCE | sales@artisantg.com | www.artisantg.com

SM

View

Instra

Diversified Technology, Inc.

CPB4612

Configuration and Maintenance

Guide

Rev 1.2

CPB4612 CPCI Board

with a Intel® Pentium® M

©Copyright 2005 by Diversified Technology, Inc. All rights reserved. Printed in the

United States of America. No part of this publication may be reproduced, stored in a

retrieval system, or transmitted, in any form or by any means, electronic,

mechanical, photocopying, recording, or otherwise without prior permission of the

publisher.

CPB4612 Configuration and Maintenance Guide

ii

Return Shipment Information

If service or repair is required, contact DTI’s Service Department for a Return Material Authorization (RMA)

number and shipping instructions. If the product is out of warranty, or was damaged during shipment, a

purchase order will be required for the repair. The product should be returned in its original shipping

materials. Contact DTI if replacement material is required. Seal the carton securely and ship prepaid to the

following address with the RMA number on the label.

DIVERSIFIED TECHNOLOGY, INC.

Service Department

476 Highland Colony Parkway

P.O. Box 748

Ridgeland, MS 39158

RMA# ________________

To contact the Service Department:

Telephone: (601) 856-4121

Fax: (601) 856-2888

Items determined to be covered under warranty will be returned freight prepaid. Items not in warranty will be

returned freight collect, contact DTI’s Service Department.

CPB4612 Configuration and Maintenance Guide

iii

For Your Safety

CAUTION: The cPB-4612 contains a lithium battery. This battery is not field-replaceable.

There is a danger of explosion if the battery is incorrectly replaced or handled. Do not

disassemble or recharge the battery. Do not dispose of the battery in fire. When the battery

is replaced, the same type or an equivalent type recommended by the manufacturer must be

used. Used batteries must be disposed of according to the manufacturer's instructions.

Return the board to DTI for battery service.

CPB4612 Configuration and Maintenance Guide

iv

Revision History

Date Revision Summary of Corrections

08/31/04 1.0 Initial Release

10/12/04 1.1 Added links throughout manual.

8/19/05 1.2 Removed references to ethernet signal routing.

Update BIOS Section

CPB4612 Configuration and Maintenance Guide

v

Table of Contents

Return Shipment Information...................................................................................................................................ii

For Your Safety...................................................................................................................................................... iii

Revision History......................................................................................................................................................iv

Table of Contents......................................................................................................................................................v

Tables ......................................................................................................................................................................ix

Figures.....................................................................................................................................................................ix

Document Organization............................................................................................................................................x

1INTRODUCTION......................................................................................................... 1

1.1 Product Definition................................................................................................................................................2

1.2 Features.................................................................................................................................................................4

1.3 Functional Blocks.................................................................................................................................................4

1.3.1 CompactPCI/PSB Architecture............................................................................................................................5

1.3.2 Processor..............................................................................................................................................................6

1.3.3 Chipset.................................................................................................................................................................6

1.3.4 PCI-to-PCI Bridge ...............................................................................................................................................6

1.3.5 Memory and I/O Addressing................................................................................................................................7

1.3.6 Power Ramp Circuitry .........................................................................................................................................7

1.3.7 Rear-Panel I/O .....................................................................................................................................................7

1.3.8 Video....................................................................................................................................................................7

1.3.9 PCI Mezzanine Card (PMC) Interface.................................................................................................................7

1.3.10 Dual 10/100/1000 Ethernet Interfaces .................................................................................................................7

1.3.11 10/100 Ethernet Interface.....................................................................................................................................8

1.3.12 IDE Hard Drive....................................................................................................................................................8

1.3.13 Serial I/O..............................................................................................................................................................8

1.3.14 Interrupts..............................................................................................................................................................8

1.3.15 Counter/Timers....................................................................................................................................................9

1.3.16 DMA....................................................................................................................................................................9

1.3.17 Real-Time Clock..................................................................................................................................................9

1.3.18 Reset ....................................................................................................................................................................9

1.3.19 Two-Stage Watchdog Timer................................................................................................................................9

1.3.20 Universal Serial Bus (USB)...............................................................................................................................10

1.3.21 System Environmental Monitor.........................................................................................................................10

1.3.22 LED Indicators...................................................................................................................................................10

1.4 Software ..............................................................................................................................................................10

2GETTING STARTED ................................................................................................ 11

2.1 Unpacking...........................................................................................................................................................12

2.2 System Requirements.........................................................................................................................................12

2.2.1 BIOS Version.....................................................................................................................................................12

2.2.2 Connectivity.......................................................................................................................................................12

2.2.3 Electrical and Environmental.............................................................................................................................12

2.3 Memory Configuration......................................................................................................................................13

2.4 I/O Configuration...............................................................................................................................................15

2.5 Connectors..........................................................................................................................................................16

2.6 Jumper Options..................................................................................................................................................16

2.7 BIOS Configuration Overview..........................................................................................................................16

CPB4612 Configuration and Maintenance Guide

vi

2.8 Operating System Installation...........................................................................................................................17

3CONFIGURATION.................................................................................................... 19

3.1 Switch Descriptions............................................................................................................................................21

3.1.1 PB1 (Reset)........................................................................................................................................................21

3.1.2 J16-1 (BKT-GND to GND) ...............................................................................................................................21

3.1.3 J16-2 (+12V to J5-pin D1).................................................................................................................................22

3.1.4 J16-3 (+5V PMC I/O)........................................................................................................................................22

3.1.5 J16-4 (IMPI Disable) .........................................................................................................................................22

3.1.6 J17-1 (Not Used)................................................................................................................................................22

3.1.7 J17-2 (CMOS Clear)..........................................................................................................................................22

3.1.8 J17-3 (Disable Onboard Video).........................................................................................................................23

3.1.9 J17-4 (Manufacture Test Mode) ........................................................................................................................23

3.1.10 J18 (Ejector Switch)...........................................................................................................................................23

4RESET...................................................................................................................... 24

4.1 Reset Types and Sources....................................................................................................................................25

4.1.1 Hard Reset Sources............................................................................................................................................25

4.1.2 Soft Reset Sources .............................................................................................................................................25

4.1.3 Backend Power Down Sources..........................................................................................................................25

4.1.4 NMI Sources......................................................................................................................................................26

5SYSTEM MONITORING AND CONTROL................................................................ 27

5.1 Monitoring and Control Functions...................................................................................................................28

Figure 5.1: Packet Structure ...........................................................................................................................................28

5.2 IPMB...................................................................................................................................................................28

5.3 Field Replaceable Unit (FRU) Information......................................................................................................29

5.4 Sensors.................................................................................................................................................................29

5.5 Firmware Updates..............................................................................................................................................29

5.6 SMBus Address Map .........................................................................................................................................29

6IDE CONTROLLER .................................................................................................. 30

6.1 Features of the IDE Controller .........................................................................................................................31

6.2 Disk Drive Support.............................................................................................................................................31

6.2.1 Primary IDE Channel.........................................................................................................................................31

6.2.2 Secondary IDE Channel.....................................................................................................................................31

6.3 IDE I/O Mapping ...............................................................................................................................................31

6.4 IDE Device Drivers.............................................................................................................................................31

7WATCHDOG TIMER................................................................................................. 32

7.1 Watchdog Timer Overview ...............................................................................................................................33

7.2 PCI Configuration Registers.............................................................................................................................33

7.2.1 Base Address Register (10h)..............................................................................................................................33

7.2.2 WDT Configuration Register (60h)...................................................................................................................34

7.2.3 WDT Lock Register (68h) .................................................................................................................................34

7.3 Memory Mapped Registers ...............................................................................................................................35

7.3.1 Preload Value 1 (BAR+00h)..............................................................................................................................35

CPB4612 Configuration and Maintenance Guide

vii

7.3.2 Preload Value 2 (BAR+04h)..............................................................................................................................35

7.3.3 General Interrupt Status (BAR+08h).................................................................................................................36

7.3.4 Reload Register (BAR+0Ch).............................................................................................................................36

7.4 Using the Watchdog in an Application.............................................................................................................37

7.4.1 WDT Unlocking and Programming Sequence...................................................................................................37

7.4.2 Watchdog Reset.................................................................................................................................................37

7.4.2.1 Load Preload Values..........................................................................................................................................37

7.4.2.2 Enabling the Watchdog Reset............................................................................................................................37

7.4.2.3 Reloading the Watchdog....................................................................................................................................37

8SYSTEM BIOS.......................................................................................................... 38

8.1 BIOS Upgrade and Recovery.............................................................................................................................39

8.1.1 Flash Utility Program.........................................................................................................................................39

8.1.2 BIOS Recovery..................................................................................................................................................39

8.2 BIOS Configuration Overview..........................................................................................................................39

8.2.1 Boot Menu .........................................................................................................................................................40

8.2.2 ROM Utilities ....................................................................................................................................................41

8.2.3 System Summary...............................................................................................................................................43

8.2.4 System Setup......................................................................................................................................................44

8.2.5 IDE Config.........................................................................................................................................................46

8.2.6 Hard Disk Setup.................................................................................................................................................47

8.2.7 Boot Order .........................................................................................................................................................49

8.2.8 Peripherals .........................................................................................................................................................51

8.2.9 USB Configuration ............................................................................................................................................53

8.2.10 MISC Config......................................................................................................................................................55

8.2.11 Event Logging....................................................................................................................................................57

8.2.12 Security/Virus....................................................................................................................................................58

8.2.13 Exit.....................................................................................................................................................................59

8.3 Plug and Play (PnP) ...........................................................................................................................................60

8.3.1 Resource Allocation...........................................................................................................................................60

8.3.2 PnP ISA Auto-configuration..............................................................................................................................60

8.3.3 PCI Auto-configuration .....................................................................................................................................60

8.3.4 Legacy ISA Configuration.................................................................................................................................61

8.3.5 Automatic Detection of Video Adapters............................................................................................................61

8.4 Console Redirection ...........................................................................................................................................61

8.5 System Management BIOS (SMBIOS).............................................................................................................61

8.6 POST CODE LEDS ...........................................................................................................................................61

ASPECIFICATIONS.................................................................................................... 64

A.1 Electrical and Environmental ...........................................................................................................................64

A.2 Absolute Maximum Ratings..............................................................................................................................64

A.2.1 DC Operating Characteristics ............................................................................................................................64

A.2.2 Battery Backup Characteristics..........................................................................................................................65

A.2.3 Operating Temperature......................................................................................................................................65

A.3 Reliability............................................................................................................................................................65

A.4 Mechanical..........................................................................................................................................................65

A.4.1 Board Dimensions and Weight..........................................................................................................................66

BCONNECTORS......................................................................................................... 68

B.1 Connector Locations..........................................................................................................................................69

CPB4612 Configuration and Maintenance Guide

viii

B.2 J15 (CompactPCI Bus Connector)....................................................................................................................71

B.3 J11 (CompactPCI Bus Connector)....................................................................................................................72

B.4 J8 (CompactPCI Connector).............................................................................................................................73

B.5 J2 (Rear Panel I/O CompactPCI Connector) ..................................................................................................74

B.6 J1 (10/100 Ethernet)...........................................................................................................................................75

B.7 J4 (Universal Serial Bus 0 connector)...............................................................................................................75

B.8 J3 (COM1 Serial Port).......................................................................................................................................76

B.9 J6, J7, J9, J10 (64bit/66Mhz PCI Mezzanine Connectors) .............................................................................76

B.10 J12 and J13 (32bit/33Mhz PCI Mezzanine Connectors).................................................................................80

B.11 J14 (IDE Connector)..........................................................................................................................................82

CTHERMAL CONSIDERATIONS ............................................................................... 84

C.1 Thermal Requirements......................................................................................................................................85

C.2 Temperature Monitoring...................................................................................................................................85

DDATASHEET REFERENCE ..................................................................................... 88

D.1 CompactPCI .......................................................................................................................................................89

D.2 Ethernet...............................................................................................................................................................89

D.3 Intel 855GME Chipset .......................................................................................................................................89

D.4 Pentium M processor (FCBGA Package).........................................................................................................89

D.5 PMC Specification..............................................................................................................................................90

D.6 Super I/O.............................................................................................................................................................90

EAGENCY APPROVALS............................................................................................ 92

E.1 CE Certification..................................................................................................................................................92

E.2 NEBS compliance...............................................................................................................................................92

E.3 Safety...................................................................................................................................................................92

E.4 Electro-magnetic Compatibility........................................................................................................................92

E.5 Regulatory Information.....................................................................................................................................92

E.5.1 FCC (USA)........................................................................................................................................................92

E.5.2 Industry Canada (Canada)..................................................................................................................................93

FCRT SPECIFICATIONS............................................................................................ 94

CPB4612 Configuration and Maintenance Guide

ix

Tables

Jumper Cross-Reference Table........................................................................................................................ 20

Connector Assignments .................................................................................................................................... 68

J15 CompactPCI Bus Connector Pin out.......................................................................................................... 71

J11 CompactPCI Bus Connector Pin out.......................................................................................................... 72

J8 Connector Pin out......................................................................................................................................... 73

J2 Rear Panel I/O Connector Pin out................................................................................................................ 74

J4 Universal Serial Bus 0 Connector Pin out .................................................................................................... 75

Thermal Requirements...................................................................................................................................... 85

Figures

CPB-4612 Faceplate........................................................................................................................................... 3

Functional Block Diagram ................................................................................................................................... 5

Memory Address Map Example........................................................................................................................ 14

I/O Address Map ............................................................................................................................................... 15

Setup Screen .................................................................................................................................................... 17

Default Jumper Configuration ........................................................................................................................... 21

PCB Dimensions ............................................................................................................................................... 66

CPB-4612 Connectors Locations (Topside) ..................................................................................................... 69

Backplane Connectors - Pin Locations ............................................................................................................. 70

CPB4612 Configuration and Maintenance Guide

x

Document Organization

This document describes the operation and use of the CPB-4612 Computer Processor Board with an Intel®

Pentium® M. The following topics are covered in this document.

Chapter 1, "Introduction," introduces the key features of the CPB-4612. This chapter includes a product

definition, a list of product features, and a functional block diagram with a brief description of each block. This

chapter can be used to compare the features of the CPB-4612 against the needs of a specific application.

Chapter 2, "Getting Started," provides unpacking instructions and initial setup information for the CPB-4612.

This chapter summarizes configuration information and should be read before using the board.

Chapter 3, "Configuration," describes the jumper settings on the CPB-4612. This chapter details factory

default settings and provides information about tailoring the board to the needs of specific applications.

Chapter 4, "Reset," discusses the reset types and reset sources available on the CPB-4612.

Chapter 5, "System Monitoring and Control," lists various system monitoring and control features available

on the CPB-4612.

Chapter 6, "IDE Controller," provides an introduction to the CPB-4612's IDE Controller. This chapter covers

drive configuration, IDE I/O mapping, device drivers, and the CPB-4612's support for internal and external

disk drives.

Chapter 7, "Watchdog Timer," explains the operation of the CPB-4612's watchdog timer. Sample code is

provided to illustrate how the watchdog's functions are used in an application.

Chapter 8, "System BIOS," discusses recovery from and correction of a corrupted BIOS.

Appendix A, "Specifications," contains the electrical, environmental, and mechanical specifications for the

CPB-4612.

Appendix B, “Connectors,” This chapter provides a connector location illustration and connector pin out

tables. A detailed description and pin out for each connector is given.

Appendix C, "Thermal Considerations," describes the thermal requirements for reliable operation of the

CPB-4612.

Appendix D, "Datasheet Reference," provides links to Websites with information about many of the devices

and technologies used in the CPB-4612.

Appendix E, "Agency Approvals," presents UL, CE, and FCC agency approval and certification information

for the CPB-4612.

Appendix F, "CRT Specifications,” identified features of the CRT4612 Rear Transition Module (RTM).

1

Chapter 1

1

1 Introduction

This chapter provides an introduction to the CPB-4612 including a product definition, a list of product

features, and a functional block diagram with descriptions of each block.

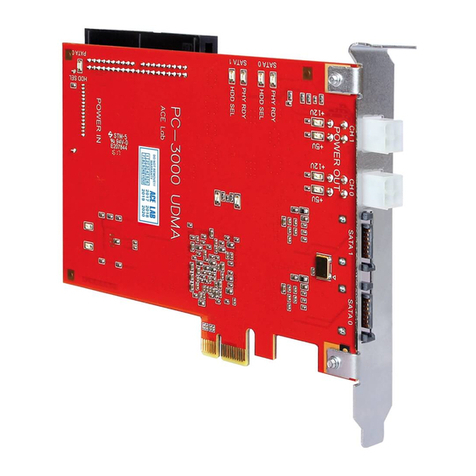

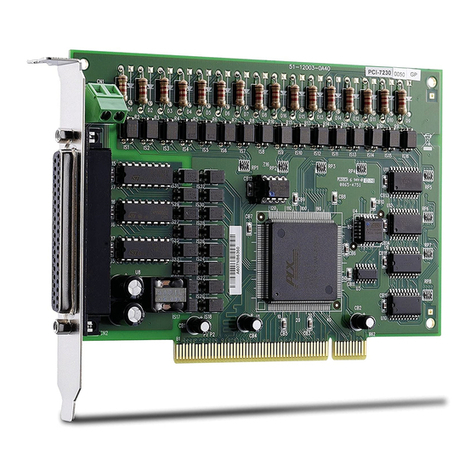

The "cPB-4612 Faceplate" illustration identifies the connectors, indicators, and switches available on the

cPB-4612's faceplate. Optional rear-panel transition boards are available to extend various faceplate

features to a system's rear-panel. For more information about compatible rear-panel transition boards,

see Appendix F.

The CPB-4612 is a 64-bit compliant CompactPCI Pentium M single board computer designed to operate

in either a system slot or a peripheral slot. The cPB-4612 provides Ethernet integration using the Intel

82559 10/100 Base-T PCI Ethernet controller and the Intel 82546EB Fast Gigabit Ethernet Multifunction

PCI Controller. The CPB4612 provides support for IDE hard drives, serial ports, and USB ports. I/O

connections are available at the rear of the chassis using one of DTI’s cRT4612 rear-panel I/O modules.

The CPB-4612 is fully compliant with both the CompactPCI standard and the PICMG 2.16 packet

switching standard.

2

1.1 Product Definition

The cPB-4612 Computer Processor Board is a single board computer designed to work as a modular

component in a CompactPCI system. It utilizes the Intel®Pentium®M processor in a micro FCBGA package

along with dual Gigabit Ethernet controllers and the latest in memory and I/O technology to provide an

inexpensive, yet fast and reliable PICMG 2.16 board. The cPB-4612 is CompactPCI Packet Switching

Backplane (CompactPCI/PSB) compatible and draws its power from the J1 and J2 connectors. The cPB-

4612 includes an Intelligent Platform Management Bus (IPMB) for system management along with IPMI v1.5

compatible firmware.

The cPB-4612 occupies a single 6U high Eurocard slot. The board can be used in either a system master

slot or in a peripheral slot. Though the cPB-4612 is highly integrated, its capabilities can be extended with

pluggable PMC modules. DTI also provides a rear transition board, the cRT-4612, that compliments the

cPB-4612 to extend I/O access to the rear of a system. For more information about PMC options and

accessories contact your DTI sales representative.

3

CPB-4612 Faceplate

Ejector Handle

Ejector Handle

PMC

PMC

10/100 Ethernet

COM RS-232

Serial Port

USB

Hotswap LED Reset Switch

4

1.2 Features

There are two SKU's of the cPB-4612. The first is the cPB-4612, which has a 64bit/66Mhz PMC site and a

32bit/33Mhz PMC site. . The second is the cPB-4612 w/ IDE, which has a 64bit/66Mhz PMC site and an

on-board 2.5” HDD IDE connector. Other features include:

•CompactPCI Specification, PICMG 2.0, Version 2.1** compliant

•CompactPCI Specification, PICMG 2.16, Version 1.0** compliant

•6U single-slot CompactPCI form factor

•Mobile Intel Pentium M, micro FCBGA package

•Intel®855GME GMCH and 6300ESB ICH

•Integrated Intel Extreme Graphics 2 controller

•Dual 10/100/1000 Mb/s Ethernet (both at the J3 backplane connector to support PICMG 2.16)

•10/100 Mb/s Ethernet (available at the front panel)

•1 MB of Level 2 cache

•400 MHz front side bus

•Socketed 256 MB, 512 MB, 1 GB, or 2GB of DDR SDRAM memory at 200, 266, or 333 MHz

•Dual stage watchdog timer

•IPMI support

•Option for either a single on-board PCI Mezzanine Card (PMC) slot (32-bit / 33MHz) or a primary IDE

channel that supports an on-board 2.5 inch hard disk

•64bit / 66Mhz @ 3.3V PCI Mezzanine Card (PMC) slot

•Two 16C550 RS-232 serial ports (COM1 available at the faceplate, COM2 available through the J5

backplane connector)

•Push Button Reset on the front panel

•1 USB on front panel, 2 USB ports available via RTM

•Rear-Panel I/O Availability (at J5) includes the following:

–Secondary IDE channel

–Serial ATA

–Two USB ports

–VGA video

–Serial Port

•Support for Microsoft Windows 2000/XP, Red Hat Linux, and Solaris 8/9

•Standard AT* Systems include:

– Two enhanced interrupt controllers (8259)

– Three counter/timers (one 8254)

– Real-time clock/CMOS RAM (146818B)

– Two enhanced DMA controllers (8237)

1.3 Functional Blocks

The following topics provide overviews of the cPB-4612's main features, some of which are shown in the

functional block diagram below.

5

Functional Block Diagram

1.3.1 CompactPCI/PSB Architecture

The cPB-4612 is designed to operate in a PICMG 2.0 CompactPCI backplane. If the system is placed in a

system slot, the bridge will automatically configure itself as a transparent bridge, and the board will perform

as the host. If the board is placed in a peripheral slot, the bridge will automatically configure itself as a non-

transparent bridge, and the board will perform as a peripheral device.

When used in accordance with the CompactPCI Packet Switching Backplane Specification, PICMG 2.16,

Version 1.0, the cPB-4612 functions as a "Dual Link Port Node" board. The cPB-4612 can be connected to a

6

system's fabric-switched Link Ports A and B, and can be inserted into system or peripheral slots. The cPB-

4612 is keyed for insertion into compatible slots.

The "CompactPCI" topic in Appendix D contains a link to the PCI Industrial Computer Manufacturers Group.

1.3.2 Processor

The cPB-4612 uses the Mobile Pentium M in a micro FCBGA package. The 1MB or 2MB on-die transfer L2

cache is integrated with the CPU, eliminating the need for separate components and improving

performance. The FCBGA package Pentium M processor also operates with a 400 MHz Processor Side

Bus for very fast access to memory and data.

The "Mobile Pentium M (FCBGA Package)" topic in Appendix D contains a link to the datasheet for the

processor.

1.3.3 Chipset

The Intel 855GME chipset consists of two controller hubs. The 855GME Memory Controller Hub (MCH)

supports a 400MHz system bus, DDR200/266/333 memory, and an integrated graphics solution w/Intel

Extreme Graphics 2 technology. The 6300ESB I/O Controller Hub (ICH4) makes a direct connection to the

memory for faster access to peripherals. It provides the features and bandwidth required for applied

computing-usage models. The following is a list of features of the 855GME chipset:

•Designed, validated, and optimized for the Intel Pentium M with NetBurst™ micro-architecture

using proven and established building blocks

•400MHz system bus delivers a high-bandwidth connection between the Intel Pentium M and the

platform, providing 3x the bandwidth over platforms based on Intel® Pentium® III processors

•USB controllers provide high performance peripherals with 480Mbps of bandwidth. This results

in a significant increase over previous integrated 1-4 port hubs at 12Mbps

•Dual UARTs

•Serial ATA

•64bit/66Mhz PCI-X bus

•32bit/33Mhz PCI bus

•Dual Ultra ATA/100 controllers, coupled with the Intel®Application Accelerator - a performance

software package - support faster IDE transfers to storage devices

•The Intel® Application Accelerator software provides additional performance over native ATA

drivers. The Intel Application Accelerator improves system performance by improving I/O

transfer rates and enables faster O/S load time resulting in accelerated boot times

•Embedded lifecycle support

The "Intel 855GME Chipset" topic in Appendix D contains a link to information about the chipset.

1.3.4 PCI-to-PCI Bridge

The cPB-4612 has a 64bit/66Mhz PCI-X bridge to the CompactPCI backplane. The bridge will configure

itself as a transparent bridge when the board is in a system slot, so that the cPB-4612 can be the system

host. If the cPB-4612 is placed in a peripheral slot, the bridge configures itself as a non-transparent bridge,

and will show up as a PCI device to the host. This allows use of the board in either a system or peripheral

slot.

7

1.3.5 Memory and I/O Addressing

The cPB-4612 supports up to 2GB of DDR333/266/200 via two right-angled SODIMM sockets. Memory

can be purchased from DTI separately.

See the "Memory Configuration" and "I/O Configuration" topics in Chapter 2 for more information.

1.3.6 Power Ramp Circuitry

The cPB-4612 features a power controller with power ramp circuitry that allows the board's voltages to be

ramped in a controlled fashion. The power ramp circuitry eliminates large voltage or current spikes caused

by hot swapping boards. This controlled ramping is a requirement of the CompactPCI Hot Swap

Specification**, PICMG 2.1, Version 1.0.

The cPB-4612's power controller unconditionally resets the board when it detects that the 3.3V, 5V, and 12V

supplies are below an acceptable operating limit. Minimum voltage thresholds for the cPB-4612 are: 4.75V

(5V supply), 3.0V (3.3V supply), and 10.0V (+12V supply).

1.3.7 Rear-Panel I/O

The following I/O signals are available from the J5 connector at the back of the cPB-4612. These signals are

available for use by a rear panel transition board such as the cRT-4612.

•Serial port (COM2)

•USB Ports 2 and 3

•Secondary IDE channel

•Serial ATA channel

•Video

1.3.8 Video

The cPB-4612 supports VGA video using Intel’s 855GME video interface. The video is accessed through

the CompactPCI J5 connector. The 855GME can share up to 32MB of system memory with the internal

video.

The onboard video from the Intel 855GME may be disabled by a jumper setting. This will allow use of a PCI

video card only. If the onboard video is enabled and a PCI video card is installed, the PCI video card will be

the primary video source.

The Intel 855GME Chipset topic contains a link to the datasheet for this device.

1.3.9 PCI Mezzanine Card (PMC) Interface

The cPB-4612 provides a 64bit/66Mhz PMC site and a 32bit/33Mhz PMC site, both with front panel access.

The 64bit/66Mhz PMC site is only 3.3V tolerant. The 32bit/33Mhz can be configured to be either 3.3V or 5V

via a jumper setting. Voltage keys are also provided to prevent inadvertently placing a PMC card on PMC

site that does not support its VI/O voltage.

The cPB-4612 w/ IDE provides a 64bit/66Mhz PMC site and a 2.5” HDD IDE connector. The 64bit/66Mhz

PMC site is only 3.3V tolerant. Voltage keys are also provided to prevent inadvertently placing a PMC card

on PMC site that does not support its VI/O voltage.

The "PMC Specification" topic in Appendix D contains a link to the sponsoring organization for the PMC

specification.

1.3.10 Dual 10/100/1000 Ethernet Interfaces

The cPB-4612 provides two 10/100/1000BaseTx Ethernet channels (ENET A and ENET B) through the

Intel 82546EB Fast Gigabit Ethernet Multifunction PCI Controller. The 82546EB consists of both the Media

8

Access Controller (MAC) and the physical layer (PHY) interface combined into a single component solution.

Both Ethernet Channels are directed to the rear connector at J3 for PICMG 2.16 support.

The "Ethernet" topic in Appendix D contains links to the datasheets for the Ethernet devices used on the

cPB-4612.

1.3.11 10/100 Ethernet Interface

The cPB-4612 supports one 10/100 Base-TX Ethernet interface. The Intel 82559EM Ethernet controller

provides this interface. The NIC address programmed into the controller is located on labels on the board.

Link and activity LED signals are on the front panel at the RJ-45 connector.

The "Ethernet" topic in Appendix D contains links to the datasheets for the Ethernet devices used on the

cPB-4612.

1.3.12 IDE Hard Drive

The cPB-4612 w/IDE supports an onboard ATA/100 2.5” IDE interface. This can be used to connect a 2.5”

hard drive. The IDE interface is implemented using Intel’s 6300ESB I/O Controller Hub (ICH). Note that the

onboard 2.5” IDE connector is not present on versions of the board that support the 33MHz/32 bit PMC site.

All versions of the cPB-4612 supports a second ATA/100 IDE interface through the CompactPCI J5

connector. The IDE interface is implemented using Intel’s 6300ESB I/O Controller Hub (ICH).

All versions of the cPB-4612 supports a Serial ATA/150 interface through the CompactPCI J5 connector.

The IDE interface is implemented using Intel’s 6300ESB I/O Controller Hub (ICH).

Both the 2.5” IDE drive connector and 33Mhz/32bit PMC site cannot both be present at the same time, since

they are in the same physical space on the board. Which one is populated depends on the version of the

board.

See Chapter 6, "IDE Controller", for more information.

1.3.13 Serial I/O

The cPB-4612 provides support for two RS-232 compatible serial ports. COM1 is accessible at the

faceplate through a 9-pin DSUB connector. This port is typically used for test access. COM2 is available at

the J5 Rear Panel I/O connector.

The serial port interface is implemented using Intel’s 6300ESB I/O Controller Hub (ICH).

1.3.14 Interrupts

Two enhanced, 8259-style interrupt controllers provide the cPB-4612 with a total of 15 interrupt inputs.

Interrupt controller features include support for:

•Level-triggered and edge-triggered inputs

•Individual input masking

•Fixed and rotating priorities

Interrupt sources include:

•Counter/Timers

•Serial I/O

•Keyboard

•Floppy disk

•IDE interface

9

•Real-Time Clock

•On-board PCI devices

Enhanced capabilities include the ability to configure each interrupt level for active high-going edge or active

low-level inputs.

The cPB-4612's interrupt controllers reside in the 6300ESB device. The "Intel 855GME Chipset" topic in

Appendix D provides a link to the datasheet for this device.

1.3.15 Counter/Timers

Three 8254-style counter/timers, as defined for the PC/AT, are included on the cPB-4612. Operating modes

supported by the counter/timers include:

•Interrupt on count

•Frequency divider

•Software triggered

•Hardware triggered

•One shot

The cPB-4612's Counter/Timers reside in the Intel 6300ESB device. The "Intel 855GME Chipset" topic in

Appendix D provides a link to the datasheet for this device.

1.3.16 DMA

Two cascaded 8237-style DMA controllers are provided on the cPB-4612 for use by the on-board

peripherals.

The cPB-4612's DMA controllers reside in the Intel 6300ESB device. The "Intel 855GME Chipset" topic in

Appendix D provides a link to the datasheet for this device.

1.3.17 Real-Time Clock

The real-time clock performs timekeeping functions and includes 256 bytes of general-purpose, battery-

backed, CMOS RAM. Timekeeping features include an alarm function, a maskable periodic interrupt, and a

100-year calendar. The system BIOS uses a portion of this RAM for BIOS setup information.

The cPB-4612's Real-Time Clock resides in the Intel 6300ESB device. The "Intel 855GME Chipset" topic in

Appendix D provides a link to the datasheet for this device.

1.3.18 Reset

The push-button reset on the cPB-4612's faceplate functions as a "Hard Reset". See Chapter 4, "Reset," for

more information about reset sources for the cPB-4612.

1.3.19 Two-Stage Watchdog Timer

The watchdog timer optionally monitors system operation and is programmable for different timeout periods

(from 1 microsecond to 10 minutes). It is a two-stage watchdog, meaning that it can be enabled to produce a

system management interrupt (SMI) or an IRQ (APIC 1, INT 10) before it generates a Reset. Failure to

strobe the watchdog timer within the programmed time period may result in an SMI, a reset request, or both.

A register bit can be read to indicate if the watchdog timer caused the reset event. This watchdog timer

register is not cleared on power-up, enabling system software to take appropriate action if the watchdog

generated the reboot.

See Chapter 7, "Watchdog Timer," for more information, including sample code.

Table of contents