RA8804 CE

ETM60E-02

Table of Contents

1. Overview...................................................................................................................................................... 1

2. Block Diagram............................................................................................................................................. 1

3. Terminal description.................................................................................................................................... 2

3.1. Terminal connections.................................................................................................................................................2

3.2. Pin Functions.............................................................................................................................................................2

4. Absolute Maximum Ratings ........................................................................................................................ 3

5. Recommended Operating Conditions......................................................................................................... 3

6. Frequency Characteristics .......................................................................................................................... 3

7. Electrical Characteristics............................................................................................................................. 4

7.1. DC Characteristics.....................................................................................................................................................4

7.2. AC characteristics......................................................................................................................................................5

8. Use Methods............................................................................................................................................... 6

8.1. Description of Registers.............................................................................................................................................6

8.1.1. Write/Read and Bank Select..........................................................................................................................6

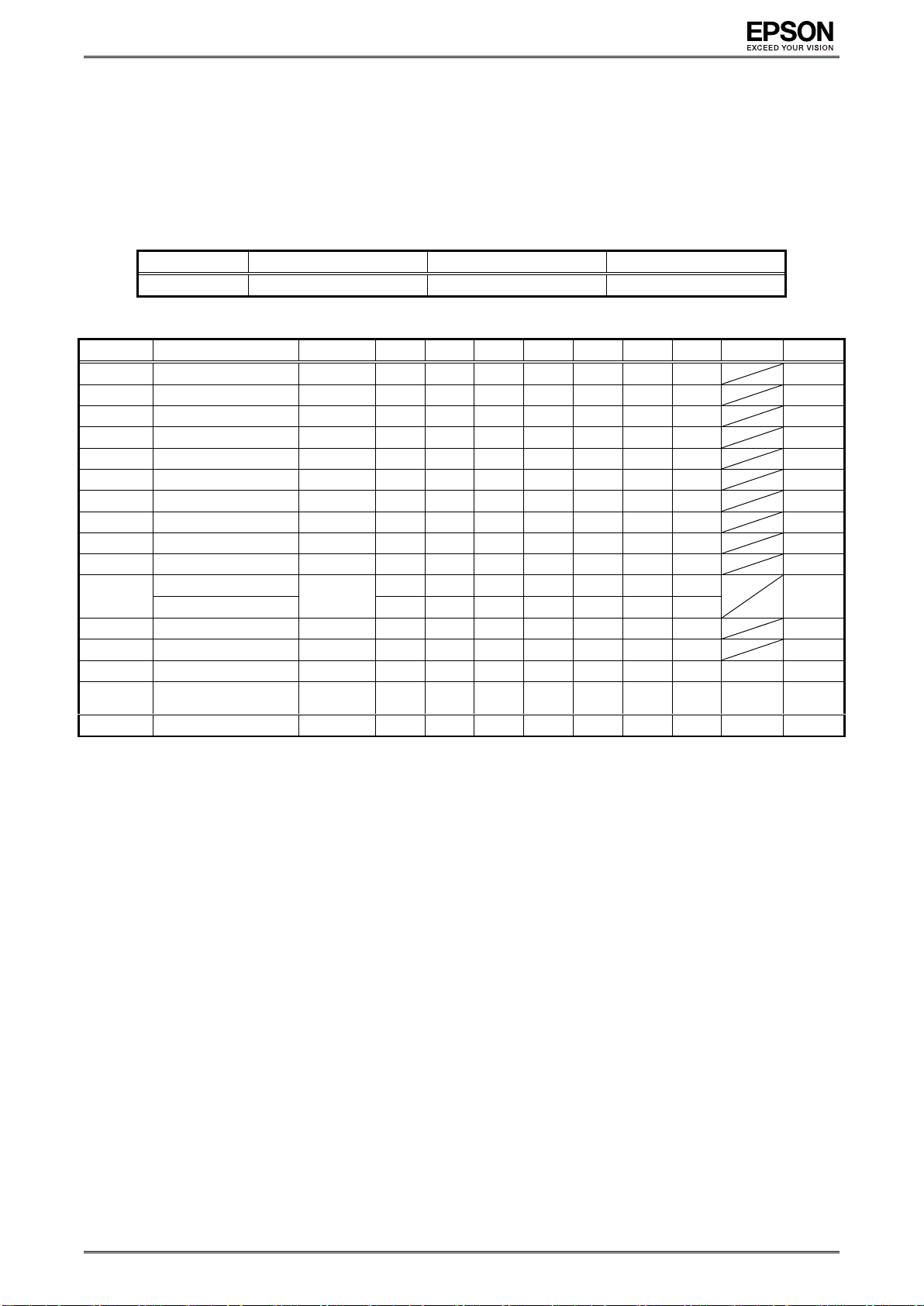

8.1.2. Register table (Basic time and calendar register)...........................................................................................6

8.1.3. Register table (Time stamp, EVIN, SOUT, Timer)..........................................................................................7

8.1.4. Quick Reference ............................................................................................................................................7

8.2. Details of Registers....................................................................................................................................................8

8.2.1. Clock counter (SEC - HOUR).........................................................................................................................8

8.2.3. Alarm registers.............................................................................................................................................10

8.2.4. Fixed-cycle timer control registers................................................................................................................10

8.2.5. Extension register ........................................................................................................................................10

8.2.6. Flag register.................................................................................................................................................11

8.2.7. Control register.............................................................................................................................................13

8.3. Fixed-cycle Timer Interrupt Function .......................................................................................................................15

8.3.1. Diagram of fixed-cycle timer interrupt function.............................................................................................15

8.3.2. Related registers for function of fixed-cycle timer interruption......................................................................16

8.3.3. Timer register...............................................................................................................................................16

8.3.4. Fixed-cycle timer interrupt interval (example)...............................................................................................18

8.3.5. Fixed-cycle timer start timing........................................................................................................................18

8.4. EVIN Interrupt and Time stamp Function.................................................................................................................19

8.4.1. Diagram of EVIN interrupt function...............................................................................................................19

8.4.2. Operation example of Time-Stamp function.................................................................................................20

8.4.3. Related registers for EVIN Interrupt and Time stamp Function....................................................................20

8.5. SOUT Interrupt Function..........................................................................................................................................23

8.5.1. Operation example of SOUT function. .........................................................................................................23

8.5.2. Related registers for SOUT interrupt functions.............................................................................................24

8.6. Time Update Interrupt Function...............................................................................................................................25

8.6.1. Time update interrupt function diagram........................................................................................................25

8.6.2. Related registers for time update interrupt functions....................................................................................26

8.7. Alarm Interrupt Function..........................................................................................................................................27

8.7.1. Diagram of alarm interrupt function..............................................................................................................27

8.7.2. Related registers for Alarm interrupt function...............................................................................................28

8.7.3. Examples of alarm settings..........................................................................................................................29

8.8. About the interrupt function for operation /INT = “L”interrupt output.......................................................................30

8.9. Temperature compensation function. ......................................................................................................................30

8.9.1. Temperature compensation function............................................................................................................30

8.9.2. Related registers for temperature compensation function............................................................................30

8.10. Reading/Writing Data via the I2C Bus Interface.....................................................................................................31

8.10.1. Overview of I2C-BUS.................................................................................................................................31

8.10.2. System configuration..................................................................................................................................31

8.10.3. Starting and stopping I2C bus communications..........................................................................................32

8.10.4. Data transfers and acknowledge responses during I2C-BUS communications..........................................33

8.10.5. Slave address ............................................................................................................................................33

8.10.6. I2C bus protocol..........................................................................................................................................34

8.11. Backup and Recovery............................................................................................................................................35

8.12. About access at the time of backup return and Initial power supply ......................................................................36

8.13. Flow chart..............................................................................................................................................................37

8.14. Connection with Typical Microcontroller ................................................................................................................40

8.15. When used as a clock source (32 kHz-TCXO) ......................................................................................................40

9. External Dimensions/Marking Layout...................................................................................................... 41

9.1. RX8804CE..............................................................................................................................................................41

9.1.1. External dimensions.....................................................................................................................................41

9.1.2. Marking layout..............................................................................................................................................41

10. Application notes..................................................................................................................................... 42