ESO STRAP User manual

EUROPEAN SOUTHERN OBSERVATORY

Organisation Européenne pour des Recherches Astronomiques dans l'Hémisphère Austral

Europäische Organisation für astronomische Forschung in der südlichen Hemisphäre

VERY LARGE TELESCOPE

STRAP

Electronics Hardware Manual

Doc. No.:VLT-MAN-ESO-11670-1794

Issue: 1.0

Date: June 30, 2000

Prepared: R.Biasi, S.Moureau 30.05.00

.............................................................

Name Date Signature

Approved: D.Bonaccini,

R.Donaldson 29.06.00

.............................................................

Name Date Signature

Released: G.Monnet 04.07.00

.............................................................

Name Date Signature

VLT PROGRAMME * TELEPHONE: (089) 3 20 06-0 * FAX: (089) 3 20 23 62

STRAP

Electronics Hardware Manual

Doc:

Issue

Date

Page

VLT-MAN-ESO-11670-1794

Issue 0.3.6

5 June, 2000

2of 96

CHANGE RECORD

Issue Date Section/Page affected Reason/ Initiation/Remarks/ Changes Details

1.0 30.06’00 All First issue

STRAP

Electronics Hardware Manual

Doc:

Issue

Date

Page

VLT-MAN-ESO-11670-1794

Issue 0.3.6

5 June, 2000

3of 96

1. TABLE OF CONTENTS

1. TABLE OF CONTENTS.........................................................................................................................................3

2. DOCUMENTS AND ACRONYMS........................................................................................................................6

2.1 PURPOSE..............................................................................................................................................................6

2.2 APPLICABLE DOCUMENTS....................................................................................................................................6

2.3 APPLICABLE DRAWINGS.......................................................................................................................................7

2.4 LIST OF ACRONYMS.............................................................................................................................................7

3. OVERALL DESCRIPTION....................................................................................................................................8

3.1 GENERAL DESCRIPTION .......................................................................................................................................8

3.2 SENSOR UNIT.......................................................................................................................................................9

3.3 VMESTRAP UNIT............................................................................................................................................10

3.4 SUMMARY LIST OF STRAP FUNCTIONS AND CAPABILITIES................................................................................10

4. FUNCTIONAL UNITS..........................................................................................................................................12

4.1 STRAP SENSOR UNIT FUNCTIONALITY.............................................................................................................12

4.1.1 Sensor Unit functional blocks...................................................................................................................12

4.1.2 Current pulses signal conditioning (Active Quenching)...........................................................................12

4.1.3 Gating function.........................................................................................................................................13

4.1.4 Overcurrent protection.............................................................................................................................13

4.1.5 Permanent memory...................................................................................................................................14

4.1.6 Input-output interface...............................................................................................................................14

4.1.7 Diaphragm micro-motor controller..........................................................................................................14

4.1.8 Cooling circuit requirement......................................................................................................................16

4.1.9 Nitrogen gas flushing................................................................................................................................16

4.2 VMESTRAP CONTROL UNIT FUNCTIONALITY .................................................................................................17

4.2.1 VMESTRAP control unit functional blocks...............................................................................................17

4.2.2 Logic control unit .....................................................................................................................................17

4.2.3 High voltage unit ......................................................................................................................................21

4.2.4 Temperature control.................................................................................................................................22

4.2.5 Computational unit - DSP ........................................................................................................................23

4.2.6 Mirror outputs ..........................................................................................................................................23

4.2.7 Communication interfaces........................................................................................................................23

5. STRAP HARDWARE DESCRIPTION ...............................................................................................................25

5.1 STRAP SENSOR HEAD HARDWARE DESCRIPTION..............................................................................................25

5.1.1 Carrier board............................................................................................................................................26

5.1.2 AQC circuits board...................................................................................................................................26

5.1.3 Connection board .....................................................................................................................................26

5.2 VMESTRAP HARDWARE DESCRIPTION............................................................................................................26

5.2.1 DSP board ................................................................................................................................................27

5.2.2 High voltage and Thermal control board.................................................................................................27

5.2.3 Bridge boards assembly............................................................................................................................31

6. CONNECTIONS ....................................................................................................................................................32

6.1 STRAP SENSOR HEAD CONNECTIONS ...............................................................................................................32

6.2 VME STRAP CONTROL UNIT CONNECTIONS.....................................................................................................34

6.2.1 Front mounting option..............................................................................................................................36

6.2.2 Rear mounting option...............................................................................................................................39

6.2.3 Input/output signals specification............................................................................................................40

6.3 CABLES AND PIPING...........................................................................................................................................41

6.3.1 Cables from Sensor Housing to STRAP VME board................................................................................41

STRAP

Electronics Hardware Manual

Doc:

Issue

Date

Page

VLT-MAN-ESO-11670-1794

Issue 0.3.6

5 June, 2000

4of 96

6.3.2 Cable from Sensor Housing to MAC4 VME board...................................................................................41

6.3.3 Piping of coolant and N2..........................................................................................................................41

6.3.4 Input/output timing specification..............................................................................................................42

7. HARDWARE CONFIGURATION......................................................................................................................43

7.1 VME/SERIAL SELECTION ...................................................................................................................................43

7.2 VME SETTING ...................................................................................................................................................43

7.2.1 Interrupt vector configuration ..................................................................................................................44

7.2.2 Interrupt level configuration.....................................................................................................................44

7.2.3 VME base address configuration..............................................................................................................45

7.3 SERIAL INTERFACE SETTING ..............................................................................................................................45

7.4 MIRROR ANALOG OUTPUT RANGE CONFIGURATION ...........................................................................................45

7.5 DIP-SWITCHES CONFIGURATION EXAMPLE.........................................................................................................46

7.6 DIAPHRAGM MOTOR CONTROLLER SETTINGS ...................................................................................................46

8. TROUBLESHOOTING.........................................................................................................................................48

8.1 VME COMMUNICATION PROBLEMS ...................................................................................................................48

8.1.1 Serial communication problems ...............................................................................................................48

8.2 APDS’BIAS VOLTAGES......................................................................................................................................49

8.3 ANALOG MIRROR OUTPUTS ...............................................................................................................................49

8.4 COUNTERS’INPUTS............................................................................................................................................49

8.5 GATE FUNCTION ................................................................................................................................................50

8.6 THERMAL CONTROL...........................................................................................................................................50

9. MAINTENANCE....................................................................................................................................................51

9.1 REPLACEMENT OF THE QUAD-CELL SENSOR ON THE APD HEAD ASSEMBLY......................................................51

9.2 REPLACEMENT OF THE BOARDS ON THE APD HEAD ASSEMBLY ........................................................................51

9.3 REPLACEMENT OF THE BOARDS ON THE APD-DSP UNIT ...................................................................................53

9.3.1 Replacement of the Bridge boards assembly - front panel option............................................................53

9.3.2 Replacement of the Bridge boards assembly - rear panel option.............................................................54

9.3.3 Replacement of the DSP control board ....................................................................................................55

9.3.4 Replacement of the High Voltage and Thermal control board.................................................................55

10. TECHNICAL SPECIFICATIONS...................................................................................................................56

11. ELECTRICAL CIRCUIT DIAGRAMS ..........................................................................................................58

11.1 STRAP SENSOR UNIT CIRCUIT DIAGRAMS.........................................................................................................58

11.1.1 STRAP Sensor unit electronics part list....................................................................................................64

11.2 VMESTRAP BOARD CONTROL UNITCIRCUIT DIAGRAMS...................................................................................66

11.2.1 VMESTRAP board control unit electronics part list ................................................................................75

11.3 VMESTRAP CONTROL UNIT -BRIDGE...........................................................................................................78

11.3.1 VMESTRAP - Front Bridge circuit diagrams...........................................................................................78

11.3.2 VMESTRAP - Front Bridge - Electronics part list ...................................................................................83

11.3.3 VMESTRAP - Rear Bridge circuit diagrams............................................................................................84

11.3.4 VMESTRAP - Rear Bridge - Electronics part list.....................................................................................89

11.4 VMESTRAP -THERMAL CONTROL AND HIGH VOLTAGE CIRCUIT DIAGRAMS ......................................90

11.4.1 VMESTRAP - THERMAL CONTROL and HIGH VOLTAGE Electronics part list .................................95

STRAP

Electronics Hardware Manual

Doc:

Issue

Date

Page

VLT-MAN-ESO-11670-1794

Issue 0.3.6

5 June, 2000

5of 96

List of figure

FIGURE 1: STRAP ARCHITECTURE AND CONNECTIONS...........................................................................................................8

FIGURE 2: QUAD-CELL SENSOR GEOMETRY .........................................................................................................................9

FIGURE 3: STRAP SENSOR HEAD FUNCTIONAL BLOCKS ...................................................................................................12

FIGURE 4: STRAP DIAPHRAGM -MICRO-MOTOR AND ENCODER INTERNAL WIRING..........................................................16

FIGURE 5: VME STRAP CONTROL UNIT BLOCK SCHEME ..................................................................................................17

FIGURE 6: CONTROL TICK GENERATION LOGIC ..................................................................................................................18

FIGURE 7: PULSE COUNTERS LOGIC ...................................................................................................................................19

FIGURE 8: GATE SIGNAL TIMING........................................................................................................................................21

FIGURE 9: HIGH VOLTAGE UNIT BLOCK SCHEME................................................................................................................22

FIGURE 10: THERMAL CONTROL BLOCK SCHEME...............................................................................................................22

FIGURE 11 -STRAP SENSOR HEAD PHYSICAL LAYOUT .....................................................................................................25

FIGURE 12 -VME STRAP CONTROL UNIT PHYSICAL LAYOUT ..........................................................................................28

FIGURE 13 -STRAP DSP CONTROL BOARD ........................................................................................................................29

FIGURE 14: STRAP SENSOR HEAD REAR VIEW (CONNECTORS'SIDE).................................................................................32

FIGURE 15 :STRAP HEAD HOUSING ..................................................................................................................................34

FIGURE 16 :VME STRAP CONTROL UNIT CONNECTORS -FRONT PANEL OPTION...............................................................36

FIGURE 17 :VME STRAP CONTROL UNIT CONNECTORS -REAR PANEL OPTION.................................................................39

FIGURE 18 :DIGITAL MIRROR OUTPUT LATCH TIMING........................................................................................................42

FIGURE 19 :EXTERNAL SYNC SIGNAL TIMING ....................................................................................................................42

FIGURE 20 :DIAPHRAGM SERVO-DRIVE FUNCTION CABLE..................................................................................................47

FIGURE 21 -APD HEAD BOARDS ASSEMBLY.....................................................................................................................52

FIGURE 22 -VME STRAP CASE AND BOARDS ASSEMBLY -FRONT PANEL OPTION............................................................53

FIGURE 23 -VME STRAP CASE AND BOARDS ASSEMBLY -REAR PANEL OPTION..............................................................54

List of tables

TABLE 1-STRAP SENSOR HEAD CONNECTORS'PINOUT ...................................................................................................33

TABLE 2-VME STRAP CONTROL UNIT CONNECTORS (ALWAYS ON FRONT PANEL).........................................................35

TABLE 3-VME STRAP CONTROL UNIT CONNECTORS (FRONT OR REAR PANEL OPTION)..................................................38

TABLE 4-VMESTRAP CONTROL UNIT INPUT/OUTPUT FUNCTIONAL AND ELECTRICAL SPECIFICATIONS..........................40

TABLE 5-EXTERNAL SYNC SIGNAL TIMING SPECIFICATIONS.............................................................................................42

TABLE 6-VME STRAP HARDWARE CONFIGURATIONS ...................................................................................................43

TABLE 7-VME SETTING ON DIP-SWITCHES S2, S3 ...........................................................................................................43

TABLE 8-INTERRUPT VECTOR ASSIGNMENT .....................................................................................................................44

TABLE 9-INTERRUPT LEVEL ASSIGNMENT........................................................................................................................44

TABLE 10 -VME BASE ADDRESS ASSIGNMENT..................................................................................................................45

TABLE 11 -SERIAL COMMUNICATION SPEED SETTING .......................................................................................................45

TABLE 12 -MIRROR ANALOG OUTPUT RANGE SETTING .....................................................................................................45

TABLE 13 -DIP SWITCHES CONFIGURATION EXAMPLE.......................................................................................................46

TABLE 14 -DIAPHRAGM MOTOR SPEED LOOP SETTING ......................................................................................................46

TABLE 15 -DIAPHRAGM MOTION LOOP PARAMETER .........................................................................................................47

STRAP

Electronics Hardware Manual

Doc:

Issue

Date

Page

VLT-MAN-ESO-11670-1794

Issue 0.3.6

5 June, 2000

6of 96

2. Documents and Acronyms

2.1 Purpose

This document provides all the necessary information for the implementation and the operation of

the STRAP unit in a ESO VLT system.

This manual contains six major sections:

•Overall description

•Description of the functional units

•Description of the physical layout of the hardware

•Connections and System configuration

•Maintenance and troubleshooting

•Technical specifications and Schematics

2.2 Applicable documents

The following documents of the exact issue shown form part of this manual to the extent specified

herein. In the event of a conflict between the documents referenced herein and the contents of this

specification, the contents of this specification shall be considered as superseding requirements.

AD1 STRAP SW Driver User Manual, .: VLT-MAN-ESO-11670-1871, Issue 1.0, 16.12.1999

AD2 STRAP Interface Control Document, VLT-ICD-ESO-11670-0699, Issue 3.0, 20.04.00

AD3 APD overcurrent protection circuit design and test report, VLT-AOP-MGA-001

AD4 STRAP SW User Manual, VLT-MAN-ESO-11670-1870, Issue 2.0, 15.05.00

AD5 4 Channel DC servo-amplifier ESO-VME4SA-X1,VLT-MAN-ESO-17130-0273

AD6 ESO VME4SA Back plane, technical manual, VLT-MAN-ESO-17130-0274

AD7 MAC4-INC User and Software reference manuals (Version 4.2)

AD8 VLT Software CCS-LCU Configuration of VLT standard VME Boards,

VLT-MAN-ESO-17210-1358

AD9 STRAP Interface Control Document, VLT-ICD-ESO-11670-0699, Issue 3.0, 20.04.00

AD10 Electromagnetic compatibility and power quality specification Part 1: electromagnetic

environment of the VLT observatory and EMC levels of the power system;

VLT-SPE-ESO-10000-0002, issue 2, 11.03.92

STRAP

Electronics Hardware Manual

Doc:

Issue

Date

Page

VLT-MAN-ESO-11670-1794

Issue 0.3.6

5 June, 2000

7of 96

AD11 Electromagnetic compatibility and power quality specification Part 2: electromagnetic

disturbance emission and immunity limits of electric and electronic equipment;

VLT-SPE-ESO-10000-0003, issue 1, 05.02.92

AD12 STRAP Optomechanics HW manual

2.3 Applicable drawings

DWG 1 Adaptive Optics APD Quad-head sensor; mechanical assembly,

VLT-DWG-ESO-11670-0780-0000-1/2, rev. A 13.11.97

DWG 2 Adaptive Optics APD Quad-head sensor; interface drawing

VLT-DWG-ESO-11670-0780-0000-2/2

2.4 List of Acronyms

APD Avalanche Photo-Diodes

AQC Active Quenching Circuit

AT Auxiliary Telescope unit

DSP Digital Signal Processor

DWGxx Applicable Drawing # xx

EMC Electromagnetic Compatibility

ESO European Southern Observatory

FWHM Full Width at Half Maximum

HW Hardware

LCU Local Control Unit

M2 VLT secondary mirror unit

NGS Natural Guide Star, reference star for the tip-tilt servo-control

STRAP System for Tip-tilt Removal with Avalanche Photodiodes

SW Software

TCS Telescope Control System

UT Unit Telescope, VLT 8m telescope

VISA Very Large Telescope Interferometer Sub-Array

VLT Very Large Telescope

VLTI Very Large Telescope Interferometer

STRAP

Electronics Hardware Manual

Doc:

Issue

Date

Page

VLT-MAN-ESO-11670-1794

Issue 0.3.6

5 June, 2000

8of 96

3. Overall description

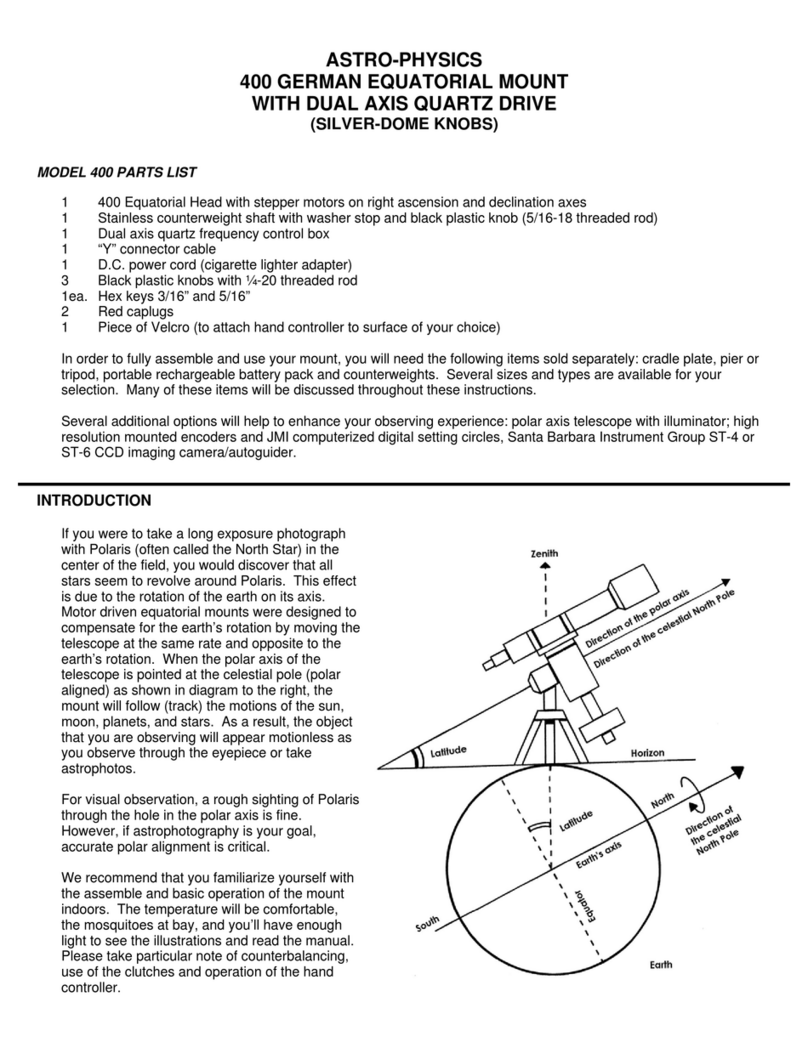

3.1 General description

The STRAP units are implemented into VLT instruments or VLT-sub-system (e.g: VLT and VLTI adaptive optics in

the Uts and Ats) for field stabilization, to remove the atmospheric and environmentally induced tilts.

STRAP is a self-contained system, which comes with its hardware and software interfaces, user,

operation and maintenance manuals. STRAP encompasses a photon-counting visible sensor, the

housekeeping and the loop control hardware/software. The input is a signal from a Natural Guide

Star (NGS) focussed on the sensor unit, the output is a command signal, optionally analog or

digital, which can drive most of the commercial steering mirrors drivers.

TCS

Fast

Steering Mirror

+ HV amplifiers

M2 Fast

Guiding

M

2

L

A

N

T

I

M

Tip-Tilt Loop

LAN

f/36 or slower beam

All cables to Sensor Head 15m max

optional LAN M2 control

Diaphragm

analog/

digital

HW Reset

STRAP Sensor Head

V

M

E

S

T

R

A

P

V

M

E

L

C

U

HP

Workstation

M

A

C

4

/

I

N

C

V

M

E

4

S

A

filte

r

coolant

Diaphragm Control

External gating

External Clock

Figure 1: STRAP architecture and connections. The control of UT M2 (AT M6) via a dedicated LAN is optional. The

TIM board is optional. Only one channel of a MAC4 motor controller board is used for the STRAP field diaphragm.

External gating, clocking and hardware reset of VMESTRAP are possible. Mirror commands output can be analog or

digital.

STRAP as delivered consists of two separate units (Figure 1), with all interconnecting cables:

•the photon counting Sensor Unit

STRAP

Electronics Hardware Manual

Doc:

Issue

Date

Page

VLT-MAN-ESO-11670-1794

Issue 0.3.6

5 June, 2000

9of 96

•the VMESTRAP control board unit

The Sensor unit interacts with the VMESTRAP control board unit and one of the four channel of

a MAC4/INC-VME4SA for the control of the motorisd diaphragm .

The VMESTRAP board control unit interacts only with the CPU board of a LCU via the VME bus,

or via a serial link to a servicing PC.

The X,Y output commands of the VMESTRAP board to the mirror drivers are available as analog

signals and as digital formats.. It is also possible to drive the UT-M2 in fast guiding mode.

The VMESTRAP control board unit is inserted in a VME 19’–6HE rack with a CPU, a LAN

connection, an optional extra LAN connection to M2, a MAC4/INC motor controller , a VME4SA

DC motor servo-amplifier and an HP Workstation as console. Some or all of these boards may be

shared with an AO system such as MACAO, or with an associated instrument.

Note: The CPU board, the motion controller board, the DC servo-amplifier board and all necessary

power supply units, and associated cables are NOT part of STRAP delivery.

3.2 Sensor Unit

The sensor unit contains the integrated APD quad-cell mounted on a Peltier thermo-cooler, a cold

finger to off-load the heat, the integrated electronics for the active quenching/pulse generation and

for the APD protection. All the electronics are embedded in a dry Nitrogen atmosphere.

In the integrated APD quad-cell, the image of the guide star is focussed on a 2x2 lenslet array

crossing (Figure 2). Each lenslet makes an image of the pupil on the Slik APD sensor at its focal

plane.

TM

Figure 2: Quad-cell sensor geometry

When the guide star is moving on the lenslet crossing, the illumination of the four pupils changes

but not their position on the APDs. The balancing of the four APD signals is the aim of the servo-

control. The APD response across its sensitive area is uniform.

The sensor head electronics transforms each photon detected into a pulse (RS485 level). The four

TTL signals of the quad-cell are transmitted to the VMESTRAP board. A motorised variable

aperture diaphragm is present to limit the sky background if necessary. The micro-motor and the

encoders are controlled by one channel of the MAC4/INC and VME4SA boards.

STRAP

Electronics Hardware Manual

Doc:

Issue

Date

Page

VLT-MAN-ESO-11670-1794

Issue 0.3.6

5 June, 2000

10 of 96

3.3 VMESTRAP Unit

The DSP-based VMESTRAP control board is plugged into a VME rack at a distance not greater

than 20 meters (Maximum). The VMESTRAP unit controls the tip-tilt loop in real time, and

performs all the necessary housekeeping and data gathering for the diagnostics. The VMESTRAP

control unit dialogues with the CPU board of the same sub-rack through the VME bus (P1 only).

For diagnostic and setup purposes, the VMESTRAP control unit is also equipped with a RS232

serial output port which gives a similar access to the same servicing and diagnostic functions. ,The

VMESTRAP feedback commands to the steering mirror is performed via three possible ways:

through the VME bus , directly with two analog output signals or via two equivalent digital output

signals. The former is used to drive directly the UT M2 (AT M6) steering mirror via a dedicated

Ethernet LAN.

3.4 Summary list of STRAP functions and capabilities

Sensor unit:

•(1 inch) quad-cell integrated APD device - without optical fiber.

•APD breakdown voltages and dark counts stored on an E2PROM, together with the APD chip

in the sensor head unit.

•Electronic safety circuits to protect the APD from sustained overcounts or electronics failures.

•Temperature control of the APD dark counts, below 25cts/s at low flux regimes.

•Use “average” Slik diodes with 250 dark counts/sec, not specifically selected for low dark.

Motorised variable diaphragm to minimize the sky contribution at low NGS fluxes.

•No temperature gradients generated in the sensor area.

•Pressurised housing with dry nitrogen atmosphere, to avoid condensation on the High Voltage

electronic circuits.

VMESTRAP unit

•Real time control tip-tilt loop on custom DSP VMESTRAP board, connected with the APD

sensor unit

•Fourth order optimized digital filtering, for the tip and tilt channels.

•APD temperature loop. T can be set between 0 and -40°C to optimize the dark counts.

•After pulsing control via hold-off time selection.

•SW driver to interface to the VME Motorola PowerPC running VxWorks.

•Optional full PC control via RS232 serial link directly on the VMESTRAP board.

•Fast steering mirror output in analog and digital format, 6 programmable voltage ranges.

•Real time centroids and mirror command data streamed on the VME bus or the serial link.

•Real time APD counts data streamed on the VME bus or the serial link.

•Optional internal or external clocking.

•SW reset and HW external reset.

•SW/electronic gating of APDs at 10nsec response time.

STRAP

Electronics Hardware Manual

Doc:

Issue

Date

Page

VLT-MAN-ESO-11670-1794

Issue 0.3.6

5 June, 2000

11 of 96

•HW external gating for APD safety interlock.

•Automatic roll-off gating to avoid APD saturation yet using the full dynamic range.

•Full VMESTRAP board programming and status monitored.

•Circular or linear data buffers to store loop data and pass them to the control computer.

•Injection of pre-stored disturbance signals in the loop for performance tests/maintenance.

•Diagnostics with mean and variances of sensor flux, tilt residual and mirror command data.

LCU SW supported functions

•Automatic sequence of operation for the initial setting of the APDs, star centering and photon

flux conditioning.

•Automatic adaptive setting of loop and APD set-up parameters.

•Automatic Gain Control.

•Chopping mode with external synch timing.

•Option to drive VLT-M2 in fast guide mode, through a LAN board.

•Cloud check monitoring flux, automatic freeze of steering mirror if flux below threshold.

STRAP

Electronics Hardware Manual

Doc:

Issue

Date

Page

VLT-MAN-ESO-11670-1794

Issue 0.3.6

5 June, 2000

12 of 96

4. Functional units

4.1 STRAP Sensor Unit Functionality

4.1.1 Sensor Unit functional blocks

Four functional blocks can be distinguished in the APD sensor unit:

•APD quad cell and permanent data memory (4.1.5)

•Active Quenching circuit (0)

•Over-current protection circuit (4.1.4)

•Input/Output interface (4.1.6)

HV

APD

CURRENT

SENSE HV

ON/OFF

CIRCUIT

ACTIVE

QUENCHING

CIRCUIT

OVERCURRENT

LOGIC AND

INPUT/OUTPUT

INTERFACE

OVERCURRENT

PROTECTION

Figure 3: STRAP Sensor Head functional blocks

4.1.2 Current pulses signal conditioning (Active Quenching)

The APDs are operated in Geiger mode. They are polarized inversely by a bias voltage usually

about 18V higher than the breakdown voltage, and the avalanche is triggered by the energy of the

photon trapped by the device. The current rise due to the avalanche phenomenon is sensed by the

Active Quenching Integrated Circuit (AQC IC developed by the team of Professor Cova at

Politecnico di Milano).

After this initial trigger, the circuits initiates a sequence of actions, namely:

•quenching phase - the APD polarization voltage is within a few nanoseconds reduced below

the breakdown voltage, so that the avalanche is stopped. Meanwhile a TTL pulse is

generated by a single shot output circuitry. This pulse is then transferred to the counting

circuitry of VME STRAP control unit (4.2.2.3)

STRAP

Electronics Hardware Manual

Doc:

Issue

Date

Page

VLT-MAN-ESO-11670-1794

Issue 0.3.6

5 June, 2000

13 of 96

•reset phase - after a short time (about 70 ns), depending on the characteristics of the actual

device, the original bias voltage is restored and the device is ready for the next photon

detection.

The length of the quenching+reset phases (currently about 100 ns) determines the maximum

allowable counting frequency (about 1/100 ns = 10 Mcnt/s).

4.1.3 Gating function

The AQC IC provides also the gating function, i.e. the capability of disabling the counting on the

APDs by reducing the bias voltage below the breakdown threshold. This is obtained by holding the

circuit in the quenching state (0).

The gating function is enabled by activating a dedicated TTL input on the AQC IC ( ).

Table 1

The gating capability is provided in order to allow the safe operation of the circuit even at very high

photon fluxes: counting is enabled and disabled continuously by a PWM signal with an accurate

timing generated by the VME STRAP control unit. This allows a reduction of the thermal power

dissipated by the APD quad cell.

The gating function can be also operate as ultra-fast electronic shutter, in order to stop the counting

during the transmission phase of pulsed LGS lasers, or as an interlock to protect the diodes from

excess light.

4.1.4 Overcurrent protection

Very fast D-MOS electronic switches are part of the Active Quenching Circuitry. These devices are

sensitive to electrostatic charges and do not withstand high polarization voltages. These conditions

may occur due to mishandling, wrong power-on or power-off sequences.

Electrostatic discharges could damage the AQC integrated circuit and the Slik APD.

Futhermore, if the reset D-MOS (11.1) remains active for longer time, as it may happen if either the

device itself or the AQC IC is damaged, the APD will immediately turn into a continuos breakdown

status. Neither the active nor the passive quenching can be effective in this condition, and the APD

will be destroyed in few tenths of a second.

In order to protect the APDs from this potentially dangerous condition, an overcurrent protection

has been implemented for STRAP.

The protection circuit senses the mean current flowing through every single APD on the quad cell

and if the current rises beyond a threshold, shuts off quickly the APD polarization voltage. Since

during ‘sustained’ breakdown, the current flow is expected to be the similar to the peak current

flowing during every breakdown pulse at normal operation, the sensed current is low-pass filtered

before being compared to the threshold value. The time constant of the filter and the threshold value

are defined in order to meet the safe operation requirements (fast response to overcurrents) and to

avoid unexpected insertions during normal operation.

When an overcurrent condition is detected, the following actions are taken automatically:

•the APDs are disconnected by hardware from the bias voltage (all four

simultaneously, regardless to the APD where the overcurrent occurred)

•a signal is sent to the VMESTRAP control unit

STRAP

Electronics Hardware Manual

Doc:

Issue

Date

Page

VLT-MAN-ESO-11670-1794

Issue 0.3.6

5 June, 2000

14 of 96

•the VMESTRAP DSP software detects the fault condition and sends a signal to the

CPU (AD1)

•the VMESTRAP DSP shuts down the bias voltage on all four APDs

•a fault flag appears on the STRAP user interface (AD4)

The system can not recover by itself from the overcurrent shutdown. The normal operating

condition can be only restored by a user command.

4.1.5 Permanent memory

Each of the following APDs' characteristics are stored in a small permanent memory (serial I C

EPROM) mounted on the PCB hosting the quad-cell sensor:

2

2

•the breakdown voltage and its temperature coefficient

•the darkcounts and the temperature coefficient

•the quantum efficiency

The reading of these data is performed automatically by the VME STRAP control unit before the

start of the voltage setting procedure, in order to avoid wrong operation by the user.

The writing of the new data into the permanent memory can be performed only from the

engineering panel , but only with restricted access (Password protected). Inserting wrong

parameters may result in the destruction of the APDs.

4.1.6 Input-output interface

The input/output interface are designed in order to keep the signal integrity over relatively long

transmission lines (up to 20 m). In particular, the four count pulse outputs and the gating signal

input have high speed requirements. These signals and the three data transmission lines required by

the permanent memory (4.1.5) are converted from TTL level to RS485 level and transferred over

twisted cable pairs. This choice reduces crosstalk and increases noise immunity.

All digital signals that are not time critical (high voltage enable input and overcurrent flag

output) are transferred through single ended TTL lines, using buffers and Schmitt trigger inputs.

4.1.7 Diaphragm micro-motor controller

The motorized variable aperture field diaphragm is located in the unit, before the quad-cell sensor.

The opening of the diaphragm is adjusted via software to minimize the sky background effects on

the servo-loop. This is especially relevant with faint NGS. The micro-motor, the encoder and limit-

switches are all inside the housing.

The motorised diaphragm unit is made of the following electrical components and is compliant with

the ESO defined standard motion system and convention [5], [6] and [7]

•Incremental encoder:

-Mounted directly on the motor shaft

-32 pulses/360 deg

-5Vdc supply

STRAP

Electronics Hardware Manual

Doc:

Issue

Date

Page

VLT-MAN-ESO-11670-1794

Issue 0.3.6

5 June, 2000

15 of 96

-Two phases differential signal

•DC micro-motor:

-24 Vdc - 3 W

-max. speed 16000 rpm

•Upper and lower limit switch:

-5 Vdc - NC – Current limited to 10mA

This diaphragm unit is interfaced via one of the channel of a MAC-INC / VME4SA motion control

VME boards. The maximum supply voltages for the motor is +24Vdc and –24Vdc (connection to

be made at the VME4SA back plane.The STRAP encoder circuits requires 5 Vdc ±5%.

The speed loop PID parameters and the tacho gain are programmed with discret components

(resistors and capacitance) mounted on a socket on the VME4SA board. The 0n-board components

provided (factory setting) are suitable for the diaphragm servo-drive unit.

Note: As no physical tachometer can be mounted on the motor, a feed-back resistance of 200

KOhms is placed inside the function cable connector (Molex), provided with the Strap, between the

motor output channel (E8) and the tachometer input circuit (E3)

The running parameters are (Approximate value):

-Travel range: 90 °deg.

-Operating time: 8 seconds

-Number of counts: approx.: 55000 cts (with 4x interpolation)

-Running motor voltage: 12.4 Vdc

-Running motor current: 25 mA

-Tacho signal: 6.2 Vdc

STRAP

Electronics Hardware Manual

Doc:

Issue

Date

Page

VLT-MAN-ESO-11670-1794

Issue 0.3.6

5 June, 2000

16 of 96

STRAP - S/D Interface - CS-P-1920 (REV.1)

5VCC

5VCC

5VCC

M

+

Vcc

Motor-

M-

NEG LS NEG

_

LIMIT

POS

_

LIMIT

WIRIN

G

CONNECTION

TO LEMO

B-

Motor

+

B

+

A-

A

+

PHASE A

PHASE

B

GN

D

5V-ENC

5V NEG LS

5V POS LS

POS LS

0V

12

910

J2

=

COMPONEN

T

VIE

W

MAXO

N

MOTOR

RE013

GP013

INC.

PULSE

NE

: 24V-3W - TYPE

-035-13EAB101A

GEAR : 1118.75:1

A032- TYPE 1119E1A00A

ENC : 5V-32

S/TURN - TYPE 3420

G

_

LIMIT

S

_

LIMIT

R1 390 - 1/8W

C1

4.7uF

R2 390 - 1/8W

U1B

56

7

U1A

SN75158

32

1

D1

SMBJ5.0

J2

1

2

3

4

5

6

7

8

9

10

U2 ITA6V5B3

GND 1

I/O8 2

I/O7 3

I/O6 4

I/O5 5

I/O4 6

I/O3 7

I/O2 8

I/O1 9

GND 10

GND

11

I/O1

12

I/O2

13

I/O3

14

I/O4

15

I/O5

16

I/O6

17

I/O7

18

I/O8

19

GND

20

J1

1

2

3

4

5

6

7

8

9

10

M

-

+

ENC

+

-

PH-A

PH-B

MICRO-SWITC

H

Matsushit

a

AV444461

PO

Figure 4: STRAP diaphragm - Micro-motor and encoder internal wiring

4.1.8 Cooling circuit requirement

The heat generated by the APD quad-cell double Peltier thermocooler is removed by a supply of coolant

from the VLT cooling system. This coolant is assumed to have the following characteristics:

-Cooling liquid: 33% ethylene glycol solution

-Minimum flow rate: 5ml/sec

-Maximum recommended flow rate: 10 ml/sec

-Coolant supply temperature: 5 ºC, or 3 ºC above the dew point

-Pressure difference at interface point: 0.4 bar

-Design operating pressure: 4 bar

-Two coolant pipes connectors: type CPC 1/4" sectional area of flow

-Quick couplings: male = inlet /female = outlet

-Coolant pipes diameter: inner: 5.5mm / outer: 10 mm

4.1.9 Nitrogen gas flushing

Two nitrogen gas flushing valves are sealed and used only during maintenance.

STRAP

Electronics Hardware Manual

Doc:

Issue

Date

Page

VLT-MAN-ESO-11670-1794

Issue 0.3.6

5 June, 2000

17 of 96

4.2 VMESTRAP Control Unit Functionality

4.2.1 VMESTRAP control unit functional blocks

Six functional blocks can be distinguished in the VME STRAP control unit (see also 4.2):

•Logic unit (4.2.1)

•High voltage unit (0)

•Thermal control unit (4.2.4)

•DSP computational unit (4.2.5)

•Mirror outputs (4.2.6)

•Communication interfaces (4.2.7)

DSP

ADC

P.I.D. DAC

ADC

Pulse

counters

& holdoff

Gate

signal

generator

Control

tick

generator

VME

interface

Serial

interface

Thermal control unit

Logic unit

(computational

unit)

Communication

interfaces

VME P1/J1

(A16/D16)

RS232

Digital

output

Thermocooler

APD Thermal

Pulse out (4x)

External sync

Gate out

HV supply

units

DAC DAC

High voltage unit

DSP

Mirror output

Analog

output

APD bias

APD

sensor

APD

External

gate in

Figure 5: VME STRAP control unit block scheme

4.2.2 Logic control unit

The VMESTRAP logic control unit consists of the pulse counters, the control tick generator and

the gating signal generator. As all these functions are very time critical, they are implemented at

STRAP

Electronics Hardware Manual

Doc:

Issue

Date

Page

VLT-MAN-ESO-11670-1794

Issue 0.3.6

5 June, 2000

18 of 96

hardware level by means of a Programmable Logic Devices. Only the setting of the different

parameters and operating modes is done by the DSP software.

4.2.2.1 Control tick signal generator

The tick signal generation logic is clocked by the 40 MHz main system clock. The 2KHz prescaler

output feeds an up-counter with compare-and-reset capabilities: Once the value set in the compare

register is reached, the counter is reset and a control tick is sent to the circuit output.

The compare register is loaded by the DSP under software control (a proper command is available

at LCU level, as described in AD1.

The control period can be set from 1ms to 62ms in 0.5ms steps. Since the tick generation is

performed only at hardware level, the period jitter is below 20 ns, and an accuracy of ± 100ppm is

guaranteed.

40 MHz

System

Clock Prescaler Counter

Compare

register

DSP

command

Tick

interrupt

output

2 KHz

[1..62ms]

Figure 6: Control tick generation logic

4.2.2.2 External synchronization

Alternatively to the internal generation of the control tick, the VME STRAP unit can be

synchronized with an external source. A software command (AD1) is provided for the selection of

the internal or external tick signal. If the external source is selected, all control-related functions

will be triggered by the external signal (integration time, control computations, mirror output

update).

For the electrical and timing specifications of the external synchronization signal, see the

paragraphes 6.2.3 and 6.3.4.2.

4.2.2.3 Pulse counters and readout logic

The counters have been implemented by means of a pipelined synchronous-asynchronous

structure, as shown in the functional scheme below.

STRAP

Electronics Hardware Manual

Doc:

Issue

Date

Page

VLT-MAN-ESO-11670-1794

Issue 0.3.6

5 June, 2000

19 of 96

40 MHz

System

Clock

Input

sychronizer

Pulse input Holdoff logic

DSPcommand

(holdoff

enable/disable)

16 bit counter DSP

DMA port

3 bit

comparator

3 bit counter

3

3

counter

read & reset

logic

Control

interrupt tick

A<>B enable counter

reset counter

16

read & reset

signal

Figure 7: Pulse counters logic

The asynchronous pulse input is received at RS485 level from the APD Head (4.1.6). This signal is

first converted into a TTL signal, then it is synchronized with the system clock. The synchronized

output pulse is passed to the Hold-off logic block (4.2.2.4and feeds the 16-bit counter. In parallel

the pulses are also continuously counted by a 3 bit binary counter. The main binary counter (16 bit)

is enabled only if its lower 3 bit are not equal to the output of the three bit counter and if the 16 bit

output is not currently read by the DSP. According to this conceptual scheme, the 3 bit counter acts

as a buffer that allows that no pulses are missed while the main counter is read (in fact, the main

counter must be stopped during the read and reset phase).

The counter reading is performed through the DMA port of the DSP. The read and reset phase is

initiated by the control interrupt.

The maximum allowable counting frequency is 10 Mcnt/s.

The input count pulses width should be > 60ns to ensure correct pulse detection.

4.2.2.4 Hold-off circuit

When the APDs are operated at low temperature (approximately below -10°C), the avalanche

electron charges tend to be temporarily trapped in silicon crystal defects, and released thermally

when the diode is enabled again. This phenomenon creates the presence of unwanted 'after-pulses'

(up to four pulses) after the photon detection pulses. This has been revealed by extensive tests

performed during the development phase, with a probability <1%.

A tradeoff solution has been taken in order to eliminate this effect at low count rates. The system

can be operated in two different modes:

•at high count rates (>= 18 Kcts/s) the APDs are operated at higher temperatures (> -10°C).

Therefore, the charge trapping disappears. At this count rates, the higher dark count value

exhibited by the APDs due to the higher operating temperature is not sensibly affecting the

signal to noise ratio.

•at low count rates, the dark counts rate becomes more significant for the overall

performance of the system. Therefore, the APDs are operated at low temperature and a

STRAP

Electronics Hardware Manual

Doc:

Issue

Date

Page

VLT-MAN-ESO-11670-1794

Issue 0.3.6

5 June, 2000

20 of 96

digital hold-off circuit is enabled so that after one pulse is gathered, no other pulses are

counted during a period of 800 ns. After this period, the normal operation is restored and a

new pulse can be counted.

It shall be noticed that the hold-off tends to introduce a noise, due to the fact that some 'good' pulses

(and not only 'after-pulses') could be missed during the hold-off period. Considering the Poisson

statistics of the counted events, the probability for a 'good' pulse to happen within 800 ns from

another 'good' pulse can calculated as follow:

!nem

pmn −

⋅

=

014.08.0 63 =⋅ −

em

where mis the mean number of events in the time unit

nis the number of events considered

At 18 Kcts/s: 18=⋅= −etf offhold

therefore:

015.0

!1

014.0 =

⋅

=e014.01 −

p

This value represents the signal to noise reduction due to the insertion of the holdoff circuit. It is

directly comparable with a typical signal to noise ratio due to dark counts (300 cnt/s) operating at

0°C, always at 18 Kcts/s.

4.2.2.5 Gate signal generator

The gate signal is generated by the same logic circuit that provides the reference control tick

signal.

The period of the gate signal is fixed at 0.5 ms, and it is always synchronous with the control

tick interrupt (and therefore with the APDs' integration time). This configuration avoids the

generation of noise by the pulse gating circuit.

The duty cycle can be modified under the control of the DSP in 32 linear steps from 0 to

100%.

Table of contents

Other ESO Telescope manuals

Popular Telescope manuals by other brands

Celestron

Celestron ASTROMASTER EQ instruction manual

ESA

ESA ItsImagical 225X manual

Celestron

Celestron CPC Series instruction manual

Orion

Orion 5567 manual

Vivitar

Vivitar VIV-TEL-76700 instruction manual

ORION TELESCOPES & BINOCULARS

ORION TELESCOPES & BINOCULARS FunScope Astro Dazzle 4.5 instruction manual