Exar XRT86VL38 User manual

Exar Corporation 48720 Kato Road, Fremont CA, 94538 •(510) 668-7000 •FAX (510) 668-7017 •www.exar.com

xr PRELIMINARY XRT86VL38

OCTAL T1/E1/J1 FRAMER/LIU COMBO

MARCH 2005 REV.P1.0.6

GENERAL DESCRIPTION

The XRT86VL38 is an eight-channel 1.544 Mbit/s or

2.048 Mbit/s DS1/E1/J1 framer and LIU integrated

solution featuring R3technology (Relayless,

Reconfigurable, Redundancy). The physical

interface is optimized with internal impedance, and

with the patented pad structure, the XRT86VL38

provides protection from power failures and hot

swapping.

The XRT86VL38 contains an integrated DS1/E1/J1

framer and LIU which provide DS1/E1/J1 framing and

error accumulation in accordance with ANSI/ITU_T

specifications. Each framer has its own framing

synchronizer and transmit-receive slip buffers. The

slip buffers can be independently enabled or disabled

as required and can be configured to frame to the

common DS1/E1/J1 signal formats.

Each Framer block contains its own Transmit and

Receive T1/E1/J1 Framing function. There are 3

Transmit HDLC controllers per channel which

encapsulate contents of the Transmit HDLC buffers

into LAPD Message frames. There are 3 Receive

HDLC controllers per channel which extract the

payload content of Receive LAPD Message frames

from the incoming T1/E1/J1 data stream and write the

contents into the Receive HDLC buffers. Each framer

also contains a Transmit and Overhead Data Input

port, which permits Data Link Terminal Equipment

direct access to the outbound T1/E1/J1 frames.

Likewise, a Receive Overhead output data port

permits Data Link Terminal Equipment direct access

to the Data Link bits of the inbound T1/E1/J1 frames.

The XRT86VL38 fully meets all of the latest T1/E1/J1

specifications: ANSI T1/E1.107-1988, ANSI T1/

E1.403-1995, ANSI T1/E1.231-1993, ANSI T1/

E1.408-1990, AT&T TR 62411 (12-90) TR54016, and

ITU G-703, G.704, G706 and G.733, AT&T Pub.

43801, and ETS 300 011, 300 233, JT G.703, JT

G.704, JT G706, I.431. Extensive test and diagnostic

functions include Loop-backs, Boundary scan,

Pseudo Random bit sequence (PRBS) test pattern

generation, Performance Monitor, Bit Error Rate

(BER) meter, forced error insertion, and LAPD

unchannelized data payload processing according to

ITU-T standard Q.921.

Applications and Features (next page)

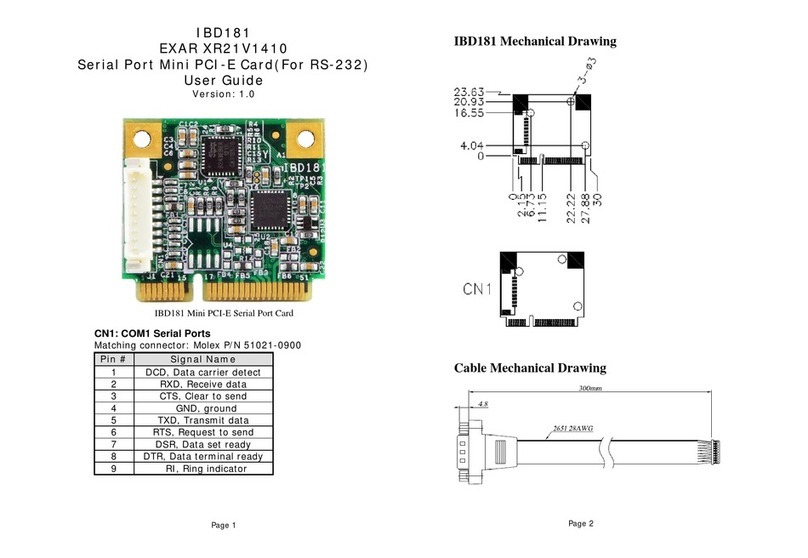

FIGURE 1. XRT86VL38 8-CHANNEL DS1 (T1/E1/J1) FRAMER/LIU COMBO

Performance

Monitor

PRBS

Generator &

Analyser

HDLC/LAPD

Controllers

LIU &

Loopback

Control

DMA

Interface

Signaling &

Alarms JTAG

WR

ALE_AS

RD

RDY_DTACK

µP

Select

A[14:0]D[7:0]

Microprocessor

Interface

4

3

Tx Serial

Clock

Rx Serial

Clock

8kHz sync

OSC

Back Plane

1.544-16.384 Mbit/s

Local PCM

Highway

ST-BUS

2-Frame

Slip Buffer

Elastic Store

Tx Serial

Data In Tx LIU

Interface

2-Frame

Slip Buffer

Elastic Store

Rx LIU

Interface

Rx Framer

Rx Serial

Data Out

RTIP

RRING

TTIP

TRING

External Data

Link Controller

Tx Overhead In Rx Overhead Out

XRT86VL38

1 of 8-channels

Tx Framer

LLB LB

System (Terminal) Side

Line Side

1:1 Turns Ratio

1:2 Turns Ratio

Memory Intel/Motorola µP

Configuration, Control &

Status Monitor

RxLOS

TxON

INT

XRT86VL38 PRELIMINARY xr

OCTAL T1/E1/J1 FRAMER/LIU COMBO REV.P1.0.6

2

APPLICATIONS

•High-Density T1/E1/J1 interfaces for Multiplexers, Switches, LAN Routers and Digital Modems

•SONET/SDH terminal or Add/Drop multiplexers (ADMs)

•T1/E1/J1 add/drop multiplexers (MUX)

•Channel Service Units (CSUs): T1/E1/J1 and Fractional T1/E1/J1

•Digital Access Cross-connect System (DACs)

•Digital Cross-connect Systems (DCS)

•Frame Relay Switches and Access Devices (FRADS)

•ISDN Primary Rate Interfaces (PRA)

•PBXs and PCM channel bank

•T3 channelized access concentrators and M13 MUX

•Wireless base stations

•ATM equipment with integrated DS1 interfaces

•Multichannel DS1 Test Equipment

•T1/E1/J1 Performance Monitoring

•Voice over packet gateways

•Routers

FEATURES

•Eight independent, full duplex DS1 Tx and Rx Framer/LIUs

•Two 512-bit (two-frame) elastic store, PCM frame slip buffers (FIFO) on TX and Rx provide up to 8.192 MHz

asynchronous back plane connections with jitter and wander attenuation

•Supports input PCM and signaling data at 1.544, 2.048, 4.096 and 8.192 Mbits. Also supports 4-channel

multiplexed 12.352/16.384 (HMVIP/H.100) Mbit/s on the back plane bus

•Programmable output clocks for Fractional T1/E1/J1

•Supports Channel Associated Signaling (CAS)

•Supports Common Channel Signalling (CCS)

•Supports ISDN Primary Rate Interface (ISDN PRI) signaling

•Extracts and inserts robbed bit signaling (RBS)

•3 Integrated HDLC controllers per channel for transmit and receive, each controller having two 96-byte

buffers (buffer 0 / buffer 1)

•HDLC Controllers Support SS7

•Timeslot assignable HDLC

•V5.1 or V5.2 Interface

•Automatic Performance Report Generation (PMON Status) can be inserted into the transmit LAPD interface

every 1 second or for a single transmission

•Alarm Indication Signal with Customer Installation signature (AIS-CI)

•Remote Alarm Indication with Customer Installation (RAI-CI)

•Gapped Clock interface mode for Transmit and Receive.

•Intel/Motorola and Power PC interfaces for configuration, control and status monitoring

•Parallel search algorithm for fast frame synchronization

•Wide choice of T1 framing structures: SF/D4, ESF, SLC®96, T1DM and N-Frame (non-signaling)

•Direct access to D and E channels for fast transmission of data link information

xr PRELIMINARY XRT86VL38

REV. P1.0.6 OCTAL T1/E1/J1 FRAMER/LIU COMBO

3

•PRBS, QRSS, and Network Loop Code generation and detection

•Programmable Interrupt output pin

•Supports programmed I/O and DMA modes of Read-Write access

•Each framer block encodes and decodes the T1/E1/J1 Frame serial data

•Detects and forces Red (SAI), Yellow (RAI) and Blue (AIS) Alarms

•Detects OOF, LOF, LOS errors and COFA conditions

•Loopbacks: Local (LLB) and Line remote (LB)

•Facilitates Inverse Multiplexing for ATM

•Performance monitor with one second polling

•Boundary scan (IEEE 1149.1) JTAG test port

•Accepts external 8kHz Sync reference

•1.8V Inner Core Voltage

•3.3V I/O operation with 5V tolerant inputs

•420-pin TBGA package or 484-pin STBGA package with -40°C to +85°Coperation

ORDERING INFORMATION

PART NUMBER PACKAGE OPERATING TEMPERATURE RANGE

XRT86VL38IB 420 Tape Ball Grid Array -40°C to +85°C

XRT86VL38IB484 484 Shrink Thin Ball Grid Array -40°C to +85°C

XRT86VL38 PRELIMINARY xr

OCTAL T1/E1/J1 FRAMER/LIU COMBO REV.P1.0.6

4

420 BALL - TAPE BALL GRID ARRAY (BOTTOM VIEW, SEE PIN LIST FOR DESCRIPTION)

2625242322212019181716151413121110987654321

OOOOOOOOOOOOOOOOOOOOOOOOOOA

OOOOOOOOOOOOOOOOOOOOOOOOOOB

OOOOOOOOOOOOOOOOOOOOOOOOOOC

OOOOOOOOOOOOOOOOOOOOOOOOOOD

OOOOOOOOOOOOOOOOOOOOOOOOOOE

OOOOO OOOOOF

OOOOO OOOOOG

OOOOO OOOOOH

OOOOO OOOOOJ

OOOOO OOOOOK

OOOOO OOOOOL

OOOOO OOOOOM

OOOOO OOOOON

OOOOO OOOOOP

OOOOO OOOOOR

OOOOO OOOOOT

OOOOO OOOOOU

OOOOO OOOOOV

OOOOO OOOOOW

OOOOO OOOOOY

OOOOO OOOOOAA

OOOOOOOOOOOOOOOOOOOOOOOOOOAB

OOOOOOOOOOOOOOOOOOOOOOOOOOAC

OOOOOOOOOOOOOOOOOOOOOOOOOOAD

OOOOOOOOOOOOOOOOOOOOOOOOOOAE

OOOOOOOOOOOOOOOOOOOOOOOOOOAF

xr PRELIMINARY XRT86VL38

REV. P1.0.6 OCTAL T1/E1/J1 FRAMER/LIU COMBO

5

484 BALL - SHRINK THIN BALL GRID ARRAY (BOTTOM VIEW - SEE PIN LIST FOR DESCRIPTION)

22212019181716151413121110987654321

OOOOOOOOOOOOOOOOOOOOOOA

OOOOOOOOOOOOOOOOOOOOOOB

OOOOOOOOOOOOOOOOOOOOOOC

OOOOOOOOOOOOOOOOOOOOOOD

OOOOOOOOOOOOOOOOOOOOOOE

OOOOOOOOOOOOOOOOOOOOOOF

OOOOOOOOOOOOOOOOOOOOOOG

OOOOOOOOOOOOOOOOOOOOOOH

OOOOOOOOOOOOOOOOOOOOOOJ

OOOOOOOOOOOOOOOOOOOOOOK

OOOOOOOOOOOOOOOOOOOOOOL

OOOOOOOOOOOOOOOOOOOOOOM

OOOOOOOOOOOOOOOOOOOOOON

OOOOOOOOOOOOOOOOOOOOOOP

OOOOOOOOOOOOOOOOOOOOOOR

OOOOOOOOOOOOOOOOOOOOOOT

OOOOOOOOOOOOOOOOOOOOOOU

OOOOOOOOOOOOOOOOOOOOOOV

OOOOOOOOOOOOOOOOOOOOOOW

OOOOOOOOOOOOOOOOOOOOOOY

OOOOOOOOOOOOOOOOOOOOOOAA

OOOOOOOOOOOOOOOOOOOOOOAB

XRT86VL38 PRELIMINARY xr

OCTAL T1/E1/J1 FRAMER/LIU COMBO REV.P1.0.6

I

LIST OF PARAGRAPHS

1.0 PIN LISTS .................................................................................................................................................6

2.0 PIN DESCRIPTIONS ..............................................................................................................................14

3.0 MICROPROCESSOR INTERFACE BLOCK ..........................................................................................52

3.1 OPERATING THE MICROPROCESSOR INTERFACE IN INTEL-ASYNCHRONOUS MODE .........................53

3.1.1 THE INTEL-ASYNCHRONOUS READ-CYCLE ............................................................................................................ 54

3.1.2 THE INTEL-ASYNCHRONOUS WRITE CYCLE .......................................................................................................... 55

3.2 OPERATING THE MICROPROCESSOR INTERFACE IN THE MOTOROLA-ASYNCHRONOUS MODE ......57

3.2.1 THE MOTOROLA-ASYNCHRONOUS READ-CYCLE ................................................................................................. 58

3.2.2 THE MOTOROLA-ASYNCHRONOUS WRITE-CYCLE ................................................................................................ 59

3.3 OPERATING THE MICROPROCESSOR INTERFACE IN THE POWERPC 403 MODE .................................62

3.3.1 THE POWERPC 403 READ-CYCLE ............................................................................................................................. 63

3.3.2 THE POWERPC 403 WRITE-CYCLE ........................................................................................................................... 64

3.3.3 DMA READ/WRITE OPERATIONS .............................................................................................................................. 66

3.4 MEMORY MAPPED I/O ADDRESSING ............................................................................................................67

3.4.1 REGISTER DESCRIPTIONS ......................................................................................................................................... 74

3.5 PROGRAMMING THE LINE INTERFACE UNIT (LIU SECTION) ...................................................................265

3.6 THE INTERRUPT STRUCTURE WITHIN THE FRAMER ...............................................................................300

3.6.1 CONFIGURING THE INTERRUPT SYSTEM, AT THE FRAMER LEVEL .................................................................. 304

4.0 GENERAL DESCRIPTION AND INTERFACE .....................................................................................307

4.1 PHYSICAL INTERFACE ..................................................................................................................................307

4.2 R3 TECHNOLOGY (RELAYLESS / RECONFIGURABLE / REDUNDANCY) ................................................308

4.2.1 LINE CARD REDUNDANCY ....................................................................................................................................... 308

4.2.2 TYPICAL REDUNDANCY SCHEMES ........................................................................................................................ 308

4.2.3 1:1 AND 1+1 REDUNDANCY WITHOUT RELAYS .................................................................................................... 308

4.2.4 TRANSMIT INTERFACE WITH 1:1 AND 1+1 REDUNDANCY .................................................................................. 308

4.2.5 RECEIVE INTERFACE WITH 1:1 AND 1+1 REDUNDANCY ..................................................................................... 309

4.3 POWER FAILURE PROTECTION ...................................................................................................................310

4.4 OVERVOLTAGE AND OVERCURRENT PROTECTION ................................................................................310

4.5 NON-INTRUSIVE MONITORING .....................................................................................................................310

4.6 T1/E1 SERIAL PCM INTERFACE ...................................................................................................................311

4.7 T1/E1 FRACTIONAL INTERFACE ..................................................................................................................312

4.8 T1/E1 TIME SLOT SUBSTITUTION AND CONTROL .....................................................................................313

4.9 ROBBED BIT SIGNALING/CAS SIGNALING .................................................................................................314

4.10 OVERHEAD INTERFACE ..............................................................................................................................315

4.11 FRAMER BYPASS MODE .............................................................................................................................317

4.12 HIGH-SPEED NON-MULTIPLEXED INTERFACE ........................................................................................318

4.13 HIGH-SPEED MULTIPLEXED INTERFACE .................................................................................................319

5.0 LOOPBACK MODES OF OPERATION ...............................................................................................320

5.1 LIU PHYSICAL INTERFACE LOOPBACK DIAGNOSTICS ............................................................................320

5.1.1 LOCAL ANALOG LOOPBACK .................................................................................................................................. 320

5.1.2 REMOTE LOOPBACK ................................................................................................................................................ 320

5.1.3 DIGITAL LOOPBACK ................................................................................................................................................. 321

5.1.4 DUAL LOOPBACK ..................................................................................................................................................... 321

5.1.5 FRAMER REMOTE LINE LOOPBACK ...................................................................................................................... 321

5.1.6 FRAMER LOCAL LOOPBACK ................................................................................................................................... 322

5.2 PROGRAMMING SEQUENCE FOR SENDING LESS THAN 96-BYTE MESSAGES ....................................323

5.3 PROGRAMMING SEQUENCE FOR SENDING LARGE MESSAGES ...........................................................323

5.4 PROGRAMMING SEQUENCE FOR RECEIVING LAPD MESSAGES ...........................................................324

5.5 SS7 (SIGNALING SYSTEM NUMBER 7) FOR ESF IN DS1 ONLY ................................................................324

5.6 DS1/E1 DATALINK TRANSMISSION USING THE HDLC CONTROLLERS .................................................324

5.7 TRANSMIT BOS (BIT ORIENTED SIGNALING) PROCESSOR .....................................................................324

5.7.1 DESCRIPTION OF BOS .............................................................................................................................................. 324

5.7.2 PRIORITY CODEWORD MESSAGE .......................................................................................................................... 325

5.7.3 COMMAND AND RESPONSE INFORMATION .......................................................................................................... 325

5.8 TRANSMIT MOS (MESSAGE ORIENTED SIGNALING) PROCESSOR ........................................................325

5.8.1 DISCUSSION OF MOS ............................................................................................................................................... 325

5.8.2 PERIODIC PERFORMANCE REPORT ...................................................................................................................... 326

5.8.3 TRANSMISSION-ERROR EVENT .............................................................................................................................. 326

5.8.4 PATH AND TEST SIGNAL IDENTIFICATION MESSAGE ......................................................................................... 327

5.8.5 FRAME STRUCTURE ................................................................................................................................................. 327

xr PRELIMINARY XRT86VL38

REV. P1.0.6 OCTAL T1/E1/J1 FRAMER/LIU COMBO

II

5.8.6 FLAG SEQUENCE ...................................................................................................................................................... 327

5.8.7 ADDRESS FIELD ........................................................................................................................................................ 327

5.8.8 ADDRESS FIELD EXTENSION BIT (EA) ................................................................................................................... 327

5.8.9 COMMAND OR RESPONSE BIT (C/R) ...................................................................................................................... 327

5.8.10 SERVICE ACCESS POINT IDENTIFIER (SAPI) ...................................................................................................... 328

5.8.11 TERMINAL ENDPOINT IDENTIFIER (TEI) ............................................................................................................... 328

5.8.12 CONTROL FIELD ...................................................................................................................................................... 328

5.8.13 FRAME CHECK SEQUENCE (FCS) FIELD ............................................................................................................. 328

5.8.14 TRANSPARENCY (ZERO STUFFING) ..................................................................................................................... 328

5.9 TRANSMIT SLC®96 DATA LINK CONTROLLER .......................................................................................... 329

5.10 D/E TIME SLOT TRANSMIT HDLC CONTROLLER BLOCK V5.1 OR V5.2 INTERFACE .......................... 330

5.11 AUTOMATIC PERFORMANCE REPORT (APR) .......................................................................................... 330

5.11.1 BIT VALUE INTERPRETATION ............................................................................................................................... 330

6.0 OVERHEAD INTERFACE BLOCK ......................................................................................................332

6.1 DS1 TRANSMIT OVERHEAD INPUT INTERFACE BLOCK .......................................................................... 332

6.1.1 DESCRIPTION OF THE DS1 TRANSMIT OVERHEAD INPUT INTERFACE BLOCK .............................................. 332

6.1.2 CONFIGURE THE DS1 TRANSMIT OVERHEAD INPUT INTERFACE MODULE AS SOURCE OF THE FACILITY DATA

LINK (FDL) BITS IN ESF FRAMING FORMAT MODE ............................................................................................... 332

6.1.3 CONFIGURE THE DS1 TRANSMIT OVERHEAD INPUT INTERFACE MODULE AS SOURCE OF THE SIGNALING

FRAMING (FS) BITS IN N OR SLC®96 FRAMING FORMAT MODE ........................................................................ 334

6.1.4 CONFIGURE THE DS1 TRANSMIT OVERHEAD INPUT INTERFACE MODULE AS SOURCE OF THE REMOTE SIG-

NALING (R) BITS IN T1DM FRAMING FORMAT MODE ........................................................................................... 335

6.2 DS1 RECEIVE OVERHEAD OUTPUT INTERFACE BLOCK .........................................................................336

6.2.1 DESCRIPTION OF THE DS1 RECEIVE OVERHEAD OUTPUT INTERFACE BLOCK ............................................. 336

6.2.2 CONFIGURE THE DS1 RECEIVE OVERHEAD OUTPUT INTERFACE MODULE AS DESTINATION OF THE FACILITY

DATA LINK (FDL) BITS IN ESF FRAMING FORMAT MODE .................................................................................... 336

6.2.3 CONFIGURE THE DS1 RECEIVE OVERHEAD OUTPUT INTERFACE MODULE AS DESTINATION OF THE SIGNALING

FRAMING (FS) BITS IN N OR SLC®96 FRAMING FORMAT MODE ........................................................................ 338

6.2.4 CONFIGURE THE DS1 RECEIVE OVERHEAD OUTPUT INTERFACE MODULE AS DESTINATION OF THE REMOTE

SIGNALING (R) BITS IN T1DM FRAMING FORMAT MODE ..................................................................................... 339

6.3 E1 OVERHEAD INTERFACE BLOCK ............................................................................................................ 340

6.4 E1 TRANSMIT OVERHEAD INPUT INTERFACE BLOCK .............................................................................340

6.4.1 DESCRIPTION OF THE E1 TRANSMIT OVERHEAD INPUT INTERFACE BLOCK ................................................. 340

6.4.2 CONFIGURE THE E1 TRANSMIT OVERHEAD INPUT INTERFACE MODULE AS SOURCE OF THE NATIONAL BIT SE-

QUENCE IN E1 FRAMING FORMAT MODE .............................................................................................................. 341

6.5 E1 RECEIVE OVERHEAD INTERFACE ......................................................................................................... 342

6.5.1 DESCRIPTION OF THE E1 RECEIVE OVERHEAD OUTPUT INTERFACE BLOCK ............................................... 342

6.5.2 CONFIGURE THE E1 RECEIVE OVERHEAD OUTPUT INTERFACE MODULE AS SOURCE OF THE NATIONAL BIT

SEQUENCE IN E1 FRAMING FORMAT MODE .......................................................................................................... 343

7.0 LIU TRANSMIT PATH .........................................................................................................................345

7.1 TRANSMIT DIAGNOSTIC FEATURES ........................................................................................................... 345

7.1.1 TAOS (TRANSMIT ALL ONES) .................................................................................................................................. 345

7.1.2 ATAOS (AUTOMATIC TRANSMIT ALL ONES) ......................................................................................................... 345

7.1.3 NETWORK LOOP UP CODE ...................................................................................................................................... 345

7.1.4 NETWORK LOOP DOWN CODE ............................................................................................................................... 346

7.1.5 QRSS GENERATION .................................................................................................................................................. 346

7.2 T1 LONG HAUL LINE BUILD OUT (LBO) ...................................................................................................... 346

7.3 T1 SHORT HAUL LINE BUILD OUT (LBO) ....................................................................................................347

7.3.1 ARBITRARY PULSE GENERATOR ........................................................................................................................... 348

7.3.2 DMO (DIGITAL MONITOR OUTPUT) ......................................................................................................................... 348

7.3.3 TRANSMIT JITTER ATTENUATOR ........................................................................................................................... 349

7.4 LINE TERMINATION (TTIP/TRING) ................................................................................................................ 350

8.0 LIU RECEIVE PATH ............................................................................................................................351

8.1 LINE TERMINATION (RTIP/RRING) ............................................................................................................... 351

8.1.1 INTERNAL TERMINATION ......................................................................................................................................... 351

8.1.2 EQUALIZER CONTROL ............................................................................................................................................. 351

8.1.3 CABLE LOSS INDICATOR ......................................................................................................................................... 352

8.2 RECEIVE SENSITIVITY ................................................................................................................................... 352

8.2.1 AIS (ALARM INDICATION SIGNAL) .......................................................................................................................... 353

8.2.2 NLCD (NETWORK LOOP CODE DETECTION) ......................................................................................................... 353

8.2.3 FLSD (FIFO LIMIT STATUS DETECTION) ................................................................................................................ 354

8.2.4 RECEIVE JITTER ATTENUATOR .............................................................................................................................. 354

8.2.5 RXMUTE (RECEIVER LOS WITH DATA MUTING) ................................................................................................... 354

9.0 THE E1 TRANSMIT/RECEIVE FRAMER ............................................................................................356

XRT86VL38 PRELIMINARY xr

OCTAL T1/E1/J1 FRAMER/LIU COMBO REV.P1.0.6

III

9.1 DESCRIPTION OF THE TRANSMIT/RECEIVE PAYLOAD DATA INPUT INTERFACE BLOCK ..................356

9.1.1 BRIEF DISCUSSION OF THE TRANSMIT/RECEIVE PAYLOAD DATA INPUT INTERFACE BLOCK OPERATING AT

XRT84V24 COMPATIBLE 2.048MBIT/S MODE .......................................................................................................... 356

9.2 TRANSMIT/RECEIVE HIGH-SPEED BACK-PLANE INTERFACE .................................................................358

9.2.1 NON-MULTIPLEXED HIGH-SPEED MODE ............................................................................................................... 358

9.2.2 MULTIPLEXED HIGH-SPEED MODE ........................................................................................................................ 361

9.3 BRIEF DISCUSSION OF COMMON CHANNEL SIGNALING IN E1 FRAMING FORMAT ............................367

9.4 BRIEF DISCUSSION OF CHANNEL ASSOCIATED SIGNALING IN E1 FRAMING FORMAT .....................367

9.5 INSERT/EXTRACT SIGNALING BITS FROM TSCR REGISTER ...................................................................367

9.6 INSERT/EXTRACT SIGNALING BITS FROM TXCHN[0]_N/TXSIG PIN ........................................................367

9.7 ENABLE CHANNEL ASSOCIATED SIGNALING AND SIGNALING DATA SOURCE CONTROL ...............368

10.0 THE DS1 TRANSMIT/RECEIVE FRAMER ........................................................................................369

10.1 DESCRIPTION OF THE TRANSMIT/RECEIVE PAYLOAD DATA INPUT INTERFACE BLOCK ................369

10.1.1 BRIEF DISCUSSION OF THE TRANSMIT/RECEIVE PAYLOAD DATA INPUT INTERFACE BLOCK OPERATING AT

1.544MBIT/S MODE ..................................................................................................................................................... 369

10.2 TRANSMIT/RECEIVE HIGH-SPEED BACK-PLANE INTERFACE ...............................................................371

10.2.1 T1 TRANSMIT/RECEIVE INTERFACE - MVIP 2.048 MHZ ...................................................................................... 371

10.2.2 NON-MULTIPLEXED HIGH-SPEED MODE ............................................................................................................. 372

10.2.3 MULTIPLEXED HIGH-SPEED MODE ...................................................................................................................... 374

10.3 BRIEF DISCUSSION OF ROBBED-BIT SIGNALING IN DS1 FRAMING FORMAT ....................................382

10.3.1 CONFIGURE THE FRAMER TO TRANSMIT ROBBED-BIT SIGNALING ............................................................... 383

10.3.2 INSERT SIGNALING BITS FROM TSCR REGISTER .............................................................................................. 383

10.3.3 INSERT SIGNALING BITS FROM TXSIG_N PIN ..................................................................................................... 384

11.0 ALARMS AND ERROR CONDITIONS ..............................................................................................386

11.1 AIS ALARM ....................................................................................................................................................386

11.2 RED ALARM ..................................................................................................................................................388

11.3 YELLOW ALARM ..........................................................................................................................................389

11.4 BIPOLAR VIOLATION ...................................................................................................................................391

11.5 E1 BRIEF DISCUSSION OF ALARMS AND ERROR CONDITIONS ...........................................................393

11.5.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS .................................................................................... 399

11.5.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM ................................................................... 400

11.5.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM ............................................................. 400

11.5.4 TRANSMIT YELLOW ALARM .................................................................................................................................. 401

11.5.5 TRANSMIT CAS MULTI-FRAME YELLOW ALARM ............................................................................................... 401

11.6 T1 BRIEF DISCUSSION OF ALARMS AND ERROR CONDITIONS ............................................................402

11.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS .................................................................................... 405

11.6.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM ................................................................... 406

11.6.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM ............................................................. 406

11.6.4 TRANSMIT YELLOW ALARM IN SF MODE ............................................................................................................ 407

11.6.5 TRANSMIT YELLOW ALARM IN ESF MODE .......................................................................................................... 407

11.6.6 TRANSMIT YELLOW ALARM IN N MODE .............................................................................................................. 407

11.6.7 TRANSMIT YELLOW ALARM IN T1DM MODE ....................................................................................................... 407

12.0 PERFORMANCE MONITORING (PMON) .........................................................................................409

12.1 RECEIVE LINE CODE VIOLATION COUNTER (16-BIT) ..............................................................................409

12.2 16-BIT RECEIVE FRAME ALIGNMENT ERROR COUNTER (16-BIT) .........................................................409

12.3 RECEIVE SEVERELY ERRORED FRAME COUNTER (8-BIT) ....................................................................409

12.4 RECEIVE CRC-6/4 BLOCK ERROR COUNTER (16-BIT) ............................................................................409

12.5 RECEIVE FAR-END BLOCK ERROR COUNTER (16-BIT) ..........................................................................409

12.6 RECEIVE SLIP COUNTER (8-BIT) ................................................................................................................409

12.7 RECEIVE LOSS OF FRAME COUNTER (8-BIT) ..........................................................................................409

12.8 RECEIVE CHANGE OF FRAME ALIGNMENT COUNTER (8-BIT) ..............................................................409

12.9 FRAME CHECK SEQUENCE ERROR COUNTERS 1, 2, AND 3 (8-BIT EACH) .........................................409

12.10 PRBS ERROR COUNTER (16-BIT) .............................................................................................................409

12.11 TRANSMIT SLIP COUNTER (8-BIT) ...........................................................................................................409

12.12 EXCESSIVE ZERO VIOLATION COUNTER (16-BIT) .................................................................................410

13.0 APPENDIX A: DS-1/E1 FRAMING FORMATS ..................................................................................411

13.1 THE E1 FRAMING STRUCTURE ..................................................................................................................411

13.1.1 FAS FRAME .............................................................................................................................................................. 411

13.1.2 NON-FAS FRAME ..................................................................................................................................................... 412

13.2 THE E1 MULTI-FRAME STRUCTURE ..........................................................................................................413

13.2.1 THE CRC MULTI-FRAME STRUCTURE .................................................................................................................. 413

13.2.2 CAS MULTI-FRAMES AND CHANNEL ASSOCIATED SIGNALING ...................................................................... 414

xr PRELIMINARY XRT86VL38

REV. P1.0.6 OCTAL T1/E1/J1 FRAMER/LIU COMBO

IV

13.3 THE DS1 FRAMING STRUCTURE ............................................................................................................... 416

13.4 T1 SUPER FRAME FORMAT (SF) ................................................................................................................ 417

13.5 T1 EXTENDED SUPERFRAME FORMAT (ESF) .......................................................................................... 418

13.6 T1 NON-SIGNALING FRAME FORMAT ....................................................................................................... 420

13.7 T1 DATA MULTIPLEXED FRAMING FORMAT (T1DM) ............................................................................... 420

13.8 SLC-96 FORMAT (SLC-96) ........................................................................................................................... 421

XRT86VL38 PRELIMINARY xr

OCTAL T1/E1/J1 FRAMER/LIU COMBO REV.P1.0.6

V

LIST OF FIGURES

Figure 1.: XRT86VL38 8-channel DS1 (T1/E1/J1) Framer/LIU Combo .............................................................................1

Figure 2.: Simplified Block Diagram of the Microprocessor Interface Block ....................................................................52

Figure 3.: Intel µP Interface Signals During Read Operations .........................................................................................55

Figure 4.: Intel µP Interface Signals During Write Operations .........................................................................................56

Figure 5.: Intel µP Interface Timing During Programmed I/O Read and Write Operations ..............................................57

Figure 6.: Motorola Asynchronous Mode Interface Signals During Read Operations .....................................................59

Figure 7.: Motorola Asychronous Mode Interface Signals During Write Operations ........................................................61

Figure 8.: Motorola Asychronous Mode Interface Signals During Programmed I/O Read and Write Operations ...........61

Figure 9.: Power PC Mode Interface Signals During Read Operations ...........................................................................64

Figure 10.: Power PC Mode Interface Signals During Write Operations .........................................................................66

Figure 11.: DMA Mode for the XRT86VL38 and a Microprocessor .................................................................................67

Figure 12.: LIU Transmit Connection Diagram Using Internal Termination ...................................................................307

Figure 13.: LIU Receive Connection Diagram Using Internal Termination ...................................................................307

Figure 14.: Simplified Block Diagram of the Transmit Interface for 1:1 and 1+1 Redundancy ......................................308

Figure 15.: Simplified Block Diagram of the Receive Interface for 1:1 and 1+1 Redundancy .......................................309

Figure 16.: Simplified Block Diagram of a Non-Intrusive Monitoring Application ...........................................................310

Figure 17.: Transmit T1/E1 Serial PCM Interface ..........................................................................................................311

Figure 18.: Receive T1/E1 Serial PCM Interface ...........................................................................................................311

Figure 19.: T1 Fractional Interface .................................................................................................................................312

Figure 20.: T1/E1 Time Slot Substitution and Control ....................................................................................................313

Figure 21.: Robbed Bit Signaling / CAS Signaling .........................................................................................................314

Figure 22.: ESF / CAS External Signaling Bus ..............................................................................................................314

Figure 23.: SF / SLC-96 or 4-code Signaling in ESF / CAS External Signaling Bus ......................................................315

Figure 24.: T1/E1 Overhead Interface ...........................................................................................................................315

Figure 25.: T1 External Overhead Datalink Bus ............................................................................................................316

Figure 26.: E1 Overhead External Datalink Bus ............................................................................................................316

Figure 27.: Simplified Block Diagram of the Framer Bypass Mode ...............................................................................317

Figure 28.: T1 High-Speed Non-Multiplexed Interface ...................................................................................................318

Figure 29.: E1 High-Speed Non-Multiplexed Interface ..................................................................................................318

Figure 30.: Transmit High-Speed Bit Multiplexed Block Diagram ..................................................................................319

Figure 31.: Receive High-Speed Bit Multiplexed Block Diagram ...................................................................................319

Figure 32.: Simplified Block Diagram of Local Analog Loopback ..................................................................................320

Figure 33.: Simplified Block Diagram of Remote Loopback ...........................................................................................320

Figure 34.: Simplified Block Diagram of Digital Loopback .............................................................................................321

Figure 35.: Simplified Block Diagram of Dual Loopback ................................................................................................321

Figure 36.: Simplified Block Diagram of the Framer Remote Line Loopback ................................................................322

Figure 37.: Simplified Block Diagram of the Framer Local Loopback ............................................................................322

Figure 38.: HDLC Controllers .........................................................................................................................................323

Figure 39.: LAPD Frame Structure ................................................................................................................................326

Figure 40.: Block Diagram of the DS1 Transmit Overhead Input Interface of the XRT86VL38 .....................................332

Figure 41.: DS1 Transmit Overhead Input Interface Timing in ESF Framing Format mode ..........................................334

Figure 42.: DS1 Transmit Overhead Input Timing in N or SLC®96 Framing Format Mode ..........................................335

Figure 43.: DS1 Transmit Overhead Input Interface module in T1DM Framing Format mode ......................................335

Figure 44.: Block Diagram of the DS1 Receive Overhead Output Interface of XRT86VL38 .........................................336

Figure 45.: DS1 Receive Overhead Output Interface module in ESF framing format mode .........................................338

Figure 46.: DS1 Receive Overhead Output Interface Timing in N or SLC®96 Framing Format mode ..........................339

Figure 47.: DS1 Receive Overhead Output Interface Timing in T1DM Framing Format mode .....................................340

Figure 48.: Block Diagram of the E1 Transmit Overhead Input Interface of XRT86VL38 ..............................................340

Figure 49.: E1 Transmit Overhead Input Interface Timing .............................................................................................342

Figure 50.: Block Diagram of the E1 Receive Overhead Output Interface of XRT86VL38 ............................................343

Figure 51.: E1 Receive Overhead Output Interface Timing ...........................................................................................344

Figure 52.: TAOS (Transmit All Ones) ...........................................................................................................................345

Figure 53.: Simplified Block Diagram of the ATAOS Function .......................................................................................345

Figure 54.: Network Loop Up Code Generation .............................................................................................................345

Figure 55.: Network Loop Down Code Generation ........................................................................................................346

Figure 56.: Long Haul Line Build Out with -7.5dB Attenuation .......................................................................................346

Figure 57.: Long Haul Line Build Out with -15dB Attenuation ........................................................................................347

Figure 58.: Long Haul Line Build Out with -22.5dB Attenuation .....................................................................................347

xr PRELIMINARY XRT86VL38

REV. P1.0.6 OCTAL T1/E1/J1 FRAMER/LIU COMBO

VI

Figure 59.: Arbitrary Pulse Segment Assignment ..........................................................................................................348

Figure 60.: Typical Connection Diagram Using Internal Termination ............................................................................350

Figure 61.: Typical Connection Diagram Using Internal Termination ...........................................................................351

Figure 62.: Simplified Block Diagram of the Equalizer and Peak Detector ....................................................................352

Figure 63.: Simplified Block Diagram of the Cable Loss Indicator .................................................................................352

Figure 64.: Test Configuration for Measuring Receive Sensitivity .................................................................................353

Figure 65.: Process Block for Automatic Loop Code Detection .....................................................................................354

Figure 66.: Simplified Block Diagram of the RxMUTE Function ....................................................................................355

Figure 67.: Interfacing the Transmit Path to local terminal equipment ..........................................................................356

Figure 69.: Waveforms for connecting the Transmit Payload Data Input Interface Block to local Terminal Equipment 357

Figure 68.: Interfacing the Receive Path to local terminal equipment ...........................................................................357

Figure 70.: Waveforms for connecting the Receive Payload Data Input Interface Block to local Terminal Equipment .358

Figure 71.: Transmit Non-Multiplexed High-Speed Connection to local terminal equipment using MVIP 2.048Mbit/s,

4.096Mbit/s, or 8.192Mbit/s .............................................................................................................................359

Figure 72.: Receive Non-Multiplexed High-Speed Connection to local terminal equipment using MVIP 2.048Mbit/s,

4.096Mbit/s, or 8.192Mbit/s .............................................................................................................................359

Figure 73.: Waveforms for Connecting the Transmit Non-Multiplexed High-Speed Input Interface at MVIP 2.048Mbit/s,

4.096Mbit/s, and 8.192Mbit/s ..........................................................................................................................360

Figure 74.: Waveforms for Connecting the Receive Non-Multiplexed High-Speed Input Interface at MVIP 2.048Mbit/s,

4.096Mbit/s, and 8.192Mbit/s ..........................................................................................................................360

Figure 75.: Interfacing XRT86VL38 Transmit to local terminal equipment using 16.384Mbit/s, HMVIP 16.384Mbit/s, and

H.100 16.384Mbit/s .........................................................................................................................................364

Figure 76.: Timing signal when the framer is running at Bit-Multiplexed 16.384Mbit/s mode ........................................364

Figure 77.: Waveforms for Connecting the Transmit Multiplexed High-Speed Input Interface at HMVIP And H.100

16.384Mbit/s mode ..........................................................................................................................................365

Figure 78.: Interfacing XRT86VL38 Receive to local terminal equipment using 16.384Mbit/s, HMVIP 16.384Mbit/s, and

H.100 16.384Mbit/s .........................................................................................................................................366

Figure 79.: Timing Signal When the Receive Framer is running at 16.384MHz Bit-Mulitplexed Mode .........................366

Figure 80.: Timing Signal wehn the Receive Framer is Running at HMVIP and H100 16.384MHz Mode .................... 366

Figure 81.: Timing Diagram of the TxSIG Input .............................................................................................................368

Figure 82.: Timing Diagram of the RxSIG Output ..........................................................................................................368

Figure 83.: Interfacing the Transmit Path to local terminal equipment ..........................................................................369

Figure 85.: Waveforms for connecting the Transmit Payload Data Input Interface Block to local Terminal Equipment 370

Figure 84.: Interfacing the Receive Path to local terminal equipment ...........................................................................370

Figure 86.: Waveforms for connecting the Receive Payload Data Input Interface Block to local Terminal Equipment .371

Figure 87.: Transmit Non-Multiplexed High-Speed Connection to local terminal equipment using MVIP 2.048Mbit/s,

4.096Mbit/s, or 8.192Mbit/s .............................................................................................................................372

Figure 89.: Waveforms for Connecting the Transmit Non-Multiplexed High-Speed Input Interface at MVIP 2.048Mbit/s,

4.096Mbit/s, and 8.192Mbit/s ..........................................................................................................................373

Figure 88.: Receive Non-Multiplexed High-Speed Connection to local terminal equipment using MVIP 2.048Mbit/s,

4.096Mbit/s, or 8.192Mbit/s .............................................................................................................................373

Figure 90.: Waveforms for Connecting the Receive Non-Multiplexed High-Speed Input Interface at MVIP 2.048Mbit/s,

4.096Mbit/s, and 8.192Mbit/s ..........................................................................................................................374

Figure 91.: Interfacing XRT86VL38 Transmit to local terminal equipment using 16.384Mbit/s, HMVIP 16.384Mbit/s, and

H.100 16.384Mbit/s .........................................................................................................................................376

Figure 92.: Timing Signals When the Transmit Framer is Running at 12.352 Bit-Multiplexed Mode ............................ 376

Figure 93.: Timing signals when the transmit framer is running at 16.384 Bit-Multiplexed mode ..................................378

Figure 94.: Timing signals when the transmit framer is running at HMVIP / H.100 16.384MHz Mode ..........................380

Figure 95.: Interfacing XRT86VL38 Receive to local terminal equipment using 16.384Mbit/s, HMVIP 16.384Mbit/s, and

H.100 16.384Mbit/s .........................................................................................................................................381

Figure 96.: Waveforms for Connecting the Receive Multiplexed High-Speed Input Interface at 12.352Mbit/s mode ...381

Figure 97.: Waveforms for Connecting the Receive Multiplexed High-Speed Input Interface at 16.384Mbit/s mode ...381

Figure 98.: Waveforms for Connecting the Receive Multiplexed High-Speed Input Interface at HMVIP and H.100 16.384Mbit/

s mode ............................................................................................................................................................382

Figure 99.: Timing Diagram of the TxSig_n Input ..........................................................................................................384

Figure 100.: Simple Diagram of E1 system model ........................................................................................................394

Figure 101.: Generation of Yellow Alarm by the Repeater upon detection of line failure ..............................................395

Figure 102.: Generation of AIS by the Repeater upon detection of line failure .............................................................396

Figure 103.: Generation of Yellow Alarm by the CPE upon detection of AIS originated by the Repeater .....................397

Figure 104.: Generation of CAS Multi-frame Yellow Alarm and AIS16 by the Repeater ...............................................398

XRT86VL38 PRELIMINARY xr

OCTAL T1/E1/J1 FRAMER/LIU COMBO REV.P1.0.6

VII

Figure 105.:Generation ofCASMulti-frame Yellow Alarm bythe CPE upon detection of“AIS16” patternsentby theRepeater

399

Figure 106.: Simple Diagram of DS1 System Model .....................................................................................................402

Figure 107.: Generation of Yellow Alarm by the CPE upon detection of line failure ......................................................403

Figure 108.: Generation of AIS by the Repeater upon detection of Yellow Alarm originated by the CPE .....................404

Figure 109.: Generation of Yellow Alarm by the CPE upon detection of AIS originated by the Repeater .....................405

Figure 110.: Single E1 Frame Diagram .........................................................................................................................411

Figure 111.: Frame/Byte Format of the CAS Multi-Frame Structure ..............................................................................414

Figure 112.: E1 Frame Format .......................................................................................................................................415

Figure 113.: T1 Frame Format .......................................................................................................................................416

Figure 114.: T1 Superframe PCM Format .....................................................................................................................417

Figure 115.: T1 Extended Superframe Format ..............................................................................................................418

Figure 116.: T1DM Frame Format .................................................................................................................................420

Figure 117.: ITU G.703 Pulse Template ........................................................................................................................426

Figure 118.: DSX-1 Pulse Template (normalized amplitude) .........................................................................................427

xr PRELIMINARY XRT86VL38

REV. P1.0.6 OCTAL T1/E1/J1 FRAMER/LIU COMBO

VIII

LIST OF TABLES

Table 1:: 420 Ball List by Ball Number ...............................................................................................................................6

Table 2:: 484 Ball List by Ball Number .............................................................................................................................10

Table 3:: Selecting the Microprocessor Interface Mode ..................................................................................................52

Table 4:: The Roles of Various Microprocessor Interface Pins, when configured to operate in the Intel-Asynchronous Mode

53

Table 5:: Intel Microprocessor Interface Timing Specifications .......................................................................................57

Table 6:: The Roles of Various Microprocessor Interface Pins, when configured to operate in the Motorola-Asynchronous

Mode .................................................................................................................................................................58

Table 8:: The Roles of Various Microprocessor Interface Pins, when configured to operate in the Power PC Mode ..... 62

Table 7:: Motorola Asychronous Mode Microprocessor Interface Timing Specifications ................................................ 62

Table 9:: XRT86VL38 Framer/LIU Register Map .............................................................................................................67

Table 10:: Register Summary ..........................................................................................................................................68

Table 11:: Clock Select Register .....................................................................................................................................74

Table 12:: Line Interface Control Register .......................................................................................................................75

Table 13:: General Purpose Input/Output 0 Control Register ..........................................................................................77

Table 14:: General Purpose Input/Output 1 Control Register ..........................................................................................81

Table 15:: Framing Select Register-E1 Mode ..................................................................................................................85

Table 16:: Framing Select Register-T1 Mode ..................................................................................................................89

Table 17:: Alarm Generation Register - E1 Mode ............................................................................................................91

Table 18:: Alarm Generation Register -T1 Mode .............................................................................................................93

Table 19:: yellow alarm duration and format when one second rule is not enforced .......................................................94

Table 20:: yellow alarm duration and format when one second rule is enforced .............................................................95

Table 21:: Synchronization MUX Register - E1 Mode .....................................................................................................97

Table 22:: Synchronization MUX Register - T1 Mode .....................................................................................................99

Table 23:: Transmit Signaling and Data Link Select Register - E1 Mode ......................................................................102

Table 24:: Transmit Signaling and Data Link Select Register - T1 Mode ......................................................................106

Table 25:: Framing Control Register E1 Mode ..............................................................................................................107

Table 26:: Framing Control Register T1 Mode ..............................................................................................................110

Table 27:: Receive Signaling & Data Link Select Register - E1 Mode ..........................................................................111

Table 28:: Receive Signaling & Data Link Select Register (RSDLSR) T1 Mode ...........................................................114

Table 29:: Signaling Change Register 0 - T1/E1 Mode .................................................................................................116

Table 30:: Signaling Change Register 1 - T1/E1 Mode .................................................................................................117

Table 31:: Signaling Change Register 2 - T1/E1 Mode .................................................................................................117

Table 32:: Signaling Change Register 3 - E1 Mode ......................................................................................................118

Table 33:: Register 16 - E1 Mode Signaling Change Register 3 (SCR 3) Hex Address: 0xn110

118

Table 34:: Receive National Bits Register .....................................................................................................................118

Table 35:: Receive Extra Bits Register ..........................................................................................................................119

Table 36:: Data Link Control Register ............................................................................................................................121

Table 37:: Transmit Data Link Byte Count Register ......................................................................................................123

Table 38:: Receive Data Link Byte Count Register .......................................................................................................123

Table 39:: Slip Buffer Control Register ..........................................................................................................................124

Table 40:: FIFO Latency Register ..................................................................................................................................125

Table 41:: DMA 0 (Write) Configuration Register ..........................................................................................................126

Table 42:: DMA 1 (Read) Configuration Register ..........................................................................................................127

Table 43:: Interrupt Control Register .............................................................................................................................128

Table 44:: LAPD Select Register ...................................................................................................................................128

Table 45:: Customer Installation Alarm Generation Register ........................................................................................129

Table 46:: Performance Report Control Register ..........................................................................................................130

Table 47:: Gapped Clock Control Register ....................................................................................................................131

Table 48:: Transmit Interface Control Register - E1 Mode ............................................................................................132

Table 49:: Transmit Interface Speed When Multiplexed Mode is Disabled (TxMUXEN = 0) .........................................134

Table 50:: Transmit Interface Speed when Multiplexed Mode is Enabled (TxMUXEN = 1) ..........................................135

Table 51:: Transmit Interface Control Register - T1 Mode ............................................................................................136

Table 52:: Transmit Interface Speed When Multiplexed Mode is Disabled (TxMUXEN = 0) .........................................138

Table 53:: Transmit Interface Speed when Multiplexed Mode is Enabled (TxMUXEN = 1) ..........................................139

Table 54:: Receive Interface Control Register (RICR) - E1 Mode .................................................................................140

Table 55:: Receive Interface Speed When Multiplexed Mode is Disabled (TxMUXEN = 0) ..........................................142

XRT86VL38 PRELIMINARY xr

OCTAL T1/E1/J1 FRAMER/LIU COMBO REV.P1.0.6

IX

Table 56:: Receive Interface Speed when Multiplexed Mode is Enabled (TxMUXEN = 1) ...........................................143

Table 57:: Receive Interface Control Register (RICR) - T1 Mode .................................................................................144

Table 58:: Receive Interface Speed When Multiplexed Mode is Disabled (TxMUXEN = 0) ..........................................146

Table 59:: Receive Interface Speed when Multiplexed Mode is Enabled (TxMUXEN = 1) ...........................................147

Table 60:: DS1/E1 Test Register 1 ................................................................................................................................148

Table 61:: DS1/E1 Test Register 2(TR2) .......................................................................................................................151

Table 62:: Loopback Code Control Register ..................................................................................................................153

Table 63:: Transmit Loopback Coder Register ..............................................................................................................155

Table 64:: Receive Loopback Activation Code Register ................................................................................................155

Table 65:: Receive Loopback Deactivation Code Register ............................................................................................156

Table 66:: Receive T1/E1 Defect Detection Enable Register ........................................................................................156

Table 67:: Transmit Sa Select Register .........................................................................................................................156

Table 68:: Transmit Sa Auto Control Register 1 - E1 Mode Only ..................................................................................158

Table 69:: Conditions on Receive side When TSACR1 bits Are enabled ......................................................................160

Table 70:: Transmit Sa Auto Control Register 2 ............................................................................................................161

Table 71:: Conditions on Receive side When TSACR2 bits enabled ............................................................................162

Table 72:: Transmit Sa4 Register ..................................................................................................................................163

Table 73:: Transmit Sa5 Register ..................................................................................................................................163

Table 74:: Transmit Sa6 Register ..................................................................................................................................163

Table 75:: Transmit Sa7 Register ..................................................................................................................................164

Table 76:: Transmit Sa8 Register ..................................................................................................................................164

Table 77:: Receive Sa4 Register ...................................................................................................................................164

Table 78:: Receive Sa5 Register ...................................................................................................................................165

Table 79:: Receive Sa6 Register ...................................................................................................................................165

Table 80:: Receive Sa7 Register ...................................................................................................................................165

Table 81:: Receive Sa8 Register ...................................................................................................................................166

Table 82:: Transmit SPRM Control Register - T1 Mode Only ........................................................................................166

Table 83:: Data Link Control Register ............................................................................................................................167

Table 84:: Transmit Data Link Byte Count Register .......................................................................................................169

Table 85:: Receive Data Link Byte Count Register ........................................................................................................169

Table 86:: Data Link Control Register ............................................................................................................................170

Table 87:: Transmit Data Link Byte Count Register .......................................................................................................172

Table 88:: Receive Data Link Byte Count Register ........................................................................................................173

Table 89:: Device ID Register ........................................................................................................................................173

Table 90:: Revision ID Register .....................................................................................................................................174

Table 91:: Transmit Channel Control Register 0 to 31 E1 Mode ...................................................................................174

Table 92:: Transmit Channel Control Register 0 to 31 T1 Mode ...................................................................................177

Table 93:: Transmit User Code Register 0 to 31 ...........................................................................................................181

Table 94:: Transmit Signaling Control Register x - E1 Mode .........................................................................................181

Table 95:: Transmit Signaling Control Register x - T1 Mode .........................................................................................184

Table 96:: Receive Channel Control Register x (RCCR 0-31) - E1 Mode .....................................................................186

Table 97:: Receive Channel Control Register x (RCCR 0-23) - T1 Mode .....................................................................189

Table 98:: Receive User Code Register x (RUCR 0-31) ................................................................................................193

Table 99:: Receive Signaling Control Register x (RSCR) (0-31) ...................................................................................193

Table 100:: Receive Substitution Signaling Register (RSSR) E1 Mode ........................................................................196

Table 101:: Receive Substitution Signaling Register (RSSR) T1 Mode ........................................................................197

Table 102:: Receive Signaling Array Register 0 to 31 ...................................................................................................198

Table 103:: LAPD Buffer 0 Control Register ..................................................................................................................199

Table 104:: LAPD Buffer 1 Control Register ..................................................................................................................199

Table 105:: PMON T1/E1 Receive Line Code (bipolar) Violation Counter ....................................................................200

Table 106:: PMON T1/E1 Receive Line Code (bipolar) Violation Counter ....................................................................200

Table 107:: PMON T1/E1 Receive Framing Alignment Bit Error Counter .....................................................................200

Table 108:: PMON T1/E1 Receive Framing Alignment Bit Error Counter .....................................................................201

Table 109:: PMON T1/E1 Receive Severely Errored Frame Counter ...........................................................................201

Table 110:: PMON T1/E1 Receive CRC-4 Block Error Counter - MSB .........................................................................202

Table 111:: PMON T1/E1 Receive CRC-4 Block Error Counter - LSB ..........................................................................202

Table 112:: PMON E1 Receive Far-End BLock Error Counter - MSB ...........................................................................203

Table 113:: PMON E1 Receive Far End Block Error Counter .......................................................................................203

Table 114:: PMON T1/E1 Receive Slip Counter ............................................................................................................204

Table 115:: PMON T1/E1 Receive Loss of Frame Counter ...........................................................................................204

xr PRELIMINARY XRT86VL38

REV. P1.0.6 OCTAL T1/E1/J1 FRAMER/LIU COMBO

X

Table 116:: PMON T1/E1 Receive Change of Frame Alignment Counter .....................................................................204

Table 117:: PMON LAPD T1/E1 Frame Check Sequence Error Counter 1 ..................................................................205

Table 118:: T1/E1 PRBS Bit Error Counter MSB ...........................................................................................................205

Table 119:: T1/E1 PRBS Bit Error Counter LSB ............................................................................................................205

Table 120:: T1/E1 Transmit Slip Counter ......................................................................................................................206

Table 121:: T1/E1 Excessive Zero Violation Counter MSB ...........................................................................................206

Table 122:: T1/E1 Excessive Zero Violation Counter LSB ............................................................................................206

Table 123:: T1/E1 Frame Check Sequence Error Counter 2 .........................................................................................207

Table 124:: T1/E1 Frame Check Sequence Error Counter 3 .........................................................................................207

Table 125:: Block Interrupt Status Register ...................................................................................................................208

Table 126:: Block Interrupt Enable Register ..................................................................................................................210

Table 127:: Alarm & Error Interrupt Status Register ......................................................................................................213

Table 128:: Alarm & Error Interrupt Enable Register - T1/E1 Mode ..............................................................................217

Table 129:: Framer Interrupt Status Register E1 Mode .................................................................................................220

Table 130:: Framer Interrupt Status Register T1 Mode .................................................................................................223

Table 131:: Framer Interrupt Enable Register E1 Mode ................................................................................................226

Table 132:: Framer Interrupt Enable Register T1 Mode ................................................................................................229

Table 133:: Data Link Status Register 1 ........................................................................................................................230

Table 134:: Data Link Interrupt Enable Register 1 .........................................................................................................232

Table 135:: Slip Buffer Interrupt Status Register (SBISR) - T1/E1 Mode ......................................................................234

Table 136:: Slip Buffer Interrupt Enable Register (SBIER) - T1/E1 Mode .....................................................................238

Table 137:: Receive Loopback Code Interrupt and Status Register (RLCISR) .............................................................240

Table 138:: Receive Loopback Code Interrupt Enable Register (RLCIER) ...................................................................243

Table 139:: Receive SA Interrupt Register (RSAIR) - E1 Mode Only ............................................................................245