MB3773

6

■

■■

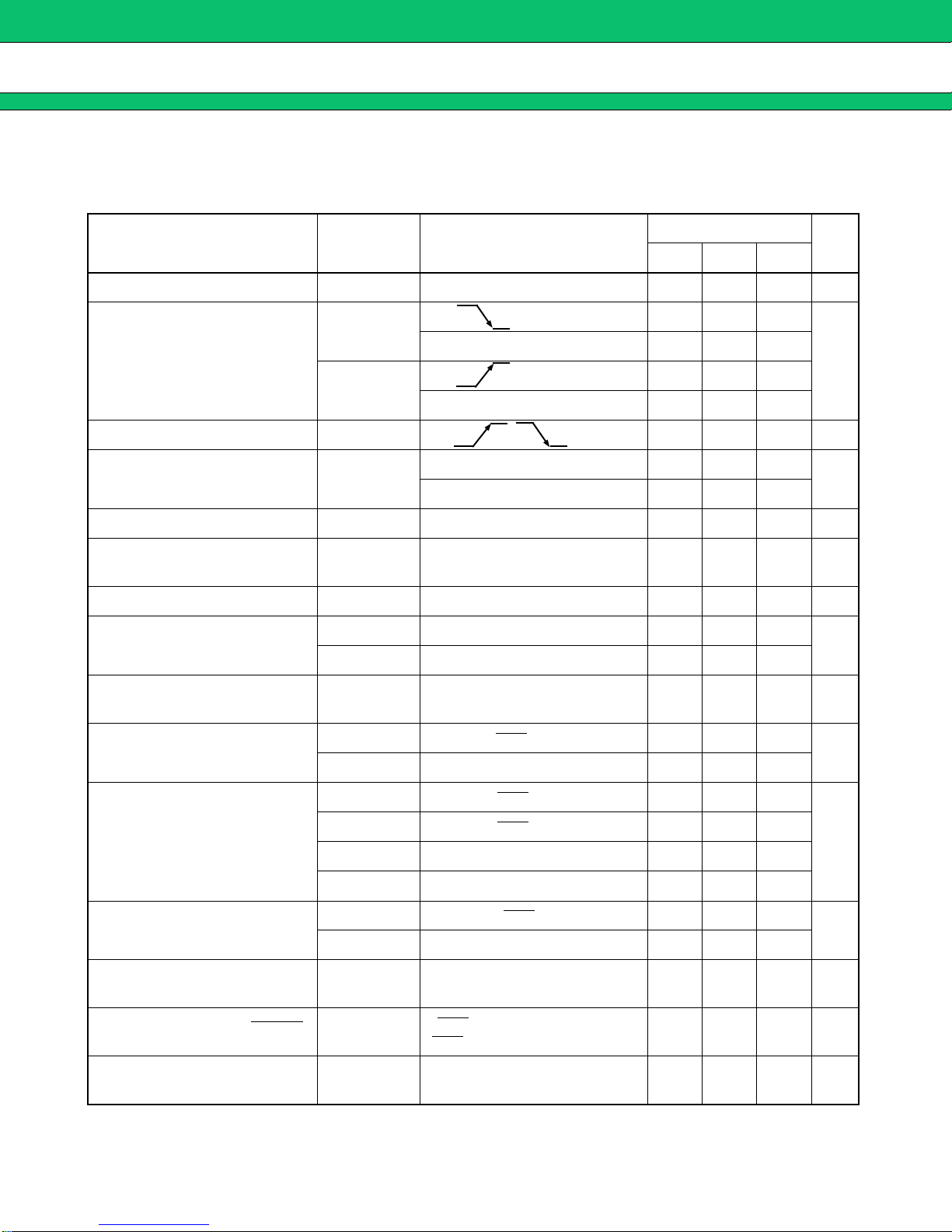

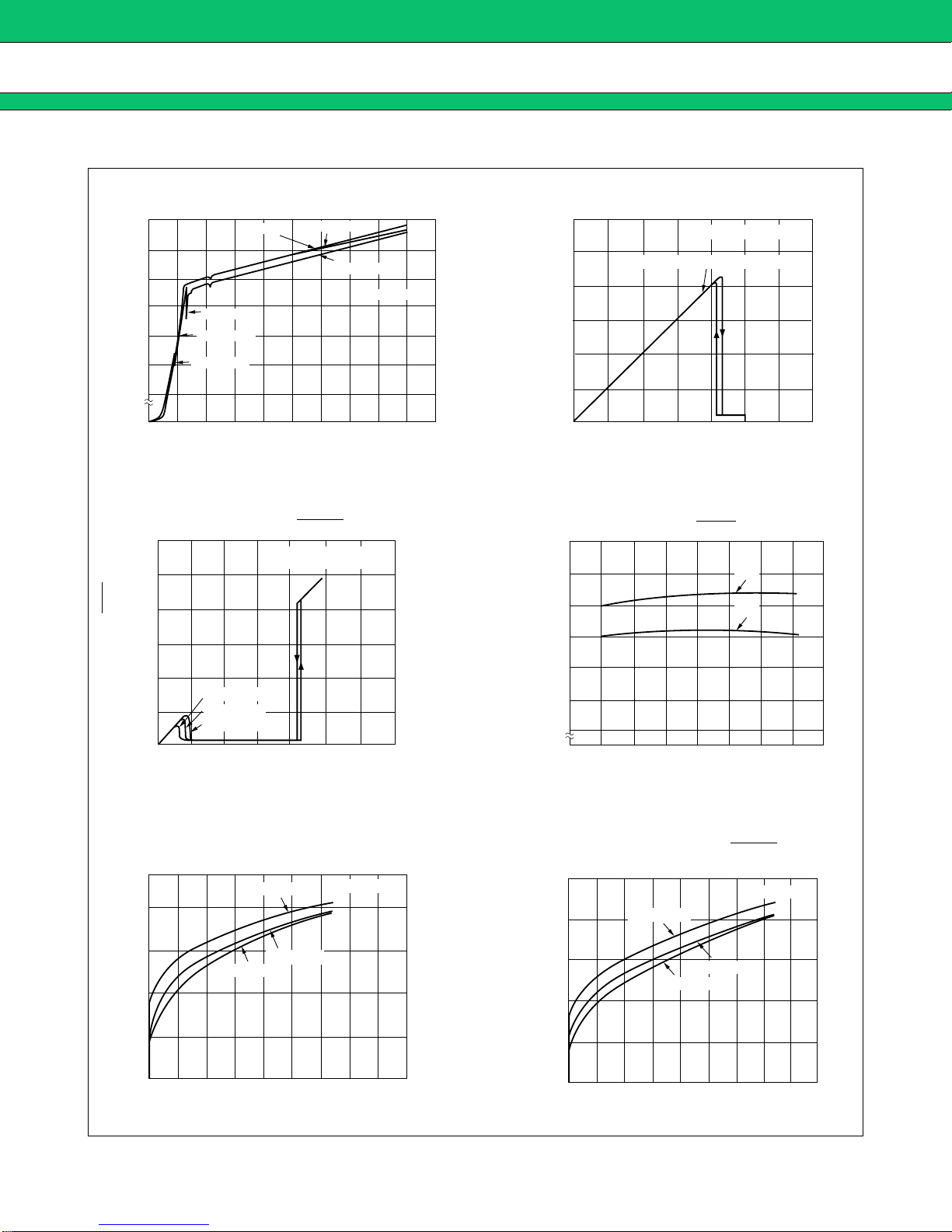

■OPERATION SEQUENCE

(1) When Vcc rises to about 0.8 V, RESET goes “Low” and RESET goes “High”.

The pull-up current of approximately 1 µA (Vcc = 0.8 V) is output from RESET.

(2) When Vcc rises to VSH ( := 4.3V) , the charge with CTstarts.

At this time, the output is being reset.

(3) When CTbegins charging, RESET goes “High” and RESET goes “Low”.

After TPR reset of the output is released.

Reset hold time: TPR (ms) := 1000 ×CT(µF)

After releasing reset, the discharge of CTstarts, and watch-dog timer operation starts.

TPR is not influenced by the CK input.

(4) C changes from the discharge into the charge if the clock (Negative edge) is input to the CK terminal

while discharging CT.

(5) C changes from the charge into the discharge when the voltage of CTreaches a constant

threshold ( := 1.4 V) .

(4) and (5) are repeated while a normal clock is input by the logic system.

(6) When the clock is cut off, gets, and the voltage of CTfalls on threshold ( := 0.4 V) of reset on, RESET goes

“Low” and RESET goes “High”.

Discharge time of CTuntil reset is output: TWD is watch-dog timer monitoring time.

TWD (ms) := 100 ×CT(µF)

Because the charging time of CTis added at accurate time from stop of the clock and getting to the output

of reset of the clock, TWD becomes maximum TWD +TWR by minimum TWD.

(7) Reset time in operating watch-dog timer:TWR is charging time where the voltage of CTgoes up to off

threshold ( := 1.4 V) for reset.

TWR (ms) := 20 ×CT(µF)

Reset of the output is released after CTreaches an off threshold for reset, and CTstarts the discharge,

after that if the clock is normally input, operation repeats (4) and (5) , when the clock is cut off, operation

repeats (6) and (7) .

(8) When Vcc falls on VSL ( := 4.2 V) , reset is output. CTis rapidly discharged of at the same time.

(9) When Vcc goes up to VSH, the charge with CTis started.

When Vcc is momentarily low,

After falling VSL or less Vcc, the time to going up is the standard value of the Vcc input pulse width in VSH or

more.

After the charge of CTis discharged, the charge is started if it is TPI or more.

(10) Reset of the output is released after TPR, after Vcc becomes VSH or more, and the watch-dog timer starts.

After that, when Vcc becomes VSL or less, (8) to (10) is repeated.

(11) While power supply is off, when Vcc becomes VSL or less, reset is output.

(12) The reset output is maintained until Vcc becomes 0.8 V when Vcc falls on 0 V.