Future Electronics Microsemi User manual

Future Electronics - Microsemi

Creative Development Board

User Guide - Rev. 1

Page 2 – Revision 1

Table of Contents

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Contents and System Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Hardware Components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

PLL Parts/Usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Power Supplies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Mini USB Connector for Power, JTAG and UART Connectivity . . . . . . . . . . 10

Programming or Re-Programming the Example Design. . . . . . . . . . . . . . . . 11

Clock Circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Differential I/O Standards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Setup and Running Out-of-the-box demo . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Package Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Memory Setups . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Schematics – Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

– FTDI-JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

– DDR SDRAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

– FPGA IO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

– FPGA Power-PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

– Power Supplies. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Page 3 – Revision 1

Introduction

Thank you for purchasing the Future Electronics - Microsemi Creative Development Board. This

guide provides the information required to easily evaluate the board.

Document Assumptions

This user’s guide assumes:

• You intend to use the Microsemi SoC Products Group Libero® System-on-Chip (SoC) suite.

• You have installed and are familiar with Microsemi SoC Products Group Libero SoC v10.0

or later.

• You are familiar with PCs and the Windows® operating system.

Additional Information

Refer to the Libero SoC Quick Start Guide to get familiar with the Microsemi SoC Products Group

FPGA development flow using Libero SoC.

Page 4 – Revision 1

Contents and System Requirements

This chapter details the contents of the Creative Development Board and lists the power supply and

software system requirements.

Box Contents

The Starter Kit includes the following:

• Future Electronics - Microsemi Creative Development Board

• The Creative Development Board Quick Start Guide

• USB Cable

Page 5 – Revision 1

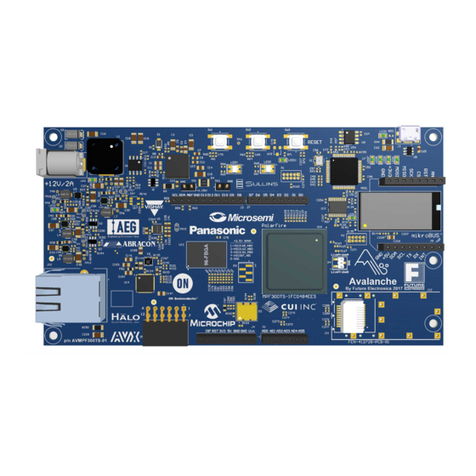

Hardware Components

This chapter describes the hardware components of the Creative Development Board.

Creative Development Board

Figure 2-1 illustrates a top-level view of the Creative Development Board. The Creative Development

Board consists of the following:

• Microsemi IGLOO2 (M2GL025) or SmartFusion2 (M2S025) FPGA

• Microsemi DC-DC LX7167

• Alliance 32M x 16-bit DDR2 synchronous DRAM (SDRAM)

• Microchip 64Mb serial flash

• Microchip six synchronous sampling 16/24-bit resolution Delta-Sigma A/D converters

• On-board FTDI USB-JTAG adaptor (FlashPro5)

• Arduino™ compatible expansion headers

• MikroBUS™ compatible expansion headers

• PMOD™ compatible expansion connector

• User buttons and LED

Detailed Board Description and Usage

The Creative Development board has various advanced features that are covered in later sections of

this chapter. This board is socketed and is populated with SmartFusion2 FPGA (M2S025) or IGLOO2

FPGA (MSGL025).

Page 6 – Revision 1

Power

Matters.

™

S

martFusion

®

2

I

GLOO

®

2

FPGA

User buttonsPMod connectors

64 Mbit Serial Flash512 Mb DDR2 SDRAM Arduino connectors

Arduino connectorsA/D Converter

Microsemi FPGA

FTDI USB-JTAGUSB

LEDs

mikroBUS

connectors

Hardware Components

Full schematics are available for download from the Future Electronics website:

http://www.futureelectronics.com/en/campaign/microsemi/Pages/CreativeDevelopmentBoard.aspx

The electronic versions of the dedicated schematics can be enlarged to a far greater degree than

shown in the printed version of this manual or even in the electronic version of this manual, hence

the interested reader is referred to the dedicated schematics to see the appropriate level of detail.

Figure 2-1 • Creative Development Board

Page 7 – Revision 1

PLL Parts/Usage

Instructions for PLL on Creative Development Board

IGLOO2 and SmartFusion2 M2GL025 devices have up to six fabric CCC (FAB_CCC) blocks at 3.3V

and a dedicated PLL associated with each CCC to provide flexible clocking to the FPGA fabric

portion of the device. The user has the freedom to use any of the eight PLLs and CCCs to generate

the fabric clocks and the internal HPMS clock from the base fabric clock (CLK_BASE). There is

also a dedicated CCC block for the HPMS (HPMS_CCC) and an associated PLL (MPLL) for HPMS

clocking and de-skewing the CLK_BASE clock. The fabric alignment clock controller (FACC), part

of the HPMS CCC, is responsible for generating various aligned clocks required by the HPMS for

correct operation of the HPMS blocks and synchronous communication with the user logic in the

FPGA fabric.

Page 8 – Revision 1

Mini USB Connector for Power, JTAG and UART Connectivity

The Mini USB Connector is used to power the BB as well as provide an embedded FlashPro5

interface to the Microsemi Libero and SoftConsole tools. More information and downloads for Libero

and SoftConsole can be found here:

http://www.microsemi.com/products/fpga-soc/design-resources/design-software

The mini USB can power the board up to 500mA. The EEPROM that is connected to the FTDI device

ss programmed so that Port A of the FTDI device is recognized as an embedded FlashPro5.

The FTDI USB to serial device provides four separate interfaces. Port A is used for a JTAG

connection to the FPGA, Port C is used as a UART interface to the FPGA. Ports B and D are

unused. When connecting a computer to the baseboard, four separate COM ports are recognized.

The third port in the group of four will be the UART port. This is important when using a console port

program such as HyperTerm or TeraTerm.

FTDI

FT4232

Mini USB

ESD

To Power Block

Port A

Port C UART

JTAG

EEPROM

Igloo2

SmartFusion2

Page 9 – Revision 1

Power Supplies

3.3V DC-DC

1.2V DC-DC

Page 10 – Revision 1

Power Supplies

1.8V DC-DC

0.9V for DDR

Table of contents

Other Future Electronics Motherboard manuals